如何读单片机的时序图

51单片机时序及延时分析

51 单片机时序及延时分析

51 单片机时序及延时分析

计算机工作时,是在统一的时钟脉冲控制下一拍一拍地进行的。

这个脉冲是由单片机控制器中的时序电路发出的。

单片机的时序就是CPU 在执行指令时所需控制信号的时间顺序,为了保证各部件间的同步工作,单片机内部电路应在唯一的时钟信号下严格地控时序进行工作,在学习51 单片机的时序之前,我们先来了解下时序相关的一些概念。

扩展阅读:单片机时序分析

既然计算机是在统一的时钟脉冲控制下工作的,那幺,它的时钟脉冲是怎幺来的呢?

要给我们的计算机CPU 提供时序,就需要相关的硬件电路,即振荡器和时钟电路。

我们学习的8051 单片机内部有一个高增益反相放大器,这个反相放大器的作用就是用于构成振荡器用的,但要形成时钟,外部还需要加一些附加电路。

8051 单片机的时钟产生有以下两种方法:

一、内部时钟方式:

利用单片机内部的振荡器,然后在引脚XTAL1(18 脚)和XTAL2(19 脚)两端接晶振,就构成了稳定的自激振荡器,其发出的脉冲直接送入内部时钟电。

LCD1602液晶显示屏幕时序图分析

LCD1602液晶显示屏幕时序图分析

这段时间里回头看看所学的单片机知识,发现一个很严重的问题看不懂时序图!研究了一上午说说自己的结果,欢迎各位拍砖和指点!

图7.2.2是1602液晶写的时序,时序图从上到下看、从左到右看。

先说说时序图的规则:

高低电平上面的线是高电平,下面的线是低电平,如果高低交叉可能会产生高电平或低电平。

电平的走向看到低电平和高电平交叉产生电平的变化,

看到红圈花的部分,竖线那里有条横线,代表着这个选用的是高电平。

还有一种情况

这种情况是高低电平一起变化,看图中横线标出了电平的变化。

现在我们了解完了规则,现在分析时序图

原图我进行了标号。

时序图从上往下看,从左往右看

1 rs 为高电平 rw 为低电平

2 载入数据db

3 始能e由低电平变为高电平

4和5 始能e由高电平转化为低电平最后数据写完。

这个就是我的理解,如果有错误或不对的地方欢迎指正。

nand flash时序图详解

怎么看时序图--nand flash的读操作详解 2013-11-16 10:25:36分类:嵌入式这篇文章不是介绍 nand flash的物理结构和关于nand flash的一些基本知识的。

你需要至少了解你手上的 nand flash的物理结构和一些诸如读写命令操作的大概印象,你至少也需要看过 s3c2440中关于nand flash控制寄存器的说明。

由于本人也没有专门学过这方面的知识,下面的介绍也是经验之谈。

这里我用的 K9F2G08-SCB0 这款nand flash 来介绍时序图的阅读。

不同的芯片操作时序可能不同,读的命令也会有一些差别。

当然其实有时候像nand flash这种 s3c2440内部集成了他的控制器的外设。

具体到读写操作的细节时序(比如 CLE/ALE的建立时间,写脉冲的宽度。

数据的建立和保持时间等),不明白前期也没有多大的问题。

因为s3c2440内部的nand flash控制器做了大部分的工作,你需要做的基本就是设置几个时间参数而已。

然后nand flash会自动进行这些细节操作。

当然如果处理器上没有集成 nand flash的控制器那么久必须要自己来写时序操作了。

所以了解最底层的时序操作总是好的但是上层一点的,比如读写操作的步骤时序(比如读操作,你要片选使能,然后发命令,然后发地址,需要的话还需发一个命令,然后需要等待操作完成,然后再读书数据)。

是必须要明白的。

这都不明白的话,怎么进行器件的操作呢也就是说 s3c2440 可以说在你设置很少的几个时间参数后,将每一个步骤中细微的操作都替你做好了。

(比如写命令,你只要写个命令到相应寄存器中,cpu内部就会协各个引脚发出适应的信号来实现写命令的操作)。

而我们所需要做的就是把这些写命令,写地址,等待操作完成。

等步骤组合起来。

从而完成一个读操作就像上面说的,虽然我们不会需要去编写每个步骤中的最细微的时序。

但是了解下。

会让你对每个操作步骤的底层细节更加明了先来看一个命令锁存的时序。

spi时序图怎么看?spi时序图详解分析

spi时序图怎么看?spi时序图详解分析https:///is/ecFhoa5/我做产品的时候,最怕就是做IIC和SPI的通信。

这两种协议时序哪怕是延时时间有误差,都有可能导致通信不上。

出现问题的时候,如果没设备也很难排查问题到底出在哪⾥。

有时候这个产品写好的时序程序,换⼀个单⽚机⽤同⼀个程序移植过去就不⾏了。

⽽且很多公司都没有设备可以调试这些协议,⼤多数时候都是完全靠蒙。

今天就拿新⼿⽐较头痛的SPI来进⾏时序图的分析和讲解,看不懂你打我!我记得第⼀次SPI通讯的时候,完全是照抄⽹络上的程序,因为芯⽚⼿册的时序图看起来太可怕了,根本看不懂。

后⾯各种模拟时序写多了,才有了经验,然后⽤经验去理解数据⼿册以及⽹络上的教程。

很多新⼿看各种数据⼿册和教程被吓到了,其实很多时候不是你的问题,⽽是数据⼿册和教程写得太学术化了。

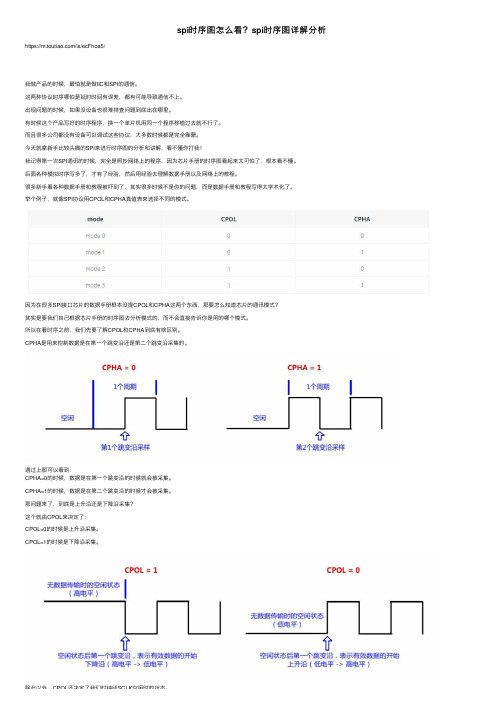

举个例⼦,就像SPI协议⽤CPOL和CPHA真值表来选择不同的模式。

因为在很多SPI接⼝芯⽚的数据⼿册根本没提CPOL和CPHA这两个东西,那要怎么知道芯⽚的通讯模式?其实是要我们⾃⼰根据芯⽚⼿册的时序图去分析模式的,⽽不会直接告诉你是⽤的哪个模式。

所以在看时序之前,我们先要了解CPOL和CPHA到底有啥区别。

CPHA是⽤来控制数据是在第⼀个跳变沿还是第⼆个跳变沿采集的。

通过上图可以看到:CPHA=0的时候,数据是在第⼀个跳变沿的时候就会被采集。

CPHA=1的时候,数据是在第⼆个跳变沿的时候才会被采集。

那问题来了,到底是上升沿还是下降沿采集?这个就由CPOL来决定了:CPOL=0的时候是上升沿采集。

CPOL=1的时候是下降沿采集。

除此以外,CPOL还决定了我们时钟线SCLK空闲时的状态。

除此以外,CPOL还决定了我们时钟线SCLK空闲时的状态。

CPOL=0的时候表⽰SCLK在空闲时为低电平。

CPOL=1的时候表⽰SCLK在空闲时为⾼电平。

Ok,明⽩了这个,我们再分析4种模式的时序图。

1. 模式0(CPOL=0 CPOL=0)CPOL = 0:时钟线空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿CPHA = 0:数据在第1个跳变沿(上升沿)采样时序图如下:2.模式1(CPOL=0 CPOL=1)CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿CPHA = 1:数据在第2个跳变沿(下降沿)采样时序图如下:3.模式2(CPOL=1 CPOL=0)CPOL = 1:空闲时是⾼电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿CPHA = 0:数据在第1个跳变沿(下降沿)采样时序图如下:4.模式3(CPOL=1 CPOL=1)CPOL = 1:空闲时是⾼电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿CPHA = 1:数据在第2个跳变沿(上升沿)采样时序图如下:这样看是不是对4种模式的区别⽐较清晰了?下⾯,我们再拿OLED的驱动芯⽚SSD1306的时序图来作为实战讲解。

时序图读写总结

时序图读写总结

一直不是很明白时序图的读写操作,上网搜了很久都找不到一份很好的资料,我故自己知道一点后就来记录一些,经常更新自己对时序图的理解吧,上网搜的时候很多人说时序图比较简单不知道是不是这样的。

因为csdn上传图片比较麻烦就不上传了,总结一下吧。

1. 时序图都是共用一个时钟信号,注意时钟信号在上下图中的对应。

2. 时序图中有叉或者上升下降的如果是数据线的话表示数据有变化。

菱形封闭的一段表示有效数据。

3. 数据需要一段时间稳定,一般在数据变化后,时钟的上升沿或者下降沿读入数据或者写入数据。

扩展阅读:如何看懂时序图?。

如何读懂时序图

/itangcleCPE/EE 421MicrocomputersWEEK #10Interpreting the Timing Diagram如何读懂时序图The 68000 Read Cycle2 Alan Clements3 Actual behavior of a D flip - f lopTiming Diagram of a Simple Flip - F lopIdealized form of the timing diagramData hold timeData setup time Max time for output to become valid after clock4 An alternative form of the timing diagramGeneral form of the timing diagramA memory access begins in clockstate S0 and ends in state S76The most important parameterof the clock is the duration of a cycle, t C YC.8Address Timing地址时序•We are interested in when the 68000 generates a new address for use in the current memory access我们感兴趣的是当6800芯片能够生成一个新的地址供当前的内存访问•The next slide shows the relationship between the new address and the state of the 68000 ’s clock下面展示的是新的地址跟6800芯片时钟的关系Alan Clements1: S0在没有初始化的时候,地址总线总是包涵新的地址。

怎么看时序图--nand flash的读操作详解

这篇文章不是介绍nand flash的物理结构和关于nand flash的一些基本知识的。

你需要至少了解你手上的nand flash的物理结构和一些诸如读写命令操作的大概印象,你至少也需要看过s3c2440中关于nand flash控制寄存器的说明。

由于本人也没有专门学过这方面的知识,下面的介绍也是经验之谈。

这里我用的K9F2G08-SCB0 这款nand flash 来介绍时序图的阅读。

不同的芯片操作时序可能不同,读的命令也会有一些差别。

当然其实有时候像nand flash这种s3c2440内部集成了他的控制器的外设。

具体到读写操作的细节时序(比如CLE/ALE的建立时间,写脉冲的宽度。

数据的建立和保持时间等),不明白前期也没有多大的问题。

因为s3c2440内部的nand flash控制器做了大部分的工作,你需要做的基本就是设置几个时间参数而已。

然后nand flash会自动进行这些细节操作。

当然如果处理器上没有集成nand flash的控制器那么久必须要自己来写时序操作了。

所以了解最底层的时序操作总是好的但是上层一点的,比如读写操作的步骤时序(比如读操作,你要片选使能,然后发命令,然后发地址,需要的话还需发一个命令,然后需要等待操作完成,然后再读书数据)。

是必须要明白的。

这都不明白的话,怎么进行器件的操作呢也就是说s3c2440 可以说在你设置很少的几个时间参数后,将每一个步骤中细微的操作都替你做好了。

(比如写命令,你只要写个命令到相应寄存器中,cpu内部就会协各个引脚发出适应的信号来实现写命令的操作)。

而我们所需要做的就是把这些写命令,写地址,等待操作完成。

等步骤组合起来。

从而完成一个读操作就像上面说的,虽然我们不会需要去编写每个步骤中的最细微的时序。

但是了解下。

会让你对每个操作步骤的底层细节更加明了先来看一个命令锁存的时序。

也就是上面说的读nand flash操作中不是有一个写命令步骤吗。

如何看懂时序图

如何看懂时序图This model paper was revised by the Standardization Office on December 10, 2020时序图,LCD1602前面总算走完了对AVR MEGA16这块单片机的一些基本的应用方式了,这时候大家对AVR的一些内部资源比如定时器,ADC,最主要的IO口的使用方式应该有了一个虽比较粗浅但是却比较形象的认识了。

这节我们来看使用单片机的另外一大主题,就是用单片机来实现芯片控制。

在前面的数码管显示一文中,就已经涉及到了用单片机来控制芯片为我们工作,CEPARK AVR开发板,为了达到增强驱动能力和节省IO口的作用,运用了移位寄存器74HC595来驱动两个四位八段数码管,是一个十分有创意的设计。

但是前面的内容重心还是集中于对AVR的IO口的控制,所以,我们从这节开始要正式逐渐深入的接触各种芯片了。

先做个引子。

单片机是一种微控制器,本身内部集成了数种资源比如CPU、内存、内部和外部总线系统,目前大部分还会具有外存。

他的主要任务是利用各种资源实现电平控制,可以以此控制与它相连的下级系统,广泛用于工业自动控制领域。

我们就从这句话出发,首先单片机是用来做控制用的,而且利用的是本身的内部资源。

但是,它的功能再强大,资源再丰富也总有一个上限,总有枯竭的一天。

所以我们常常利用单片机外接芯片来弥补或者增强单片机的功能来完成我们所需功能的电路。

比如程序存储器不足,可以外接外部存储器,比如单片机内部中断级不足,可以外接中断控制器等等。

大家可以从这个角度来理解芯片控制的意义罢。

今天我们用AVR单片机来实现对LCD1602液晶显示芯片的控制。

首先从这个名字讲起,LCD:英文全称为Liquid Crystal Display,即为液态晶体显示,也就是我们常说的液晶显示了。

(平时老说LCDLCD,可能大家也都不怎么注意过这个全称吧,呵呵,当增加词汇量了)1602则是表示这个液晶一共能显示2行数据,每一行显示16个字符。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/itangcleCPE/EE 421MicrocomputersWEEK #10Interpreting the Timing Diagram如何读懂时序图The 68000 Read Cycle2 Timing Diagram of a Simple Flip-F lopIdealized form of the timing diagramActual behavior of a D flip-f lopData hold timeData setup timeMax time for output tobecome valid after clockAlan Clements 3 General form of the timing diagramAn alternative form of the timing diagram4The Clock•A microprocessor requires a clock that provides a stream of timing pulses to control its internal operations一个微处理器需要时钟,提供一系列的计时脉冲来控制它的内部操作•A 68000 memory access takes a minimum of eight clock states numbered from clock state S0 to clock state S7一个6800芯片的储存器最小能过接收8个从S0到S7的时钟脉冲.6A memory access begins in clockstate S0 and ends in state S7Alan Clements Alan Clements 7The most important parameterof the clock is the duration of a cycle,t C YC .Alan Clements 8Address Timing地址时序•We are interested in when the 68000 generates a new address for use in the current memory access我们感兴趣的是当6800芯片能够生成一个新的地址供当前的内存访问•The next slide shows the relationship between the new address and the state of the 68000 ’s clock下面展示的是新的地址跟6800芯片时钟的关系1:S0在没有初始化的时候,地址总线总是包涵新的地址。

2: S1这个状态说明一个新的地址可以供内存访问Alan ClementsAddress Timing地址时序•Let’s look at the sequence of events that govern the timing of the address bus让我们看看事件发生的顺序,管理时间的地址总线•The “old” address is removed in state S0旧的地址已经从S0中移除•The address bus is floated for a short time, and the CPU puts out a new address in state S1地址要先存在一小段时间后,CPU才能把心的地址状态写入S1中12Alan ClementsAlan Clements Alan Clements 13The old address is removedin clock state S0 and theaddress bus floatedAlan Clements我们感兴趣的是地址生效的那个时间点。

这个时间是在S0失效后,t CLA V 秒后。

t C LA VThe designer is interested in the point atwhich the address first becomes valid. Thispoint is t C LA V seconds after the falling edgeof S0.Address and Address Strobe地址跟地址选通•We are interested in the relationship between the time at which the address is valid and the time at which the address strobe, AS*, is asserted我们感兴趣的事在地址总线能够访问时,地址选通是否有效。

•When AS* is active-low it indicates that the address is valid当AS*低电平有效时地址才是有效的。

Alan Clements上图说明:1:当地址有效的时候把AS 低电平信号.2:当地址要改变前,要把AS变成高电平•We now look at the timing of the clock, the address, and the address strobe从上面的时序图可以看出到,时钟脉冲,地址信号,片选脉冲;3者的关系。

16Alan Clements17Alan ClementsAlan Clements当AS变成低电平的时候,时钟脉冲在S2处AS* goes low in clockstate S2The Data Strobes 数据选通•The 68000 has two data strobes LDS* and UDS*. These select the lower byte or the upper byte of a word during a memory access6800芯片有两个数据选通信号LDS(低)和UDS(高).内存通过选择LDS和UDS来访问数据。

•To keep things simple, we will use a single data strobe, DS* 为了让事情看起来简单,我们只要选通DS就可以了。

(DS的高8位是UDS低8位是LDS)•The timing of DS* in a read cycle is the same as the address strobe, AS*DS的读数据跟AS读地址的时序是一样的。

Alan Clements19Alan ClementsAlan ClementsThe Data Bus 数据总线•During a read cycle the memory provides the CPU with data当读数据期间,内存给CPU提供数据•The next slide shows the data bus and the timing of the data signal .上图显示了数据总线跟数据的关系•Note that valid data does not appear on the data bus until near the end of the read cycle 注意到可访问的数据没有出现在数据总线,直到读完数据。

20The data strobe, is assertedat the same time as AS*in a read cycleAlan Clements Alan Clements21Analyzing the Timing Diagram分析时序图•We are going to redraw the timing diagram to remove clutter让我们从头到脚分析这个时序图让头脑不那么乱•We aren’t interested in the signal paths themselves, only in the relationship between the signals 我们不能单单从一条信号线来分析了,我们得从整体上来分析。

我们感兴趣的是时钟脉冲,AS/DS(地址选通/数据选通)和数据在读周期Alan Clements在地址开始有效的时候,内存就可以访问数据了。

Alan ClementsAlan ClementsCalculating the Access Time计算访问时间• We need to calculate the memory’s access time 我们必须计算内存的访问时间• By knowing the access time, we can use the appropriate memory component 通过了解访问时间,我们可以适当使用内存• Equally, if we select a given memory component, we can calculate whether its access time is adequate for a particular system 同样,如果我们选择一个特定内存组件,我们可以计算出它的访问时间是否足够用来在一个特定的系统Alan Clements 2728Alan Clements在t DICL 后,数据必须有效。

Alan Clements我们知道在地址和数据可以访问的时候之间的时间是t acc 秒Alan Clements地址数据在t CLA V 后能被访问Alan Clements在地址有效,从S0到S6结束,数据就别俘获了。

Alan ClementsAlan Clements 3334Timing Example•68000 clock 8 MHz t CYC = 125 ns •68000 CPU t CLA V = 70 ns•68000 CPU t DICL = 15 ns•What is the minimum t acc?•3 t CYC = t CLA V + t acc + t DICL•375 = 70 + t acc + 15•t acc = 290 nsAlan Clements35。