51单片机WR_RD时序

第2章 MCS-51单片机结构与时序_110905

2.3.1 运算部件及专用寄存器组

运算部件以算术逻辑单元ALU为核心,包括一个位处理器和 两个8位暂存寄存器(不对外开放),它能实现数据的算术运 算、逻辑运算、位变量处理和数据传输操作。 累加器ACC 寄存器B 专用寄存器组 程序状态字PSW 程序计数器PC 堆栈指针SP 数据指针寄存器DPTR

锁 存 器

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0 VCC VSS

地 址 总 线 (AB)

数 据 总 线 (DB)

VCC VSS

ห้องสมุดไป่ตู้(a)

(b)

MCS-51系列单片机引脚及总线结构

2.3 微 处 理 器

Program State Word

accumulator

ALU --Arithmetic and Logic Unit

图2.1 MCS-51单片机内部结构框图

1.算术逻辑单元ALU与累加器ACC、寄存器B

算术逻辑单元不仅能完成8位二进制的加、减、乘、除、加 1、减1及BCD加法的十进制调整等算术运算,还能对8位变量进 行逻辑"与"、"或"、"异或"、循环移位、求补、清零等逻辑运 算,并具有数据传输、程序转移等功能。 累加器(ACC,简称累加器A,地址E0H)为一个8位寄存器, 它是CPU中使用最频繁的寄存器。进入ALU作算术和逻辑运算的 操作数多来自于A,运算结果也常送回A保存。 寄存器B(地址F0H )是为ALU进行乘除法运算而设置的。 若不作乘除运算时,则可作为通用寄存器使用。

2.4-MCS-51单片机的工作方式和时序

7

空闲方式

• 进入: MOV PCON, #01H; IDL1 IDL 0

• 状态:CPU不工作; 各功能部件保持进入前状态;功耗小

• 退出:A、中断源发出中断请求; B、硬件复位

8

空闲方式的进入和退出

GF0——检测标志位; GF0=0执行用户程序 GF0=1空闲方式 P1.0=1电网停电

9

4、编程和校验方式

方式

RST PSEN EA /VPP

编程

1

0

VPP

禁止

1

0

╳

校验

1

0

1

保密位编程 1

0

VPP

针对8751等EPROM

ALE / PROG

0 1 1 0

P2.7 P2.6 P2.5 P2.4

1

0 ╳╳

1

0 ╳╳

0

0 ╳╳

1

1 ╳╳

10

EPROM的编程方式

方式

RST PSEN

编程

1

0Hale Waihona Puke 禁止10校验

1

0

保密位编程 1

0

EA /VPP

VPP ╳ 1 VPP

ALE / PROG

0 1 1 0

P2.7 P2.6 P2.5 P2.4

1

0 ╳╳

1

0 ╳╳

0

0 ╳╳

1

1 ╳╳

11

EPROM的校验方式

方式

RST PSEN

编程

1

0

禁止

1

0

校验

1

0

保密位编程 1

第03MCS-51系列单片机的指令系统和时序资料

西华大学电气信息学院 郑海春

13

3,逻辑操作和循环移位指令:

操作数之间的逻辑或、与、取反和异或等操作。

【特点】:多数情况下一个操作数在A中,结果也存 于A。移位指令分为左移、右移和带进位和不带进 位几种情况。逻辑类指令基本不影响PSW的内容。

西华大学电气信息学院 郑海春

14

4,控制转移类指令:

①无条件转移;

西华大学电气信息学院 郑海春

7

3.2 指令系统的概述

MCS-51共有111条指令,其长度(字节数)和 执行时间(指令周期)各不相同。

西华大学电气信息学院 郑海春

8

指令的字节数:MCS-51单片机的指令系统有: 单字节(占用1个ROM存储单元 — 1个 字节); 双字节(占用2个ROM存储单元 — 2个字节); 三字节(占用3个ROM存储单元 — 3个字节)。

④位【 特点】:按位操作。指令中所涉及到的地址皆为 “位地址” 。 这类指令基本不影响PSW的内容。

西华大学电气信息学院 郑海春

16

3.3 寻址方式

在指令的操作数位置上,用于表征、寻找操作数的 方法定义为“寻址方式”。 正确的理解、掌握寻址方式,是学习、使用指令的 关键。 在MCS-51单片机中,共使用了七种寻址方式。

第三章 MCS-51系列单片机的指令系统和时序 本章内容

掌握常用指令的格式和功能。 掌握指令执行时所包含的操作。 了解指令的长度和执行时间。

西华大学电气信息学院 郑海春

1

本章目录

3.1 MCS-51单片机的时序 3.2 指令系统的概述 3.3 寻址方式 3.4 数据传送类指令

3.5 算术操作类指令

ROM

ROM

ROM

OP

51单片机时序及接口扩展

特点:

片内、片外分别编址;

片内地址:00和~FFH,

片外地址:0000H~FFFFH。

片外RAM用数据指针DPTR寻址,由管脚RD/WR控制

RAM的读出/写入;

片内RAM分为四个区(工作寄存器区、位寻址区、数据

缓冲区和特殊功能寄存器区)。

《测量与机电控制》核心课程

2.1 存储器配置及特点

工作寄存器区:

《测量与机电控制》核心课程

2.1 存储器配置及特点

状态字(PSW)

CY AC F0 RS1 RS0 OV

P

D7

D0

(1)进位标志位Cy(Carry) 用于加减运算时,保存最高位进 位、借位状态。

(2)辅助进位位AC(Auxiliary Carry)

例:78H+97H

有进位 CY=1

0111 1000 + 1001 0111 1 0000 1111

专门用来存放堆栈的栈顶地址。入栈能自动加1,出栈则自动减

1。

系统复位后初始化的值为07H,则堆栈由08H单元开始,占

用了工作寄存器空间,可以改变SP的值。

《测量与机电控制》核心课程

2.1 存储器配置及特点

③ 与端口相关的(7个)

(1)I/O口P0、P1、P2、P3 (2)串行数据缓冲器SBUF (Serial Date Buffer) (3)串行控制寄存器SCON (Serial Control Register) (4)电源控制寄存器PCON (Power Control Register)

例:某运算结果是79H(01111001),P=1。 《测量与机电控制》核心课程

2.1 存储器配置及特点

②与指针相关的(2个)

单片机:51单片机的延时及时序分析

计算机工作时,是在统一的时钟脉冲控制下一拍一拍地进行的。

这个脉冲是由单片机控制器中的时序电路发出的。

单片机的时序就是CPU在执行指令时所需控制信号的时间顺序,为了保证各部件间的同步工作,单片机内部电路应在唯一的时钟信号下严格地控时序进行工作,在学习51单片机的时序之前,我们先来了解下时序相关的一些概念。

既然计算机是在统一的时钟脉冲控制下工作的,那么,它的时钟脉冲是怎么来的呢?要给我们的计算机CPU提供时序,就需要相关的硬件电路,即振荡器和时钟电路。

我们学习的8051单片机内部有一个高增益反相放大器,这个反相放大器的作用就是用于构成振荡器用的,但要形成时钟,外部还需要加一些附加电路。

8051单片机的时钟产生有以下两种方法:1. 内部时钟方式:利用单片机内部的振荡器,然后在引脚XTAL1(18脚)和XTAL2(19脚)两端接晶振,就构成了稳定的自激振荡器,其发出的脉冲直接送入内部时钟电路,外接晶振时,晶振两端的电容一般选择为30PF左右;这两个电容对频率有微调的作用,晶振的频率范围可在1.2MHz-12MHz之间选择。

为了减少寄生电容,更好地保证振荡器稳定、可靠地工作,振荡器和电容应尽可能安装得与单片机芯片靠近。

2. 外部时钟方式:此方式是利用外部振荡脉冲接入XTAL1或XTAL2。

HMOS和CHMOS单片机外时钟信号接入方式不同,HMOS型单片机(例如8051)外时钟信号由XTAL2端脚注入后直接送至内部时钟电路,输入端XTAL1应接地。

由于XTAL2端的逻辑电平不是TTL的,故建议外接一个上接电阻。

对于CHMOS型的单片机(例如80C51),因内部时钟发生器的信号取自反相器的输入端,故采用外部时钟源时,接线方式为外时钟信号接到XTAL1而XTAL2悬空。

如下图外接时钟信号通过一个二分频的触发器而成为内部时钟信号,要求高、低电平的持续时间都大于20ns,一般为频率低于12MHz的方波。

片内时钟发生器就是上述的二分频触发器,它向芯片提供了一个2节拍的时钟信号。

MCS51单片机答案

1、MCS-51单片机的时钟周期与振荡周期之间有什么关系?一个机器周期的时序如何划分?答:时钟周期是单片机最基本的时间单位。

机器周期则是完成某一个规定操作所需的时间。

一个机器周期为6个时钟周期,共12个振荡周期性,依次表示为S1P1、S1P2、……S6P1、S6P2。

2、MCS-51内部四个并行I/O口各有什么异同?作用是什么?答:MCS-51单片机共有四个8位双向并行的I/O端口,每个端口都包括一个锁存器、一个输出驱动器和一个输入缓冲器。

但这四个端口的功能不全相同,P0口既可作一般I/O端口使用,又可作地址/数据总线使用;P1口是一个准双向并行口,作通用并行I/O口使用;P2口除了可作为通用I/O使用外,还可在CPU访问外部存储器时作高八位地址线使用;P3口是一个多功能口除具有准双向I/O功能外,还具有第二功能。

3、简述MCS-51单片机的中断响应过程。

答:CPU在每个机器周期的S5P2期间顺序采样每个中断源,在下一个机器周期S6区间按优先级顺序查询中断标志,如查询到某个中断定标志为1,将在接下来的机器周期S1期间按优先级进行中断处理,中断系统通过硬件自动将相应的中断矢量地址装入 PC,以便进入相应的中断服务程序。

一旦响应中断,CPU首先置位相应的中断“优先级触发器”,然后由硬件执行一条长调用指令,把当前的PC值压入堆栈,以保护断点,再将相应的中断服务的入口地址送入PC,于是CPU接着从中断服务程序的入口处开始执行。

对于有些中断源,CPU在响应中断后会自动清除中断标志。

5、MCS-51单片机内部包括哪些主要逻辑功能部件?答:MCS-51单片机主要由下列部件组成: 1个8位CPU;1个片内振荡器及时钟电路;4KB ROM程序存储器,256BRAM;21个特殊功能寄存器;2个16位定时/计数器;4个8位并行I/O口及1个可编程全双工串行接口;可寻址64KB的外部程序存储器空间;可寻址64KB的外部数据存储器空间;5个中断源、两个优先级中断嵌套中断结构。

51单片机的延时及时序分析

要给我们的计算机CPU提供时序,就需要相关的硬件电路,即振荡器和时钟电路。我们学习的8051单片机内部有一个高增益反相放大器,这个反相放大器的作用就是用于构成振荡器用的,但要形成时钟,外部还需要加一些附加电路。8051单片机的时钟产生有以下两种方法:

51单片机的延时及时序分析

计算机工作时,是在统一的时钟脉冲控制下一拍一拍地进行的。这个脉冲是由单片机控制器中的时序电路发出的。单片机的时序就是CPU在执行指令时所需控制信号的时间顺序,为了保证各部件间的同步工作,单片机内部电路应在唯一的时钟信号下严格地控时序进行工作,在学习51单片机的时序之前,我们先来了解下时序相关的一些概念。

在8051单片机中把一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示)。请大家参考后面的时序图。

机器周期

在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段,每一阶段完成一项工作。例如,取指令、存储器读、存储器写等,这每一项工作称为一个基本操作。完成一个基本操作所需要的时间称为机器周期。一般情况下,一个机器周期由若干个S周期(状态周期)组成。8051系列单片机的一个机器周期同6个S周期(状态周期)组成。前面已说过一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示),8051单片机的机器周期由6个状态周期组成,也就是说一个机器周期=6个状态周期=12个时钟周期。参见后面的时序图。

二、外部时钟方式:

此方式是利用外部振荡脉冲接入XTAL1或XTAL2。HMOS和CHMOS单片机外时钟信号接入方式不同,HMOS型单片机(例如8051)外时钟信号由XTAL2端脚注入后直接送至内部时钟电路,输入端XTAL1应接地。由于XTAL2端的逻辑电平不是TTL的,故建议外接一个上接电阻。对于CHMOS型的单片机(例如80C51),因内部时钟发生器的信号取自反相器的输入端,故采用外部时钟源时,接线方式为外时钟信号接到XTAL1而XTAL2悬空。如下图

51LPC系列OTP单片机烧写时序

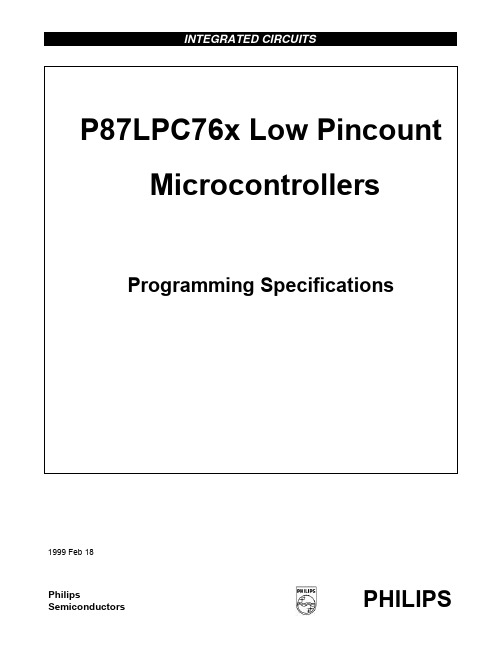

P87LPC76x Low Pincount MicrocontrollersProgramming Specifications1999 Feb 18Philips1. PINOUTFigure 1: 20, 16, 8 pins DIP pinoutThe 20 pin SO package outlines SOT163-1 is attached at the end of this document.123RST / V PP / P1.54V SS567891020191817P0.4 / CIN1A / AD1 / PDA16P0.5 / CMPREF / AD2 / PCL 15V DD 1413121112RST / V PP / P1.53V SS45678161514P0.4 / CIN1A / AD1 / PDA 13P0.5 / CMPREF / AD2 / PCL 12V DD 11109RST / V PP / P1.51V SS2348P0.4 / CIN1A / AD1 / PDA 7P0.5 / CMPREF / AD2 / PCL 6V DD5Figure 2: 44 pins PLCC bondout chipTable 1: 44 PLCC pinout (programming related pins are in bold text)PLCC44717392918286401P IN F UNCTION1VSS234 567 8P1.5/RST/VPP 9 10VSS 1112 13141516171819202122P IN F UNCTION44 43 4241403938P0.4/CIN1A/AD1/PDA 37P0.5/CMPREF/AD2/PCL3635 34333231VDD3029282726252423VDD2. PIN DESCRIPTIONSTable 2: Programming pins in different packages3. GETTING INTO THE SERIAL PROGRAMMING MODE1. Disconnect pins PCL and PDA.2. Connect VDD; the part does not support “hot insertion” into the programming socket3. Wait 20 uSec (Min) and raise V PP to 10.75V +/- 0.25V; V PP rise time is 1uSec to 100 uSec.At this point the part is in the programming mode.4. Wait t INIT = 60 uSec (Min) before beginning the serial communication to the part.5. Get out of the programming mode by connecting V PP = 0V; V PP fall time is 1uSec to 100 uSec.6. Disconnect VDD before removing the part from the socket.The programming mode enables the internal RC oscillator.During the programming mode PDA and PCL pins are Schmitt trigger inputs.Figure 3: Getting into the programming modeMNEMONIC44 pins package PIN NO.20 pins packagePIN NO.16 pins packagePIN NO.8 pins packagePIN NO.TYPE NAME AND FUNCTION VSS 10, 1542P Ground: 0V reference.VDD 23, 3115126P Power Supply: 5V +/-.5VPCL 3716137I Serial clock input for EPROM programming communication.PDA 3817148I/O Serial data I/O for EPROM programming communication.VPP8431PV PP = 10.75V +/- 0.25V I PP = 30mA during programming.PDA PCLVDDVPPtVDD = 4.5V to 5.5V; V PP = 10.75V +/- 0.25V I PP = 30mA during programming; T amb = 10°C to +40°C Table 3: Programming mode timings4. PROGRAMMING MODEThe programming commands are sent by the programmer through the PCL and PDA lines. Each programming command is one byte shifted into the part by 8 clocks.The serial interface is identical to the 51’s 8-bit serial UART mode 0; LSB is the first bit in the serial byte.PCL pin is the clock input from the programmer.PDA pin is the data I/O. Data is enabled on the falling edge of PCL, and is clocked on the rising edge of PCL.Data output from the part is disabled after the rising edge of PCL for the last bit in a data byte.Figure 4: Writing programming commands by the programmerTable 4: Programming commandsSYMBOL FIGUREPARAMETERLIMITS UNIT MIN MAX t VDDVPP V DD HIGH to V PP rising edge20us t VPPLH V PP rise time 1100us t VPPHL V PP fall time1100us t INITV PP = 10.75V to the beginning of serial communication60usNAME OPCODE FUNCTIONNOP00H Not usedLOAD_DATA 02H Load address counter with the next data byteRD_DATA 04H Read data byte addressed by the program counterINC_ADDR 06H Increment address counterLD_ADRR_LO 08H Load 8 LOW address bits into programming counter LD_ADRR_HI 0AH Load 8 HIGH address bits into programming counterSTRT_PRGM 0CH Start programming a data byte; always followed by the Stopt programming command STP_PRGM 0EHStop programming a data byte; always follows the Start programming command.PDALSB bitMSB bitPCLNotes:Wait 2 uSec between any two programming commands (except “Start Programming” to “Stop Programming”)Wait 250uSec between “Start Programming” and “Stop Programming” commands.Example of a sequence of programming commandsTable 5: Sequence of programming commandsFigure 5: Reading data by the programmerLD_ADDR_LO Wait 2uSec XX DATA Wait 2uSec LD_ADDR_HI Wait 2uSec XX DATA Wait 2uSec LOAD_DATA Wait 2uSec XX DATA Wait 2uSec READ_DATA Wait 2uSec XX DATA Wait 2uSec INC_ADDR Wait 2uSec LOAD_DATA Wait 2uSec XX DATA Wait 2uSec STRT_PRGM Wait 250uSec STP_PRGMWait 2uSecSYMBOL FIGUREPARAMETERLIMITS UNIT MINMAX t SC 5Serial clock cycle time0.21000us t WAIT 5Wait between two serial bytes2us t WAITP 5Wait after a “Start Programming” command250us t SDSU 4Serial data setup time to the rising edge of the serial clock 40ns t SDH 5Serial data hold time after the rising edge of the serial clock 10ns t SCLDV 5Serial clock LOW to valid data of the first data bit in a byte 40ns t SCHZ5Serial clock HIGH to data Hi-Z at the last data bit in a byte40nsPDALSBMSB PCLTable 6: Programming commands timingAddress Memory Definition0000H to 0FFFH User’s code; program/read by the programmerFC30H Company signature 15H - Read only by programmerFC31H Part’s signature DDH - Read only by the programmerFC60H Derivative’s signature 00H - Read only by the programmerFCE0H to FCFFH32 bytes used as user’s parameters; program/read by the programmerFD00H User Configuration Reg. #1 (UCFG1) program/read by the programmerFD01H User Configuration Reg. #2 (UCFG2) program/read by the programmerTable 7: EPROM MappingThe programmer programs the user’s code at address 0 to FFFH and configuration registers located at address FCE0H to FD01H. These configuration registers configure the chip’s modes of operation.5. USER CONFIGURATION REG. #1 (UCFG1) AT ADDRESS FD00H76543210 Programmed bits WDTE RPD PRHI BO2.5CLKR FOSC2FOSC1FOSC0Erased State FFHTable 8: User Configuration Register #1WDTE: WatchDog Timer Enable;1 = (Erased) WDT enabled0 = (Programmed) WDT disabledRPD: Reset Pin Disable;1(Erased) External Reset pin disabled (The internal power-on reset is enabled)0 (Programmed) External Reset pin enabledPRHI: Port Reset High;1 = Enable ports to high during and after RESET0 = Enable ports to low during and after RESETBO2.5: Brown out at 2.5V;1 = Enable brown out at 2.5V0 = Enable brown out at 3.8VCLKR: CLock Rate select;1 = Enable divide by 1 of clock (6 clocks per machine cycle)0 = Enable divide by 2 of clock (12 clocks per machine cycle)FOSC2 - FOSC0: Oscillator control bits;FOSC2FOSC1FOSC0External clock input at pin X1111Internal RC clock; 6MHz +/- 25%01132KHz to 100KHz external Crystal/Resonator010100KHz to 4 MHz external Crystal/Resonator0014 MHz to 20 MHz external Crystal/Resonator000Table 9: FOSC2-FOSC0 bit function6. USER CONFIGURATION REG. #2 (UCFG2 AT ADDRESS FD01H)76543210 Programmed bits SEC2SEC1Erased State FFHTable 10: User Configuration Register #2SEC2-SEC1: SECurity bits 2 & 1;11 = Security bits unprogrammed; Programming and Verify allowed.10 = Security bit 2 unprogrammed; 1 programmed; Programming disabled, Verify enabled.00 = Both bits programmed; Programming and Verify disabled7. 32 REGISTERS OF USER’S PARAMETERS (FCE0H TO FCFFH)The 32 registers of user’s parameters are programmed as code located at address FCE0H to FCFFH.The content of the 32 parameter registers and the two configuration registers are defined by the HEX file at addresses:FCE0H to FCFFH32 bytes used as user’s parameters; program/read by the programmerFD00H User Configuration Reg. #1 (UCFG1) program/read by the programmerFD01H User Configuration Reg. #2 (UCFG2) program/read by the programmerThe user should be able to display, edit, program and verify the two configuration registers and the user’s 32 bytes located at address FCE0H to FCFFH.Philips SemiconductorsPackage outlinesSO20:plastic small outline package; 20 leads; body width 7.5 mm SOT163-1。