等间距采样的高速数据采集系统设计

等间距采样的高速数据采集系统设计

( ns r I tum e t inc nd Dyna i e s r m e i s r fEduc ton K e b r t r n s Sce e a m c M a u e ntM nity o a i y Ia o a o y,

N o t nie st r h U v r iy ofChi na,T ay n 0 051,Chi ) i ua 30 na Ab tac sr t:Theba i i cpl ft s ig c b ef uls wih na r w s qudit nc a pi g i s rb d. Pu s ha a t rs is a d pr scpr i e o e tn a l a t t r o pule e i s a e s m ln sde c ie n le c r ce itc n o— c s ig r q r m e s a e a a y e T h igl ie r p a e o s e a a a q iiin s tm sd sgn d wih FPGA d SP43 e sn e uie nt r n l z d. e sn e ln e e t d l w— pe d d t c u sto ys e i e i e t an M 0FI 49

基于等效时间采样的高速数据采集技术

基 于等 效 时 间采 样 的高 速 数 据 采 集 技 术

陈 小 桥 , 爱 荣 , 长 军 刘 亓

( 汉 大 学 电子 信 息 学 院 , 汉 武 武 407 ) 3 0 2 摘 要 : 用 等效 时 间 采 样 技 术 用 低 速 的 A 转 换 器 可 以 实 现 对 宽 频 带 模 拟 信 号 的 高 速 数 利 D

H i h s e dat quiii s t m ba e g pe d a ac ston yse s d

o n e qui l nt tm e a p i va e i s m lng C e a qa , i A rn , iC a  ̄u h n Xio io Lu i g Q h n n o

维普资讯

总第 3 9卷 第 4 0期 4

20 0 2年 第 8期

电 测 与 仪 表

E e tia Me s rme t & I sr me tto lere l a ue n n tu nain

V 19 N . 0 0 . o4 3 4

Au .2 02 g 0

领 域 ,经 常 涉 及 对 宽 带 模 拟 信 号 进 行 数 据 采 集 和 存

储, 以便 计 算 机 进 一 步 进 行 数 据 处理 。 了对 高 速 模 为

成 的低 频 信 号 ,且 U 3的 周 期 为 U1周 期 的整 数 倍 。

被 测 高 频 重 复 信 号 U1 取 样 脉 冲 出现 的 时 刻 被 采 在

据 采 集 , 仅 降 低 了 系统 实 现 的 难 度 , 节 约 了 系统 成 本 。 文 主 要 着 重 论 述 了基 于 等 效 不 还 本

时 间 采 样 的高 速 数据 采 集 技 术 的基 本 原 理 以 及 整 体 实 现方 案 整 个方案 实 现 的 关 键 于 步 进 采 样 脉 冲 信 号 的 提 取 , 文 对 此 进 行 了详 细 沦述 本 , 关 键 词 : 效 时 间 采样 ; 速 数 据 采 集 ; 进 采 样 脉 冲 等 高 步 中 图分 类 号 : M9 5 T 3 文 献标 识 码 : A 文 章 编 号 :0 — 3 0(0 2 0 一 0 3 0 101 1 9 2 0 ) 8 O 2 — 4

高速数据采集系统设计

高速数据采集系统设计作者:张宁来源:《卫星电视与宽带多媒体》2009年第10期多通道高速数据采集技术是宽带模拟信号数据采集的关键技术,在现代通信、仪器仪表等领域中得到广泛应用。

本文通过多通道高速采样器AD9042设计实现说明接口电路的工作原理、设计思想和实现方案。

本系统采用多路合成方案实现多路低引言在现代电子测量、仪器仪表、通信等领域,经常涉及对宽带信号进行数据采集和存储。

实际数字采样系统中存在数字转换器引起的量化噪声、采样保持器带来的非线性失真、带宽限制和孔径抖动误差、数据在系统各部分间传送过程中可能引入的噪声干扰以及由电路布局和系统结构的原因耦合的噪声干扰等多种因素会造成采样系统性能下降,这种因素在高速采样系统中影响尤其突出。

因此,高速宽带采样系统设计显得尤其重要。

影响高速采样系统性能的主要因素1 前端电路的构成合理的前端电路构成,是系统实现中最为关键的一步。

在高速数据采集系统的设计中,最重要的技术指标是系统的通过速率。

这一指标与预采样滤波器的建立和恢复时间,模拟多路开关的转换时间,驱动放大器的响应时间,采样保持电路的捕捉时间,模数转换器的转换时间等都有关系,即系统各部件的性能参数限制了系统的性能指标。

实际上高速数据采集的实现总会受到器件性能的制约,而且对于不同的系统结构,起决定性作用的部件又各不相同,所以选择合适的结构在系统设计中显得尤为重要。

在高速数据采集系统中,常用的结构有单通道采集结构和多通道并行采集结构两种。

在前端电路设计时应注意如下几点:(1)前置放大器在输入信号的带宽范围内应该有足够大的增益和足够短的稳定时间。

一般是选择具有大的驱动能力和快的稳定时间的运放。

(2)降低输出瞬态的影响。

一个重要方法是保证工作频带内放大器能保持一个较低的输出阻抗。

(3)放大器带宽要保证其稳定时间跟得上ADC的速度。

在接近单位增益的交叉点的频率时,放大器闭环增益会降低,导致输出阻抗增大。

因此,在设计前置驱动放大器时,决不能忽视带宽的因素,所以在选择放大器时要有足够大的带宽储备量。

基于AD9233高速数据采样系统的设计

信 息 技 术34科技资讯 SC I EN C E & TE C HN O LO G Y I NF O R MA T IO N雷达通过向特定方向辐射电磁波,再从接收的信号中将目标的回波信号检测出来,从而判断目标的角度,距离,形状等信息。

雷达目标的检测一般是在十分复杂的电磁环境下进行的,接收信号不仅含有目标回波,还含有大量的干扰噪声。

随着数字信号处理理论的不断发展,雷达信号数字接收机技术日益成为雷达技术发展的重点。

雷达的数字接收机主要包含数字采样部分和信号处理部分。

本文主要对雷达信号的高速采样电路进行研究设计。

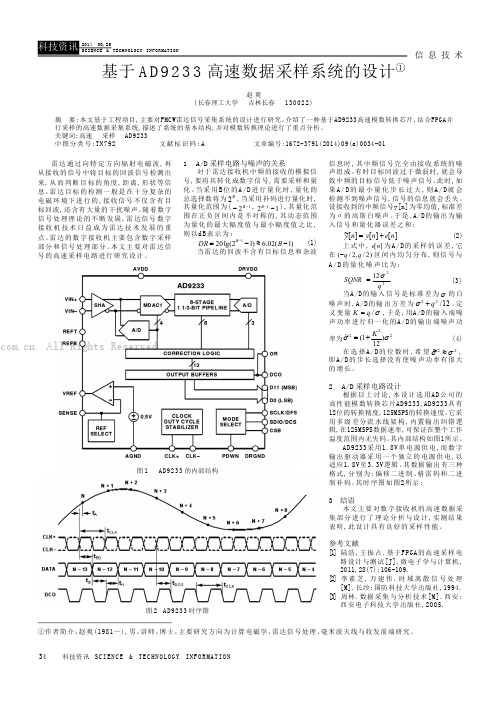

1 A/D 采样电路与噪声的关系对于雷达接收机中频的接收的模拟信号,要将其转化成数字信号,需要采样和量化。

当采用B 位的A /D 进行量化时,量化的总选择数将为B 2,当采用补码进行量化时,其量化范围为( 12 B , 121 B ),其量化范围在正负区间内是不对称的,其动态范围为量化的最大幅度值与最小幅度值之比,则以d B 表示为:)1(02.6)12lg(201 B DR B (1)当雷达的回波不含有目标信息和杂波①作者简介:赵爽(1981—),男,讲师,博士,主要研究方向为计算电磁学、雷达信号处理、毫米波天线与收发前端研究。

基于A D 9233高速数据采样系统的设计①赵爽(长春理工大学 吉林长春 130022)摘 要:本文基于工程项目,主要对FMCW雷达信号采集系统的设计进行研究。

介绍了一种基于AD9233高速模数转换芯片,结合FPGA并行采样的高速数据采集系统,描述了系统的基本结构,并对模数转换理论进行了重点分析。

关键词:高速 采样 AD9233中图分类号:TN 792文献标识码:A 文章编号:1672-3791(2014)09(a)0034-01信息时,其中频信号完全由接收系统的噪声组成。

有时目标回波过于微弱时,就会导致中频的目标信号低于噪声信号。

此时,如果A /D 的最小量化步长过大,则A /D 就会检测不到噪声信号,信号的信息就会丢失。

高速数据采集系统设计说明书

基于FPGA和SoC单片机的高速数据采集系统设计一.选题背景及意义随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分。

高速数据采集系统在自动测试、生产控制、通信、信号处理等领域占有极其重要的地位。

随着SoC单片机的快速发展,现在已经可以将采集多路模拟信号的A/D转换子系统和CPU核集成在一片芯片上,使整个数据采集系统几乎可以单芯片实现,从而使数据采集系统体积小,性价比高。

FPGA为实现高速数据采集提供了一种理想的实现途径。

利用FPGA高速性能和本身集成的几万个逻辑门和嵌入式存储器块,把数据采集系统中的数据缓存和控制电路全部集成在一片FPGA芯片中,大大减小了系统体积,提高了灵活性。

FPGA 还具有系统编程功能以及功能强大的EDA软件支持,使得系统具有升级容易、开发周期短等优点。

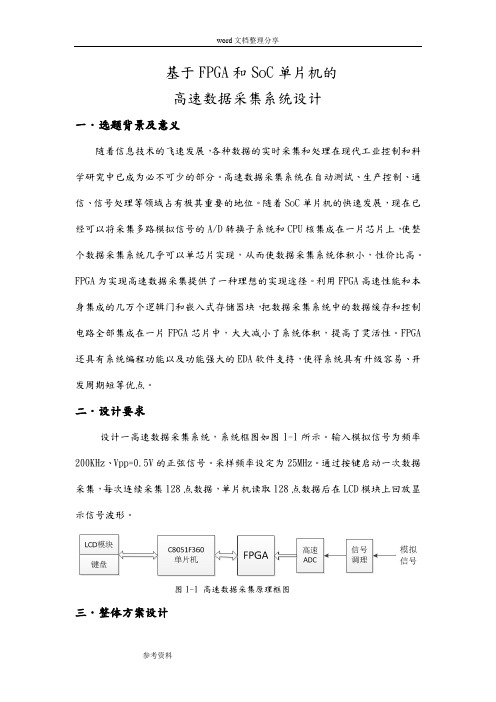

二.设计要求设计一高速数据采集系统,系统框图如图1-1所示。

输入模拟信号为频率200KHz、Vpp=0.5V的正弦信号。

采样频率设定为25MHz。

通过按键启动一次数据采集,每次连续采集128点数据,单片机读取128点数据后在LCD模块上回放显示信号波形。

图1-1 高速数据采集原理框图三.整体方案设计高速数据采集系统采用如图3-1的设计方案。

高速数据采集系统由单片机最小系统、FPGA最小系统和模拟量输入通道三部分组成。

输入正弦信号经过调理电路后送高速A/D转换器,高速A/D转换器以25MHz的频率采样模拟信号,输出的数字量依次存入FPGA内部的FIFO存储器中,并将128字节数据在LCD模块回放显示。

图3-1 高速数据采集系统设计方案四.硬件电路设计1.模拟量输入通道的设计模拟量输入通道由高速A/D转换器和信号调理电路组成。

信号调理电路将模拟信号放大、滤波、直流电平位移,以满足A/D转换器对模拟输入信号的要求。

2.高速A/D转换电路设计五.FPGA模块设计本设计的数据缓冲电路采用FIFO存储器。

高精度数据采集系统的设计及性能分析

高精度数据采集系统的设计及性能分析现代工业生产过程中往往需要涉及大量的监测和控制,而高精度数据采集系统的设计和性能分析就是为了满足这种需求而诞生的。

本文将介绍高精度数据采集系统的设计和性能分析的相关技术及应用,同时分析这些技术的应用场景和性能优劣,希望能够对读者有所帮助。

一、高精度数据采集系统的组成高精度数据采集系统是由多个部件组成的复杂系统,其中主要包括传感器、信号调理器、数据采集卡、数据处理软件等。

下面详细介绍这些部件的作用及原理:1. 传感器传感器是高精度数据采集系统中最核心的组成部分之一。

它的作用是将测量对象的物理量转换为电信号输出,常见的传感器包括温度传感器、压力传感器、角度传感器、力传感器等。

不同类型的传感器在测量的物理量和范围上存在差异,同时也有不同的转换方式和输出形式。

2. 信号调理器信号调理器是传感器信号处理的核心,主要负责将传感器输出的信号进行放大、滤波、线性化等处理,使其适合于数据采集卡进行数字化转换。

信号调理器的设计将直接影响系统的稳定性和精度。

3. 数据采集卡数据采集卡是高精度数据采集系统中另一个重要的组成部分,它起到将模拟信号转换成数字信号的作用。

数据采集卡的数字化转换精度和采样率将直接影响采集系统的精度。

4. 数据处理软件数据处理软件是高精度数据采集系统中最后一道关键工序的组成部分。

它的作用是将数据从数据采集卡中读取,并将其经过校准、滤波、标定、控制等算法处理,最终输出给用户需要的数据。

数据处理软件应当具有友好的用户界面、高效的运算能力和稳定的运行性能。

二、高精度数据采集系统的应用场景高精度数据采集系统的应用场景十分广泛,主要包括以下几个领域:1. 工业控制众所周知,现代工厂生产过程需要各种各样的传感器和数据采集设备,以保证产品质量和生产效率。

高精度数据采集系统可以应用于无污染的检测、高速电机控制、发电温度观测、高分辨率精细控制等技术领域。

2. 航空雷达航空雷达数据采集系统需要在高速行动的飞机上进行复杂的数据采集和传输,并要求精度高、稳定性好、机动性强、重量轻等特点。

《2024年高速无线数据采集终端的设计与优化》范文

纪实故事-老舍母亲:把吃亏视做理所当然老舍的母亲是一位旧中国典型的劳动妇女,勤劳持家,自立自强。

老舍热情、好客,待人真挚、诚恳,这些性格与母亲的影响有关。

老舍的母亲会给婴儿洗三——穷朋友们可以因此少花一笔“请姥姥”钱。

她会刮痧,她会给孩子们剃头,她会给少妇们绞脸……凡是她能做的,都有求必应,谁家有事要帮忙,她总是跑在最前头。

有客人来,无论手头再怎么窘迫,老舍的母亲也要设法弄一点东西去款待。

舅父与表哥们来做客时,往往是自己掏钱买酒、买肉食,这使她脸上羞得飞红。

可是殷勤地给他们温酒做面,又给她一些喜悦。

遇上亲友家中红白喜事,母亲必把大褂洗得干干净净,亲自去贺吊,一份礼也许只是两吊小钱。

老舍继承了他母亲的性格,出了名的好客,离了朋友们就活不下去。

在重庆的时候,老舍的生活相当清贫,但是老友相逢,卖了大褂,也要上一趟小馆盛情款待。

晚年的老舍更加看重友情。

逢年过节,或是小院里百花盛开的时节,老舍的家,就变成了欢乐之海,赏花赏画,品茗品酒。

主人与宾客们全都痛快极了。

有时到了欢畅之时,赵树理会扯着嗓子“吼”他拿手的上党梆子,曹禺则酩酊大醉后滑到了桌子底下……也有的时候,老舍的小院里会出现一些奇特的客人。

他们大都是年逾花甲的老人,有的还领着个小孩。

一见到老舍先生,他们就照旗人的规矩,一边作揖行礼,一边还大声吆喝着:“给大哥请安!”老舍总是连忙把他们扶起:“别……别这样!现如今不兴这一套了。

快坐下,咱哥俩好好聊聊。

”事后,老舍向旁观的朋友解释,“这些都是几十年的老朋友了。

当年有给行商当保镖的,有在天桥卖艺的,也有当过‘臭脚巡’(旧社会的巡警)的。

你读过我的《我这一辈子》《断魂枪》《方珍珠》吗?他们就是作品中的模特儿啊!”老舍的姑母常在家闹脾气,在鸡蛋里找骨头,是家中的阎王。

直到老舍入了中学,她才死去。

可是老舍没有看见母亲反抗过。

“没受过婆婆的气,还不受大姑子的吗?命当如此!”母亲在非解释一下不足以平服别人的时候,才这样说,老舍感叹:母亲活到老,穷到老,辛苦到老,最会吃亏。

高速数据采集系统的设计

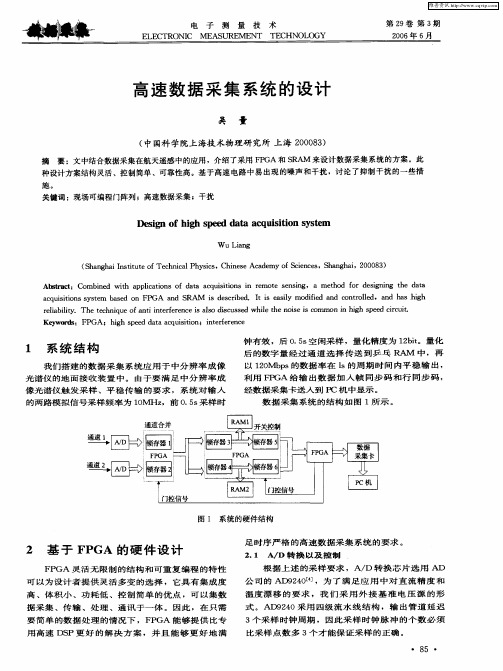

钟 有 效 ,后 0 5 空 闲 采 样 ,量 化 精 度 为 1 bt .s 2 i。量 化 后 的数 字 量 经 过 通 道 选 择 传 送 到 乒 乓 RAM 中 ,再 以 10 p 2 Mb s的 数 据 率 在 I 周 期 时 间 内 平 稳 输 出 , s的

利 用 F GA 给 输 出 数 据 加 入 帧 同 步 码 和 行 同 步 码 , P 经数 据采集 卡送入到 P C机 中 显 示 。 数 据 采 集 系 统 的 结 构 如 图 1所 示 。

摘 要 :文 中结合数据采集在航 天遥感 中的应用 ,介 绍了采用 F GA和 S A 来 设计数 据采集 系统 的方 案。此 P RM 种 设计 方案结构灵活 、控 制简单 、可靠性高 。基 于高速 电路 中易 出现 的噪声和 干扰 ,讨 论 了抑 制干扰 的一 些措

施。

关键词 :现场 可编程 门阵列 ;高速数据 采集 ;干扰

吴

量 :高速数 据采 集 系统 的设 计

由 于 通 道 数 只 有 2路 , 因 此 直 接 取 其 数 字 量 的

第3 期

高 1 b t 人 FP 2 i送 GA 中 ,利 用 FP GA 内部 的 资 源 生 成 锁存器 进 行 两 路 数 据 的合 并 ,这 样 提 高 了集 成 度 ,减 少 了 外 围 的 器 件 数 量 。两 路 锁 存 器 的 时 钟 均

— ~[ — 匝 ) —l = D

i —I/ 1 — — 墅 —◆ ^u —/ —

图 l 系统 的硬件结 构

2 基 于 F GA 的 硬 件 设 计 P

F PGA 灵 活 无 限 制 的 结 构 和 可 重 复 编 程 的 特 性 可 以 为 设 计 者 提 供 灵 活 多 变 的 选 择 ,它 具 有 集 成 度 高 、体 积 小 、 功 耗 低 、 控 制 简 单 的优 点 ,可 以集 数 据 采 集 、传 输 、处 理 、 通 讯 于 一 体 。 因 此 ,在 只 需 要 简 单 的数 据 处 理 的情 况 下 , F PGA 能 够 提 供 比专

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

等间距采样的高速数据采集系统设计郝亮,孟立凡,刘灿,高建中(中北大学仪器科学与动态测试教育部重点实验室,太原030051)摘要:简单介绍通过对窄脉冲等间距采样来测试电缆故障的基本原理,分析其脉冲的特点和处理要求;采用F PGA和MSP430F149作为主控芯片,设计了单路多次低速数据采集系统;利用Quartus II软件编写主控程序,并在Modelsim下进行仿真验证。

实验结果表明,该系统方案切实可行,可有效解决电缆故障测距过程中的高精度数据采集问题。

关键词:等间距采样;数据采集;MSP430F149;F PGA中图分类号:TN98文献标识码:BH igh2spe ed Data Acquisition System Based on Equidistance SamplingHao Liang,Meng Lifan,Liu Can,Gao Jianzhong(Inst ruments Science and Dynamic Measurement Ministry of Education Key Laboratory,North University of China,T aiyuan030051,China)A bstract:T he basic principle of testing cable faults wit h narrow2pulse equidistance sampling is described.Pulse characteristics and pro2 cessing requirements are analyzed.The single2line repeated low2speed dat a acquisition system is designed with FPGA and MSP430F149 as main control chips.Main control procedures are programmed in Quartus II and simulated in Modelsim.Experimental result shows that t he system is practical,and the problem of high2precision data acquisition in the process of cable fault location is resolved effectively. K ey words:equidist ance sampling;data acquisit ion;MSP430F149;FPGA引言电缆故障是通信行业中的常见故障,而电缆测距是排除故障的前提条件。

准确的电缆测距可以缩短发现故障点的时间,利于快速排除故障,减少损失。

窄脉冲时域反射仪利用时域反射技术来测定电缆断点位置,可以同时检测出同轴传输系统中多个不连续点的位置、性质和大小。

窄脉冲信号持续的时间非常短暂,为了能够有效地捕捉到窄脉冲信号,对A/D采样率和处理器速率提出了较高的要求,传统的数据采集已经不能满足系统设计需求。

本文介绍的单路多次低速数据采集方案硬件结构简单,成本低,能够满足系统设计要求。

1系统设计理论依据根据电磁波理论,电缆即传输线。

假若在电缆的一端发送一探测脉冲,它就会沿着电缆进行传输,当电缆线路发生障碍时会造成阻抗不匹配,电磁波会在障碍点产生反射。

在发射端,由测量仪器将发送脉冲和反射脉冲波形记录下来。

实际测试中,具体障碍的波形有所差异:断线(开路)障碍时,反射脉冲与发射脉冲极性相同;而短路、混线障碍时,反射脉冲与发射脉冲极性相反。

波形如图1所示。

图1发射脉冲与反射脉冲波形设从发射窄脉冲开始到接收到反射脉冲波的时间为$t,则:l=v#$t2其中,v为脉冲波在电缆中的传输速度;l为电缆故障点与脉冲波送入端的距离。

由以上分析可知,在同一个固定障碍的线路上多次送入同一脉冲电压,其反射脉冲将同样地在同一位置多次出现。

要实现对反射窄脉冲的捕获和1m的测距分辨率(在波速为200m/L s的情况下),则$t=2lv=2@1200=0.01L s =10ns。

即要求抽样的时间分辨率为10ns,对应的数据采集系统频率高达100MHz。

同时,最大测量范围是2km 时,要求发射脉冲的重复周期T=2lv=2@2000200=20L s。

实际上,电磁波在电缆中的传播速度可能小于200m/L s,这就要求发射脉冲的重复周期大于20L s 。

该时域反射已发射脉冲的重复周期T =40L s,因此需要存储的数据是40L s 的时间间隔,每10ns 采集一个点,共需要4K 个存储单元。

2 系统硬件设计采集系统的硬件电路由单片机、A/D 转换器、隔离器、存储器、地址发生器及相应的控制逻辑组成,其结构如图2所示。

本文选用TI 公司的单片机MSP430F149。

图2 系统硬件结构框图脉冲波形和反射波形在同一测试电缆线上是可多次重复出现的。

只要发射脉冲产生一次,反射脉冲就会产生一次,而且波形是相似的。

当要求对波形进行100MH z 的数据采集时,只需使用转换速率为25MH z 的A/D 转换器进行4次采样,每次的间隔时间为是10ns 。

因此,可以采用该方案进行数据采集,将系统设计的成本降到最低,满足电缆测试的高精度要求。

3 系统软件设计3.1 单片机控制部分的设计单片机控制部分主要完成系统清零和数据读出。

其具体功能是:负责A/D 转换过程的启动及控制;对采样后存储于存储器内的采集数据进行处理。

其中,P2口用作数据端口,P1.0为系统清零位(包括地址以及控制逻辑部分),P1.1控制A/D 转换器与存储器的连接和断开,P1.2为采集完成位,P1.3读出数据地址信号控制,P1.4完成对存储器的读写控制。

系统上电后,单片机首先控制A/D 转换器直接和存储器连接,接着给出系统清零信号,将地址和控制逻辑的计数器清零,等待触发脉冲的到来,单片机进入低功耗模式。

开始数据采集后,单片机以中断方式来判断采集是否完成;采集完成后P1.2产生中断信号,唤醒单片机;系统再一次清零并断开A/D 转换器和存储器的连接,控制地址发生器将存储在里面的数据读出,一次采集就完成了。

3.2 FPGA 控制逻辑的设计窄脉冲时域反射仪要求的分辨率较高,所以要求的采样频率相当高。

例如,要实现1m 的测距分辨率(在波速为200m/L s 的情况下),要求波形抽样的时间分辨率约为10ns,对应的数据采样频率达100MHz [3]。

逻辑控制要实现对一固定波形多次采样,并进行波形拼凑。

实现高速数据采集电路,即将需一次完成的100MHz 高速采样[2]转换为较低频率的4次采样,将各次采样的结果进行重新组合,以拼凑出一个完整的100MH z 采样波形。

系统的实际数据采样速率为25MHz,采样时间间隔为40ns 。

每完成一次波形测试,仪器要连续发射4次脉冲,数据采集电路启动4次。

由于障碍点是固定的,每次发射脉冲时仪器接收到的脉冲反射波形是相似的,只不过发射脉冲的时刻与启动采样的时刻延时分别从0ns 、以10ns 为间隔增加到40ns 。

3.2.1 FPGA 的控制流程FPGA 的控制流程如图3所示。

硬件逻辑控制模块可以产生高速数据采集所需的A/D 转换器和存储器的控制信号。

图3 FPGA 的控制流程3.2.2 FPGA 控制逻辑的具体实现高速数据采集[1]控制逻辑的设计主要包括:脉冲个数检测电路的设计和读写存储器的地址逻辑生成部分的设计。

OP 信号产生原理图如图4所示。

图4 OP 信号产生原理图脉冲个数检测电路是通过2个2位的计数器来实现的。

连接T RIG(触发启动信号)的计数器(启动计数器),判断当前是第几个脉冲,它的状态过程是00v 01v 10v 11,连接100MH z 晶体振荡器的计数器(晶振计数器)用来统计10ns 脉冲的个数。

也就是说,当连接触发启动信号的计数器从00v 01时,晶振计数器是00状态,这时后面的状态选择输出一个由低到高的跃变OP (输出脉冲),控制后面25MH z 数据采集开始。

当启动计数器又有一个触发过来(从01v 10)时,晶振计数器就开始从00v 01,也就是统计一个10ns 。

统计完以后,后面的状态选择又输出一个由低到高的跃变OP,开始25MH z 数据采集。

以次类推,分别是延迟20ns 和30ns 开始数据采集。

得到的OP 仿真图如图5所示。

在逻辑控制设计完成后,将最后得到的25MH z 时钟输入17位计数器。

每次上升沿到来,地址加1,生成的地址信号使得采样的信号存入对应的地址单元。

使用Q9位是为了让输出端可以产生低电平,从而在采样数据到达所需个数时,有一个上升沿来触发其所控制的触发器,使得数据采样暂停,等待下一次采样。

Q12用作反馈,数据采样到了4K 后通过它进行反馈,停止A/D 芯片的工作,同时将地址计数器清零,准备数据读出。

当存储器存满4K 的数据,AP _OE 输出高电平,用于控制A/D 芯片和内部地址计数器。

可以看到,地址计数器在数据采集到达4K 后也清零,在初始的位置等待数据的读出。

系统控制原理图如图6所示。

系统控制仿真图如图7所示。

4 结 论本系统在MSP430F149单片机和FPGA 控制下,通过多次低速数据采集并对采样到的数据进行重组,实现了高达到100MH z 的高速数据采集与存储。

该系统不但具有硬件成本低、系统功耗低的优点,而且数据采样频率完全不受单片机速度的影响,只取决于所选用A/D 转换电图5 OP 仿真图图6 系统控制原理图图7系统控制仿真图路的速度和控制逻辑的设计。

其测量结果准确度高,环境实用性强,可有效解决电缆断点测定的难题。

参考文献[1]杨理践,于潇宇,高松巍.基于FPGA的海量数据采集系统的设计[J].测控技术,2009(5).[2]皮代军,张海勇,叶显阳.基于FPGA的高速实时数据采集系统设计[J].现代电子技术,2009(6).[3]章勇勤,艾勇,邓德,等.基于FPGA的超高速数据采集与处理系统[J].数控采集与处理,2009(2).[4]马育锋,龚沈光.基于MSP430单片机的多路信号采集系统[J].武汉理工大学学报:交通科学与工程版,2009(2).[5]刘军,周东辉,周亚楠.一种深海长期观测低功耗数据采集装置[J].微计算机信息,2009(10).[6]马雄楠,方方,邱远法.基于MSP430的微功耗计数电路的设计[J].核电子学与探测技术,2008(4).(收稿日期:2009209227)!21磁盘等大容量的存储设备,除稳定性外,最主要考虑的是有效空间利用率。

从表1中可以看出,在这3种文件系统中,msdos文件系统的空间利用率要高一些,minix文件系统次之,ext2文件系统最低。