高速数据采集系统设计

基于PCI-1712的高速数据采集系统设计

的数据采集系统。传统的计算机使用 IA S 总线, 其不仅传输 速度慢, 传输数据量小, 而且系统移植性差, 在现代计算机中

多使用 P I C 总线 , 其具有 即插 即用 、 功能强大 、 使用方便等特

点。 因此, 本次设 计利用 P I总线技术, C 通过使用研华公 司提 供 的 P I 1 1 数 据采集卡, 实现对声音信号 的高速 采集 , C一 7 2 来

w hic c b wi h an e del y app ed n ari us li i v o hig -s ed at a qui t n h pe d a c si iO fi d. el

Ke wod y rs:P I 1 1 C 一 7 2:D A; H g p e a a A q i i i n C 十 B i d r M ih S e d D t c u st o ; + u l e

(e a t e t o n o m t o n ie r n , N n h n a g o g U i e s t ,J a g i N n h n 3 0 3 D pr m n f If r a i n E g n e ig a c a g H n kn n vr i y i n x a ca g 3 0 6 )

李锦 王 琪 宫明广 江民俊 王 磊

L i W n i G n i g u n J a g M n u W n e i J n a gQ o gM ng a g i n ij n a g L i

高速数据采集与处理系统设计研究

高速数据采集与处理系统设计研究随着科技的不断进步和社会的快速发展,数据已经成为了企业决策和业务开展的最重要资源之一。

为了更好地收集和处理数据,不少企业开始采用高速数据采集与处理系统。

本文将详细介绍高速数据采集与处理系统的设计研究,重点探讨其应用场景、数据处理流程和技术实现。

一、高速数据采集与处理系统的应用场景高速数据采集与处理系统适用于数据量极大、实时性要求高的企业。

比如金融行业的交易数据、电信运营商的通信数据、物流公司的运输数据等等。

在这些场景下,数据的产生和流动速度非常快,传统的数据采集和处理方案已经无法胜任。

二、高速数据采集与处理系统的数据处理流程高速数据采集与处理系统的数据处理流程相对于传统的数据处理方案来说更加简单高效。

常用的数据处理流程包括以下几个步骤:1. 数据采集:通过网络、传感器等方式对产生的数据进行采集。

2. 数据传输:将采集到的数据通过网络传输至数据中心。

3. 数据处理:对采集到的数据进行处理,包括数据清洗、数据分析、数据挖掘等等。

4. 数据存储:将处理后的数据存储到数据库中,以便于后续的数据分析和业务决策。

5. 数据展示:通过数据可视化工具将处理后的数据以图表等形式进行展示。

三、高速数据采集与处理系统的技术实现高速数据采集与处理系统的技术实现主要依赖于以下几个方面:1. 异步模型:通过异步模型实现高并发的数据采集和处理。

2. 分布式计算:将数据处理的任务分散到多台服务器上进行并行计算,提高数据处理效率。

3. 大数据存储:通过大数据存储技术,可以高效地存储处理后的数据。

4. 数据可视化:通过数据可视化工具可视化处理后的数据,便于用户进行数据分析和业务决策。

四、高速数据采集与处理系统的优势相比传统的数据采集和处理方案,高速数据采集与处理系统具有以下几个优势:1. 高效性:高速数据采集与处理系统可以实现实时数据采集,对数据进行高效的处理和存储。

2. 稳定性:高速数据采集与处理系统可靠性高,能够在高并发的情况下正常运行。

基于FPGA的高速数据采集系统设计与实现的开题报告

基于FPGA的高速数据采集系统设计与实现的开题报告一、选题背景与意义在现代工业领域,高速数据采集是必不可少的环节,对于某些应用场景,如医学图像、通信信号和自然界信号的采集等,必须保证采样率高、抗噪性强的特点。

面对如此巨大的数据采集挑战,传统基于PC机的采集系统已经难以满足实时性和高速性的要求,而基于FPGA的高速数据采集系统从其高速、高精度、低功耗、灵活可靠等诸多特点上来看,成为了实现高速数据采集的首选方案。

因此,本文将对基于FPGA的高速数据采集系统设计与实现开题进行研究。

二、研究内容本课题旨在通过对基于FPGA的高速数据采集系统设计与实现开题进行深入研究,侧重于以下几个方面:1. 基于FPGA芯片架构的深入研究,尤其是在高速、可靠、低功耗等方面的性能表现。

2. 研究采样率、信噪比、滤波器等方面在数据采集系统中的应用。

3. 设计高速数据采集控制系统,探究其在高速数据采集系统中的作用和设计原理。

4. 进行基于FPGA的高速数据采集系统硬件电路设计、软件编码及实现,并通过实验验证其性能。

三、研究方法本文采用计算机仿真分析和实验研究相结合的方法,首先通过软件工具对系统进行模拟,了解系统设计的基本原理和方法,然后进行硬件电路设计和软件编码,实现实际的高速数据采集系统,最后对实验结果进行分析和总结。

四、预期成果1. 实现一套基于FPGA的高速数据采集系统,该系统具有高速性、稳定性、可靠性、低功耗等优点。

2. 对该系统进行了性能测试,并分析系统在数据采集过程中的表现及优劣。

3. 从系统设计、电路设计、软件编写三个角度,对基于FPGA的高速数据采集系统设计与实现开题进行了研究,并提出了可供参考的经验和具体指导意见。

五、可能面临的问题及解决方案1. FPGA硬件电路设计难度大。

解决方案:参考多数学者的研究成果,针对不同应用,找出符合实际需要的电路设计。

2. 信号处理算法的开发。

解决方案:充分利用智能算法,设计高效低延迟的算法并进行实际验证。

基于FPGA的高速数据采集系统设计

基于FPGA的高速数据采集系统设计随着科学技术的不断进步,数据采集系统在许多领域都发挥着重要作用。

为了满足高速数据采集的需求,基于现场可编程门阵列(FPGA)的高速数据采集系统设计应运而生。

本文将介绍这一系统的设计原理和关键技术。

首先,我们需要了解FPGA的基本原理。

FPGA是一种可编程的硬件设备,可以根据需要重新配置其内部逻辑电路。

这使得FPGA在数据采集系统中具有极大的灵活性和可扩展性。

与传统的数据采集系统相比,基于FPGA的系统可以实现更高的采样率和更低的延迟。

基于FPGA的高速数据采集系统设计主要包括以下几个关键技术。

首先是模数转换(ADC)技术。

ADC是将连续的模拟信号转换为数字信号的关键环节。

在高速数据采集系统中,需要使用高速、高精度的ADC来保证数据的准确性和完整性。

其次是FPGA内部逻辑电路的设计。

为了实现高速数据采集,需要设计高效的数据处理逻辑电路。

这些电路可以实现数据的实时处理、存储和传输等功能。

同时,还需要考虑电路的时序约束和资源分配等问题,以确保系统的稳定性和可靠性。

另外,时钟同步技术也是高速数据采集系统设计的重要内容。

在高速数据采集过程中,各个模块需要保持同步,以确保数据的准确性。

因此,需要设计合理的时钟同步方案,保证各个模块在同一个时钟周期内完成数据的采样和处理。

最后,还需要考虑系统的接口和通信问题。

基于FPGA的高速数据采集系统通常需要与其他设备进行数据交互,如计算机、存储设备等。

因此,需要设计合适的接口和通信协议,实现数据的传输和存储。

综上所述,基于FPGA的高速数据采集系统设计涉及多个关键技术,包括ADC技术、FPGA内部逻辑电路设计、时钟同步技术以及接口和通信问题。

通过合理的设计和优化,可以实现高速、高精度的数据采集,满足现代科学研究和工程应用的需求。

这将为各个领域的数据采集工作带来巨大的便利和发展空间。

电力系统高速数据采集系统设计

接收 和发送端与 其S I 和S O口相 连 , 来进行数 据传输 , GI P I O2 7 和 G I P I O2 8 分别用来对存 储器 的片选和读 写进行控制 。 电力系统高速数 据采集系统是一种应用在 电力系统实时采集 电能 质 量 情 况 的 一 种 采集 装 置 。 目前所 采 用 的AD 转 换 器 件 不 能 同 3系 统软 件件 设 计 步转换六路信号 , 所 测 结 果 之 间有 一 定 的 延迟 性 [ 1 】 。 针 对 以上 缺 点 , 3 . 1 谐 波分 析 算法 现采用D s P 2 8 1 2 和AD 7 6 5 6 相 结合 的方 法 , 所用的AD7 6 5 6 具有的六 本文数据分析 算法采用快速傅立 叶变换, 快速傅 氏变换是离散 路 同步采样特性 , 克服 了测量结果 之间延迟的缺点 , 使得测量精度 傅 氏变换 的快速算法 , 它是根据离散傅 氏变换 的奇 、 偶、 虚、 实等特 高。 以上 优点 弥补 了 目前录波器 的缺 陷, 达 到了 目前应用 的要 求。 性, 对离散傅立 叶变换 的算法进行 改进获得 的。 1电力系统高速数据采集系统结构原理 设X( m) 为M项 的复数 序列 , 由D F T变换可知任意一 X ( n ) 的计 算都需要M次复数乘法和M一1 次复数加法 , 一次复数乘法等于两次 电力系统的三相 电压 和电流通过滤波器 滤去高频干扰信号和 一 次 复 数 加 法 相 当于 两 次 实 数 加 法 , 即 低频漂移信号 , 经过 滤波 的电压和 电流信号通过 电压传感器和 电流 实 数 加 法 和 四次 实 数 乘 法 , 使把一次复数加法 和一 次复数乘法定义成一次“ 运算” , 那么 求出N 传感器按一 定的比例转成 适合 A D 7 6 5 6 采样 的小幅值 电压 信号 , 然 项复数序 列的X( n ) , 即M点变换大 约就 需要M2 次运算 。 当M= 1 0 2 4 后D S P T MS 3 2 0 F 2 8 1 2 控制AD7 6 5 6 将 六路模拟量转换成数 字量 , 点甚 至更 多的时候 , 需要M2 =l 0 4 8 5 7 6 次运算 , 利用周期性和对 称 并从A D7 6 5 6 读取6 路数据并存储在存储器 中, 利用相关算法对所 采 性, 把一个M项序列( 设M= 2 R , k 为正整数) , 分为两个M/ 2 项 的子序 数据进 行分析 , 计算相 关参数 。 列, 每 个 M/ 2 点 DF T变 换 需 要 M2 / 2 次运算 , 再 用 M 次运 算 把 两 个 2系统 硬 件设 计 M/ 2 点 的DF T 变 换 组合 成一 个M点 的 D F T变 换 。 这 样 变 换 以后 , 总 2 . 1 数 据采 集 处理模 块 硬件 电路 设 计 的运 算次数 就变成M+2 ( M/ 2 ) 2 = M+ M2 / 2 。 继 续上 面的例子 , 高速数据采集模块采用 以D S P T MS 3 2 0 F 2 8 1 2 为控 制核 心 , 模 M=1 0 2 4 时, 总的运算次数就变成 了5 2 5 3 1 2 次, 节省 了大约5 0 %的运 数转换芯片采用A D7 6 5 6 芯片 , 系统实现 1 2 . 8 KHz 的采样频率 , D S P 算量 。 而如果 我们将 这种“ 一分为二 ” 的思想不断进行下去 , 直到分 采用F F T算法对 电力 系统 电压和 电流进行各次谐波 的分析 , 计算出 成两 两 一组 的DFT运 算单 元 , 那 么M 点 的DFT变 换就 只 需要 功率 、 有效值 等参 数 , 并将采集数据存 储在存储器 中。 Ml o g 2 M次的运算, M在 1 0 2 4 点时 , 运算量 仅有 1 0 2 4 0 次, 是先前 的直 2 . 2 A D7 6 5 6采样 电路 设 计 接算法 的1 %, 点数 越多 , 运算量 的节约就越大 , 这就是F F T的优越 高速数据采样 电路采用AD I 公司推 出的6 通道 、 高集成度 、 1 6 b i t 性。 T I 已经 为 D S P 提供创建 好的F F T 库 函数 , 其具体 的实现方法会 逐次逼近型AD 7 6 5 6 , AD7 6 5 6 的并行数 据 E l DB 0 - D B1 5 与相连D S P 在软件 部分进行详细介绍 。 的G P I OA0 ~l 5 I O 端 口, 作为数据传输 口; AD 7 6 5 6 的C O NV S T A、 3 . 2主程 序 设 计 CONVS T、 C ONVS T C三个端 口与DS P的G PI OB 0 相连, 作为 系统初始化完成后 , D S P F 2 8 1 2 控 制AD 7 6 5 6 进 行 数 据 采集 , 六 AD 7 6 5 6 的6 路 同时采样启动 控制 口; A D7 6 5 6 的/ c s 端 口与DS P 的 路数据 采集完成后 , D S P 进行F F T运算分析 出各次谐波分量 , 对采 G P I O B1 端 口相连作 为AD 7 6 5 6 的片选控 制 口, AD 7 6 5 6 的/ RD与 集的六路数据进行分析 , 包括有效值 、 频谱分析、 平均值 和最大值等 D S P 的G P I OB 2 端 口相连作为读控 制 口; AD 7 6 5 6 的B US Y端 口与 参数 , 并将分析 的相 关数据 以及 原始数据存 储在 存储 器中 , 按此程 D S P 的G P I OB 3 端 口与相连 , 用来检测AD转换是否结束 。 序 不断采集并存储在存储 器 中。 2 . 3 DS P T MS 3 2 0 F 2 8 1 2最 小 系统设 计 4结 语 本 系 统 采 用 电源 管 理 芯 片 TPS 7 3H D 3 01 给 DSP供 电 , 本文设计 出了一种基于D S P 和Z B e e 无线通信模块 的新 型油 T P S 7 3 HD 3 0 1 的输人 电压为5 V, 输 出电压为3 . 3 V 和1 . 9 V, 两种 电压 系 统运算速度快 , 采集 精度高 , 设备移动方 分 别 经 过 相 应 的 滤 波 电 路 供 给 D SP, DSP的 R ESET 管 角 与 田油井 电力监测 系统 。 组 网灵 活 , 运行稳定可靠 , 应用前景 比较好。 T P S 7 3 HD 3 0 1 的R E S E T 管角直接相 连。 本系统时钟 电路采用D S P内 便 , 部 晶体 振荡器 电路 , 外接 晶体的工作 频率 5 0 MHz , D S P内部具有一 参考文献

高速数据采集系统设计基于JESD204B说明书

2nd International Conference on Computer Engineering, Information Science & Application Technology (ICCIA 2017)The Design of High Speed Data Acquisition System Based on JESD204BYu Wang a, Qingzhan Shi b and Qi FengCollege of Electronic Science and Engineering, National University of Defense Technology,Changsha 410073, Chinaa******************,b********************Keywords: Data acquisition system, JESD204B interface, High-speed ADC.Abstract. Recently, various acquisition systems require data converters to provide higher resolution and sampling rates. The physical layout of parallel interfaces and the bit rate limitations of serial LVDS methods pose technical hurdles for designers. The design is based on the classical architecture of FPGA+DSP+ADC of data acquisition system. The High speed ADC is based on JESD204B interface with four slices and two channels, it can meet the requirements of high-speed acquisition, and high-speed sampling of eight channels. It provides a good method for the design and application of various high-speed acquisition systems, and it effectively solves all kinds of problems in parallel transmission of traditional data acquisition, and brings great engineering application value.1.IntroductionIn our era, the increasing of demand for high data rate application is never stop. This trend leads to the development of high resolution and high sample rate ADC devices. As early as 1991, the United States Navy studied and designed a high-performance programmable signal processor, the architecture of FPGA+DSP had been widely used. Many universities and institutes in China have also developed their own signal processing systems under the FPGA+DSP architecture [1]. Combined with ADC chip, the high-speed acquisition system has also been implemented, but it is difficult for the data transmission to meet the needs of multi-channel, high bandwidth and small size when the traditional data acquisition system adopts parallel transmission mode of multiplex data wires. As a result, the JEDEC international organization has launched a new AD/DA sampling data transmission standard JESD204. So that, the development of the high-speed acquisition system can develop continuously [2].2.The overall hardware designThe design is based on JESD204B interface, designed to achieve high-speed data acquisition system. The design is based on the classical FPGA+DSP+ADC data acquisition system architecture. The FPGA chip uses the XC7VX485T from the Xilinx Virtex-7 series. GTX, its maximum serial speed transceiver, supports the maximum line speed of 12.5Gbps. The DSP chip uses the TMS320C6678 from TI, it integrates 8 arithmetic cores, and the highest processing speed of single core can reach 1.25Gbps. The ADC chip uses the ADC32RF45 from TI, its data is output based on JESD204B interface. As shown in Fig 1, the eight channels sampling signal enters the ADC chip firstly, and then the serial high-speed transceiver GTX is transmitted to the FPGA by the JESD204B interface, then the data is sent to the DSP through SRIO for signal processing operations.FPGA DSPADC x4SRIO PCIEGPIOJESD204B 8Channel FLASH DDR3x4GbpsEthernet FLASH DDR3x2HDMIFig.1 System overall structure diagramIn the design of the data acquisition system, the FPGA’s external interface HDMI, a 19 pin high-speed data interface, is used for data’s communication with external memory. On the board, we connect the four differential signal line of the FPGA’s high speed serial transceiver (GTX) to the HDMI interface. The external high-speed interface of DSP adopts Gigabit Ethernet to realize high-speed data transmission. Both the FPGA and the DSP have an external 256MB Flash memory, In addition, the FPGA has two DDR3 external memory to form the storage space of the 1GB, DSP has four DDR3 memory external to form the storage space of 2GB.3. JESD204B InterfaceIn the field of PC and embedded systems, it has been an empty talk that the method for improving bus bandwidth by raising bus operating frequency under the condition of a parallel bus data width. It cannot be realized at all because of the influence of technology and environment in the actual implementation. Therefore, the communication structure of the serial bus is changed from parallel bus communication. Typically, the ADC is 12~16 bit data lines, and strictly required to be aligned on one edge of the clock. The higher frequency the ADC operating, the greater data offset between the data lines, and then synchronization between data is becoming more difficult. The JEDEC international organizations have fully learned the advantages of PCIE/SRIO and other serial bus communication protocols based on data packet (frame format). The JESD204 protocol was introduced in 2006, it is the a differential pair adopted the CML level, instead of the 12~16 bit parallel data line, realizing serial communication interface and supporting the highest 3.125Gbps data transmission rate of ADC device. In January 2012, the JESD204 bus protocol has been upgraded to the JESD204 B.01 version, the maximum transmission rate of each pair of differential lines is supported by 12.5Gbps [3,4]. Table 1 Comparison of JESD204 with other interfacesNumber of Channels Resolution CMOS Pin Count LVDS Pins Count (DDR) CML Pin Count (JESD204B)1 14 13 14 42 14 26 28 44 14 52 56 68 14 104 112 6Fig.2 CMOS, LVDS, and CML Driver Power ComparisonIn summary, the advantages of JESD204B include the following three points:(1) Decreased in pin number, simplified system design, greatly simplified the wiring between ADC and FPGA(2) Because wiring is simpler and pin number is less, using JESD204B will make the package smaller and simpler.(3) High speed ADC devices consume less power per unit after adopting CML level.At present, the TI, the ADI and other companies have their latest high-speed ADC chip based on the JESD204B interface. ADC32RF45 released by TI, AD9625 released by ADI, and the latest AD9208 released by ADI Company in April 2017, these all belong to the new ADC series adopted with JESD204B interface. In respect of Field Programmable logic device (FPGA), the company, such as Xilinx and Altera, also supports the JESD204B interface. In addition there are JESD204B dedicated clock chip, such as LMK042828, HMC7044 and so on.4.The Key of ADC design interfaceWe can implement the JESD204B protocol by FPGA's GTX interface, to parse the data emitted by ADC correctly. The hardware uses the FPGA’s GTX interface directly, and the GTX is connected with the data-in pin of the ADC. ADC data-out pin as the sending end, FPGA GTX port as the receiving end, to achieve data transmission on the line [5]. The software uses the 8B/10B codec module and the control character detection module which are embedded in the GTX interface.low two bit make up a frame with 16bit data. After framing, the data is encoded by 8B/10B, then it becomes 20 bit. Sending to Serial high-speed transceiver GTX of FPGA, FPGA complete the operation of the 8B/10B decoding and the analysis of JESD204B protocol. Setting the ADC32RF45 sample clock to 2.5GHz, the rate corresponding to the encoding at all levels is shown below.Table 2 Comparison of JESD204BClock/GH z Data-width/bit Rate/Gbp sRemark Original data 2.5 14 8.4 ADC Sampled DataFraming 2.5 16 10 Zero-paddingCoding 2.5 20 12.5 8B/10BThe ADC is dual channel, each channels has 4 lanes, that is, 4 pairs of CML data lines. As can be seen from the chart above, ADC eventually sends the sampled data at a rate of 12.5Gbps, GTX, the receiving rate of the FPGA side should also be set to 12.5Gbps.5. Clock designJESD204B begins with the edge of the clock signal to identify synchronization. And through a certain handshake signal, the sender and receiver can correctly recognize the frame length and boundaries. Therefore, the clock signal and its timing relation are extremely important to JESD204B. The following is a multi-device synchronization solution for the JESD204B system, the Device Clock is the main clock for the device operation. A clock that is usually sampled in a digital to analog converter or a clock with integer multiples. The frame and multi frame clock of the protocol itself are also based on Device Clock. SYSREF is the edge of the Device Clock used to indicate different converters or logic, or the reference delay between different devices.In the JESD204B system, the synchronization of data converters can be broken down into four basic requirements. These requirements are vividly depicted in Fig.4.(1) The phase alignment of the device clock is implemented on each data converter;(2) The setting and holding time of the SYSREF (relative to the device clock) are met on each data converter and logic element;(3) An appropriate resilient buffer release point is selected in the JESD204B receiver to ensure deterministic delay; (4) Need to meet the SYNC signal timing requirements when necessary. A D CA D CA D CA D C Data SYNC DataSYNC Data SYNCDevice Clock SYSREF Device ClockSYSREF Device Clock SYSREFDevice ClockSYSREFLogic DeviceClock Distirbution DataSYNCFig.4 Multi device synchronization solution for JESD204B systemADI and TI have high performance clock jitter attenuator with JESD204B, such as HMC7044, LMK04828 and so on. Their Device Clock, and SYSREF are paired output, its output timing meets its timing requirements, and its application is relatively simple.6.ConclusionThis paper utilizes the advanced high-speed ADC with JESD204B interface, combine the latest ADC chip and Xilinx 7 Series resources, and proposes the design of high-speed data acquisition system based on JESD204B. This paper first describes the overall design of the system, and then we detailed for each module design. We first solve the core processing module of FPGA+DSP. Both of FPGA and DSP communicate with each other through SRIO, FPGA pretreatment data is sent to the DSP for signal processing. Utilizing existing technology and hardware, a high-speed data acquisition system is designed with the JESD204B interface ADC which has higher resolution and higher sampling rate (3Gbps or so). It can be well suited to eight channel high-speed sampling, the design is miniaturized and the wiring is simpler. FPGA resource consumption is reduced by about half of resources compared to traditional parallel data lines, it has great prospect of engineering application. References[1] Ran Yan, XI Pengfei. High Speed Serial Data Acquisition System Based on JESD204 Protocol [J].Electronic Sci. & Tech. 2015, 28(5):17-19[2] Zhou Yuxuan, Clock Circuit Design of 2.5 GSPS High Resolution Data Acquisition System [D].UESTC, 2016[3] ADI. JESD204B Survival Guide [M]. [USA]: ADI, 2013[4] ADI. JESD204B serial interface clock requirements and their implementation [M]. [USA]: ADI,2013[5] Xilinx. 7 Series FPGAs GTX/GTH Transceivers [M]. USA: Xilinx, 2016.。

高速公路交通信息采集系统设计

高速公路交通信息采集系统设计随着社会经济的快速发展和人们生活水平的不断提高,交通问题逐渐成为制约国家发展的重要因素之一。

在现代城市中,交通拥堵已经成为了人们生活中的一大烦恼,而高速公路交通信息采集系统的设计,就是为了解决这个问题。

本文将从设计的背景、设计的目标和设计的方案等方面,对高速公路交通信息采集系统进行探讨。

一、设计的背景随着城市化进程的加速,人口的大规模流动和车辆的快速增加,交通拥堵的问题越来越严重。

高速公路作为重要的交通设施,承载着大量的车流和人流,但是由于车辆数量的增加,导致高速公路的交通流量越来越大,交通拥堵问题日益严重。

同时,传统的高速公路交通管理方法已经不能很好地处理复杂的交通环境,迫切需要一种新的高效交通信息处理系统来更好地管理高速公路交通。

二、设计的目标高速公路交通信息采集系统的设计的目标,是帮助交通管理部门更好地处理交通信息,实现道路交通的科学管理。

具体地说,它可以实现以下几个方面的目标:1. 实现高速公路实时监控。

利用高精度跟踪技术,通过自动化的摄像头系统,实现对道路上的行车情况进行实时监测,为交通管理者提供实时的路况数据。

2. 提高交通安全水平。

通过对道路上的交通信息进行采集和处理,及时发现各种交通违规行为,并及时进行处理,提高交通规范度和安全水平。

3. 降低耗时和物力成本。

通过智能化的高速公路交通信息采集系统,自动化的完成各种交通信息的收集和处理,降低人力资源和物资投入成本,提高道路交通的效率。

4. 实现路况预测功能。

通过对历史数据和实时采集的数据进行分析,对未来的交通情况进行预测。

为交通部门提供预测数据,帮助其更好地制定管理决策。

三、设计方案高速公路交通信息采集系统的设计中,需要解决以下几个重点问题:1. 数据采集和处理高速公路交通信息的采集和处理,是系统设计的核心和难点。

通过高精度的摄像头和相关传感器,对道路上的车辆行驶情况进行实时监测,并通过智能化算法对各种信息(如车辆数量、速度、车型、车牌等)进行采集和处理,通过智能分析技术和大数据处理技术,对采集的数据进行分析和处理,生成管理人员所需要的各类报表和图表,达到及时监管和迅速反应的目的。

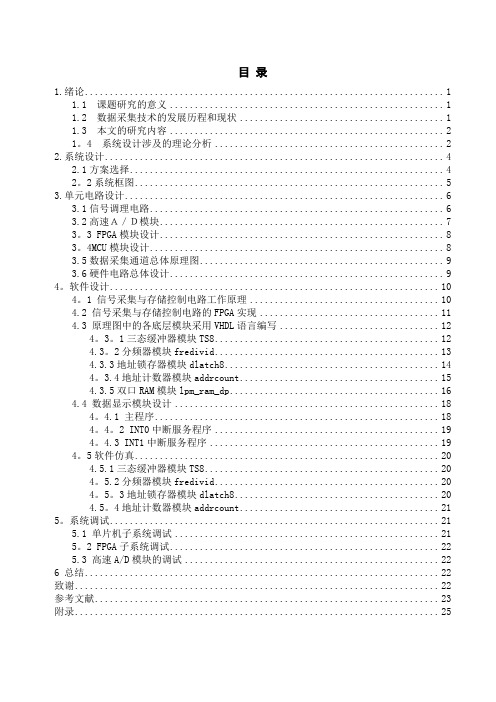

毕业设计--基于单片机的高速数据采集系统设计

目录1.绪论 (1)1.1 课题研究的意义 (1)1.2 数据采集技术的发展历程和现状 (1)1.3 本文的研究内容 (2)1。

4 系统设计涉及的理论分析 (2)2.系统设计 (4)2.1方案选择 (4)2。

2系统框图 (5)3.单元电路设计 (6)3.1信号调理电路 (6)3.2高速A/D模块 (7)3。

3 FPGA模块设计 (8)3。

4MCU模块设计 (8)3.5数据采集通道总体原理图 (9)3.6硬件电路总体设计 (9)4。

软件设计 (10)4。

1 信号采集与存储控制电路工作原理 (10)4.2 信号采集与存储控制电路的FPGA实现 (11)4.3 原理图中的各底层模块采用VHDL语言编写 (12)4。

3。

1三态缓冲器模块TS8 (12)4.3。

2分频器模块fredivid (13)4.3.3地址锁存器模块dlatch8 (14)4。

3.4地址计数器模块addrcount (15)4.3.5双口RAM模块lpm_ram_dp (16)4.4 数据显示模块设计 (18)4。

4.1 主程序 (18)4。

4。

2 INT0中断服务程序 (19)4。

4.3 INT1中断服务程序 (19)4。

5软件仿真 (20)4.5.1三态缓冲器模块TS8 (20)4。

5.2分频器模块fredivid (20)4。

5。

3地址锁存器模块dlatch8 (20)4.5。

4地址计数器模块addrcount (21)5。

系统调试 (21)5.1 单片机子系统调试 (21)5。

2 FPGA子系统调试 (22)5.3 高速A/D模块的调试 (22)6 总结 (22)致谢 (22)参考文献 (23)附录 (25)高速数据采集系统设计摘要:随着数字技术的飞速发展,高速数据采集系统也迅速地得到了广泛的应用.在生产过程中,应用这一系统可以对生产现场的工艺参数进行采集、监视和记录,为提高生产质量,降低成本提供了信息和手段。

在科学研究中,应用数据采集系统可以获取大量的动态数据,是研究瞬间物理过程的有力工具,为科学活动提供了重要的手段.而当前我国对高速数据采集系统的研究开发都处于起步阶段,因此,开发出高速数据采集系统就显得尤为重要了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速数据采集系统

设计

基于FPGA和SoC单片机的

高速数据采集系统设计

一.选题背景及意义

随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分。

高速数据采集系统在自动测试、生产控制、通信、信号处理等领域占有极其重要的地位。

随着SoC单片机的快速发展,现在已经能够将采集多路模拟信号的A/D转换子系统和CPU核集成在一片芯片上,使整个数据采集系统几乎能够单芯片实现,从而使数据采集系统体积小,性价比高。

FPGA为实现高速数据采集提供了一种理想的实现途径。

利用FPGA高速性能和本身集成的几万个逻辑门和嵌入式存储器块,把数据采集系统中的数据缓存和控制电路全部集成在一片FPGA芯片中,大大减小了系统体积,提高了灵活性。

FPGA 还具有系统编程功能以及功能强大的EDA软件支持,使得系统具有升级容易、开发周期短等优点。

二.设计要求

设计一高速数据采集系统,系统框图如图1-1所示。

输入模拟信号为频率200KHz、Vpp=0.5V的正弦信号。

采样频率设定为25MHz。

经过按键启动一次数据采集,每次连续采集128点数据,单片机读取128点数据后在LCD模块上回放显示信号波形。

图1-1 高速数据采集原理框图

三.整体方案设计

高速数据采集系统采用如图3-1的设计方案。

高速数据采集系统由单片机最小系统、FPGA最小系统和模拟量输入通道三部分组成。

输入正弦信号经过调理电路后送高速A/D转换器,高速A/D 转换器以25MHz的频率采样模拟信号,输出的数字量依次存入FPGA内部的FIFO存储器中,并将128字节数据在LCD模块回放显示。

图3-1 高速数据采集系统设计方案

四.硬件电路设计

1.模拟量输入通道的设计

模拟量输入通道由高速A/D转换器和信号调理电路组成。

信号调理电路将模拟信号放大、滤波、直流电平位移,以满足A/D转换器对模拟输入信号的要求。

2.高速A/D转换电路设计

五.FPGA模块设计

本设计的数据缓冲电路采用FIFO存储器。

FIFO数据缓冲电路原理如图5-1。

图5-1 FIFO数据缓冲电路原理

FIFO的写端口的数据线与ADS931的数据线直接相连,FIFO的写时钟和ADS931采用同一时钟信号CLK0。

FIFO的读端口与单片机并行总线相连,数据输出端口加了三态缓冲器。

地址译码器的片选信号1

CS和读信号RD相或非后作为FIFO的读时钟电路和三态缓冲的使能信号。

FIFO数据顶层原理图如图5-2。

图5-2 FIFO数据顶层原理图

六.F360单片机模块设计。