高速数据采集系统

一种高速实时数据采集系统的设计与实现

(2位 总 线 )2 4M /(4 总 线 )。 3 ,6 Bs6 位 1 2 ] P I 部 总线 一边 与处理 器和 存储 器总线 接 口 C 局

数据后置处理等功能 。用 以完成主机对数据采集前 端 送 出的 1 6位并行数 据 的读取 ,和对传感 器数据 的读

取 、 式的转换 、 送} 格 发 l 】 要 包 括 以下 几 个 功 能 模 块 : 。主 P I 线 控 制 器 、IO缓 存 器 ( 片 C 7 4 7 , 度 C 总 FF 一 Y C 25 深

( olg fMa n E gn eig,Notw sen P ltc nc l nv ri C l e o r e n ie r e i n r etr oye h ia U iest h y,Xia 0 2,Chn ) n 71 7 0 ia

【 btat ei i e o f u r seddt a q it na dt nmi inb sd( C (e p ea C m o et A s c】A ds nn m t do sp = p e aa cus i n r s s o ae m P lP f h rl o pn n r g g h a io a s i

另一边 为外设扩展 提供 高带 宽通道 。这样便将 外设 I / O总线上 移下来 , 不需 C U介 入就可进行数据 传输 P PI C 总线 具有 高性 能 、 使用 方便 、 高协 调性 、 数据 完型

基于VISA技术的高速USB数据采集系统

基于V I SA 技术的高速USB 数据采集系统苏兰兰, 施伟峰(上海海事大学,上海 200135) 摘 要:高速US B 数据采集系统的设计严格遵循US B2.0协议,实现了主机和测试设备之间简单、快速、可靠的连接和通信。

该文介绍了这种数据采集系统的硬件组成、驱动程序和固件程序的设计以及采用虚拟仪器软件Lab W indows/CV I 在V I S A 技术上开发应用程序的设计方法。

关键词:V I S A;Lab W indo ws/CV I ;US B;高速数据采集 中图分类号:TP274 文献标识码:A 文章编号:100528354(2007)0420036204VI SA 2based hi gh speed USB DAQ syste mS U Lan 2lan,SH IW ei 2feng(ShangHaiMariti m e University,Shanghai 200135,China )Abstract :The design of this high 2speed USB DAQ syste m abides by protocol USB 2.0so strictly that it can a 2chieve a si m ple,fast and reliable connection co mm unication bet w een the host and USB devices .This paper in 2troduces the co m position of hardw ares of this syste m ,the design of its driver and fir mw are program s and the m ethod by w hich the virtual instrum ents soft ware Lab w indo w s /CV I is adopted to develop V ISA 2based application program s .Key words :V irtual Instrum ent Soft w are A rchitecture (V ISA );L ab W indo w s /CV I ;Universal Serial B us(USB );High Speed DAQ收稿日期:2006210208作者简介:苏兰兰(19762),女,硕士,研究方向为:控制理论与控制工程,容错控制,神经网络控制等。

高速公路交通信息采集系统设计

高速公路交通信息采集系统设计随着社会经济的快速发展和人们生活水平的不断提高,交通问题逐渐成为制约国家发展的重要因素之一。

在现代城市中,交通拥堵已经成为了人们生活中的一大烦恼,而高速公路交通信息采集系统的设计,就是为了解决这个问题。

本文将从设计的背景、设计的目标和设计的方案等方面,对高速公路交通信息采集系统进行探讨。

一、设计的背景随着城市化进程的加速,人口的大规模流动和车辆的快速增加,交通拥堵的问题越来越严重。

高速公路作为重要的交通设施,承载着大量的车流和人流,但是由于车辆数量的增加,导致高速公路的交通流量越来越大,交通拥堵问题日益严重。

同时,传统的高速公路交通管理方法已经不能很好地处理复杂的交通环境,迫切需要一种新的高效交通信息处理系统来更好地管理高速公路交通。

二、设计的目标高速公路交通信息采集系统的设计的目标,是帮助交通管理部门更好地处理交通信息,实现道路交通的科学管理。

具体地说,它可以实现以下几个方面的目标:1. 实现高速公路实时监控。

利用高精度跟踪技术,通过自动化的摄像头系统,实现对道路上的行车情况进行实时监测,为交通管理者提供实时的路况数据。

2. 提高交通安全水平。

通过对道路上的交通信息进行采集和处理,及时发现各种交通违规行为,并及时进行处理,提高交通规范度和安全水平。

3. 降低耗时和物力成本。

通过智能化的高速公路交通信息采集系统,自动化的完成各种交通信息的收集和处理,降低人力资源和物资投入成本,提高道路交通的效率。

4. 实现路况预测功能。

通过对历史数据和实时采集的数据进行分析,对未来的交通情况进行预测。

为交通部门提供预测数据,帮助其更好地制定管理决策。

三、设计方案高速公路交通信息采集系统的设计中,需要解决以下几个重点问题:1. 数据采集和处理高速公路交通信息的采集和处理,是系统设计的核心和难点。

通过高精度的摄像头和相关传感器,对道路上的车辆行驶情况进行实时监测,并通过智能化算法对各种信息(如车辆数量、速度、车型、车牌等)进行采集和处理,通过智能分析技术和大数据处理技术,对采集的数据进行分析和处理,生成管理人员所需要的各类报表和图表,达到及时监管和迅速反应的目的。

纯国产高速采集存储系统简介

数据入口

存储容量 采集速度 控制口 快视 数据导出口 尺寸 重量 功率 电源 散热方式 工作温度 管理软件 量身定制

可选支持 LVDS、CamLink、10 Gps SFP+、 HD-SDI、SD-SDI、Aurora、SRIO 等接口

4 块 SATA3 SSD 稳定大于 2GB/s USB3.0、UART 上位机 可选 10GE、USB3.0(GE/PCIE 也可定制) 110mm x 160mm <1.0Kg <10W 12V 风冷 0–45℃(可选宽温-40-80℃) 免费提供 可根据需求定制:尺寸、形状、接口、 协议、软件控制等

增值功能:提供鼠标选择区域的灰度统计 自定义硬盘文件管理系统,灵活控制管理硬盘,保证数据完整性

格式化硬盘 多种格式上传记录:可指定地址、指定记录、指定时间上传等方式 剩余存储空间自检

通讯连接自检

FPGA 温度自检 SSD 性能自检

Tel: 18874206254 Email:1139739291@

速度快 接口丰富 容量大 体积小 灵活定制

实物图片 应用领域

软件亮点

操作系统 系统配置 采集、存储、任务参数配置 图像预览 数据记录 支持多通道数据 HDMI、DVI 或 VGA 实时演示、或上位机实时显示 基本回放功能:开始、结束、暂停、继续、快进、快退

简介

已实现所有器件国产化替代!!!!

Y9000 系列便携式高速数据采集存储系统由 007 科技创新自主研发,为国内首 款高性能嵌入式数据采集存储一体化设备。该系统实现了多种物理接口或传输协议下 视频、雷达等高速信号的采集、存储、快视、导出等功能,具有速度快、容量大、体 积小、重量轻、可靠性高等特点,是机载、车载、舰载或野外数据采集应用的首选方 案。

高速数据采集系统设计说明书

基于FPGA和SoC单片机的高速数据采集系统设计一.选题背景及意义随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分。

高速数据采集系统在自动测试、生产控制、通信、信号处理等领域占有极其重要的地位。

随着SoC单片机的快速发展,现在已经可以将采集多路模拟信号的A/D转换子系统和CPU核集成在一片芯片上,使整个数据采集系统几乎可以单芯片实现,从而使数据采集系统体积小,性价比高。

FPGA为实现高速数据采集提供了一种理想的实现途径。

利用FPGA高速性能和本身集成的几万个逻辑门和嵌入式存储器块,把数据采集系统中的数据缓存和控制电路全部集成在一片FPGA芯片中,大大减小了系统体积,提高了灵活性。

FPGA 还具有系统编程功能以及功能强大的EDA软件支持,使得系统具有升级容易、开发周期短等优点。

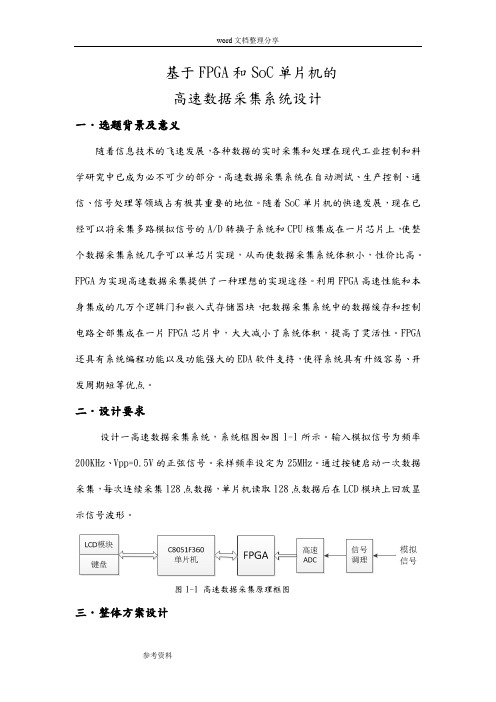

二.设计要求设计一高速数据采集系统,系统框图如图1-1所示。

输入模拟信号为频率200KHz、Vpp=0.5V的正弦信号。

采样频率设定为25MHz。

通过按键启动一次数据采集,每次连续采集128点数据,单片机读取128点数据后在LCD模块上回放显示信号波形。

图1-1 高速数据采集原理框图三.整体方案设计高速数据采集系统采用如图3-1的设计方案。

高速数据采集系统由单片机最小系统、FPGA最小系统和模拟量输入通道三部分组成。

输入正弦信号经过调理电路后送高速A/D转换器,高速A/D转换器以25MHz的频率采样模拟信号,输出的数字量依次存入FPGA内部的FIFO存储器中,并将128字节数据在LCD模块回放显示。

图3-1 高速数据采集系统设计方案四.硬件电路设计1.模拟量输入通道的设计模拟量输入通道由高速A/D转换器和信号调理电路组成。

信号调理电路将模拟信号放大、滤波、直流电平位移,以满足A/D转换器对模拟输入信号的要求。

2.高速A/D转换电路设计五.FPGA模块设计本设计的数据缓冲电路采用FIFO存储器。

高速数据采集系统的设计

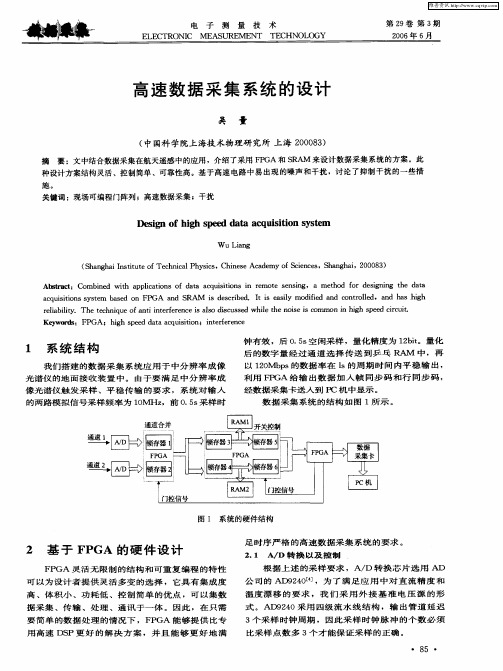

钟 有 效 ,后 0 5 空 闲 采 样 ,量 化 精 度 为 1 bt .s 2 i。量 化 后 的数 字 量 经 过 通 道 选 择 传 送 到 乒 乓 RAM 中 ,再 以 10 p 2 Mb s的 数 据 率 在 I 周 期 时 间 内 平 稳 输 出 , s的

利 用 F GA 给 输 出 数 据 加 入 帧 同 步 码 和 行 同 步 码 , P 经数 据采集 卡送入到 P C机 中 显 示 。 数 据 采 集 系 统 的 结 构 如 图 1所 示 。

摘 要 :文 中结合数据采集在航 天遥感 中的应用 ,介 绍了采用 F GA和 S A 来 设计数 据采集 系统 的方 案。此 P RM 种 设计 方案结构灵活 、控 制简单 、可靠性高 。基 于高速 电路 中易 出现 的噪声和 干扰 ,讨 论 了抑 制干扰 的一 些措

施。

关键词 :现场 可编程 门阵列 ;高速数据 采集 ;干扰

吴

量 :高速数 据采 集 系统 的设 计

由 于 通 道 数 只 有 2路 , 因 此 直 接 取 其 数 字 量 的

第3 期

高 1 b t 人 FP 2 i送 GA 中 ,利 用 FP GA 内部 的 资 源 生 成 锁存器 进 行 两 路 数 据 的合 并 ,这 样 提 高 了集 成 度 ,减 少 了 外 围 的 器 件 数 量 。两 路 锁 存 器 的 时 钟 均

— ~[ — 匝 ) —l = D

i —I/ 1 — — 墅 —◆ ^u —/ —

图 l 系统 的硬件结 构

2 基 于 F GA 的 硬 件 设 计 P

F PGA 灵 活 无 限 制 的 结 构 和 可 重 复 编 程 的 特 性 可 以 为 设 计 者 提 供 灵 活 多 变 的 选 择 ,它 具 有 集 成 度 高 、体 积 小 、 功 耗 低 、 控 制 简 单 的优 点 ,可 以集 数 据 采 集 、传 输 、处 理 、 通 讯 于 一 体 。 因 此 ,在 只 需 要 简 单 的数 据 处 理 的情 况 下 , F PGA 能 够 提 供 比专

基于嵌入式的多通道高速数据采集系统徐航

摘要:给出了一种多通道高速数据采集系统的设计方法,与传统的采用ISA 总线的采集卡相比,具有速度快、精度高和实时性好的特点。

本设计采用了比较常用的FPGA、高速AD9051、高速FIFO 等实现了高速采集系统,用DMA 控制技术将采集到的数据直接存储到高速FIFO 中,再由单片机将数据读出,并通过USB 端口传到上位机中,最后用LabVIEW 软件开发的界面进行数据的显示和分析。

实验表明该采集系统有通信速度快,可靠,增益可调,可连续采样等特点,更加适合应用于测试系统。

关键词:高速数据采集系统;FPGA;高速FIFO;LabVIEWAbstractAbstract:This paper presented a method of designing multi-channel high-speed data acquisition system ,which with faster speed,higher precision and better real-time compared to the traditional data acquisition card that use of the ISA bus .This design uses a relatively common FPGA,high-speed AD,high-speed FIFO and 51MCU to form a data acquisition system .The collect-ed data is stored directly into the high-speed FIFO by DMA control technology,then microcontroller read out data and transmit-ted to PC through the USB port ,PC display and process the data in the interface developed by LabVIEW .Experiments show that the acquisition system has fast communication speed,performance,adjustable gain,continuous sampling features and so on,it ’s more suitable for the test system.words Key words:High-Speed Data Acquisition system ;FPGA ;High Speed FIFO ;LabVIEW 中图分类号:TP73文献标识码:B文章编号:1001-9227(2013)-01-0148-03基于嵌入式的多通道高速数据采集系统徐航1,罗巍2(1四川大学电气信息学院四川成都,610065)(2浙江大学电气学院浙江杭州,310027)收稿日期:2012-10-25作者简介:徐航(1987-),男,硕士研究生,研究方向为电子技术应用。

高速ECT的数据采集系统设计

20 0 8年 9月

E T的 数 采 集 系 设 计 C 据 统

郑伟 军 , 王保 良, 志尧 ,李海 青 黄

( 江 大 学控 制科 学 与 工 程 学 系 工业 控 制 技 术 国 家重 点 实 验 室 浙 杭州 3 02 ) 10 7

摘

要: 针对 目前 电容层析成像 ( C ) E T 数据采集系统 中控制模块和通讯模块制 约数据采集速度 的瓶颈问题 , 文设 计并研制 本

了一 套基 于 D P处 理 器 和 U B . 术 的高 速 E T数 据 采 集 系 统 。该 系 统 以 D P处 理 器 ( D P28 N) S S 20技 C S A S 一18 为核 心 , 以 C L 辅 P D进

行 控制 ; 时采 用 U B . 术设 计 了 E T的 通讯 模 块 , 同 S 2 0技 C 实现 了 E T数 据 采集 系统 与上 位 机 的高 速通 讯 。实 验 测 试 表 明 , 系 C 该 统 在 保持 较 高 采 样精 度 的 同时 . 据 采 集 的 速度 大 为 提 高 , 秒 达 到 26 数 每 2 4幅 以 上 , 破 了 E T系统 数 据 采 集 速 度 的 瓶颈 , 足 突 C 满 了工 业应 用 的实 时 性 要求 。 关 键 词 : 容层 析 成 像 ; 据 采 集 系统 ;D P S 电 数 S ;U B

t a h aa a q ii o p e fo e 2 4 fa sp rs c n a e n a h e e h tte d t c u st n s e d o v r2 6 r me e e o d h b e c iv d,wh c ra h o g h o t n c i s ih b e k t r u h t e b tl e k e o aa a q st n s e d o fd t c uiii p e fECT s se a d c n me tte r a —i e u rme to h n sra rc se . o y tm n a e h e lt me rq ie n ft e idu t lp o e s s i Ke r s:ee t c lc p ctn e tmo a h y wo d lcr a a a i c o g p y;d t c u st n s se ;DS i a r aa a q iio y tm i P;US B

高速数据采集与存储系统的设计及实现

翅片,实现较好的散热效果。综合重量等因素考虑,当翅片 在重要区域布置间距为 5mm,非重要区域不布翅片时,方案 为最佳方案,模型和模块温度分布满足设计要求。

参考文献

[1] 李波 , 李科群 , 俞丹海 .Flotherm 软件在电子设备热 设计中的应用 [J]. 电子机械工程 ,2008(3):11-13. [2] 夏显忠 , 陶光勇 , 夏利锋 . 基于 CFD 的 FLOTHERM 在 机载液晶显示器热分析的应用 [J]. 电子机械工程 ,2007(3):7-10. [3] 李明东 . 利用 CFD 数值仿真技术确定电子设备风道 特性 [J]. 安全与电磁兼容 ,2003(3):16-18.

2016 年第 5 期

信息与电脑 China Computer&Communication

软件开发与应用

高速数据采集与存储系统的设计及实现

向 琛 陈翠云

(中国兵器装备集团 ( 成都 ) 火控技术中心,四川 成都 611731)

摘 要:随着信息技术的不断发展,促使数据采集系统在人们日常生产和生活中的应用越来越广泛。在实际工作当中, 有效利用数据采集系统可以采集、监控并记录生产现场的工艺参数信息,进而起到降低企业实际生产成本与全面提高产 品质量的作用,从而为开展具体工作提供重要数据参照。笔者首先对数据采集技术的基本情况进行了介绍,再对数据采 集单元电路的设计进行了阐述与分析,最后对如何设计存储系统的 FPGA 程序进行了探索与研究,以期能够提高该系统实 际应用效率。 关键词:数据采集;存储系统;设计;实现 中图分类号:TP274.2 文献标识码:A 文章编号:1003-9767(2016)05-085-02

采取高速数据采集与存储系统可以在实际科研工作中获 取到海量的有效信息,因此,其是研究瞬间物理的重要工具。 高速数据采集与存储系统当前主要应用在气象预报、预测地 震等领域,而且现场信号还具有一些较为突出的特点,如运 算量较大、实时性较强等。因此,受到相关工作人员的高度 重视 。

高速数据采集与处理系统设计与验证研究

高速数据采集与处理系统设计与验证研究摘要:高速数据采集与处理系统在许多领域中具有重要的应用,如通讯、工业控制、医疗诊断等。

本文旨在通过设计与验证研究,探讨高速数据采集与处理系统的各个组成部分及其相互之间的关系,以及如何优化系统性能。

该研究可为高速数据采集与处理系统的设计与应用提供理论依据和实践指导。

1. 引言高速数据采集与处理系统是指能够以高速率采集大量数据并进行实时处理的系统。

在许多领域中,如科学研究、工业控制、医疗诊断等,高速数据采集与处理系统都起着关键作用。

然而,由于数据量大、采样频率高,对系统的设计与验证提出了很大的挑战。

2. 高速数据采集系统设计高速数据采集系统的设计包括硬件和软件两个方面。

硬件方面主要包括采集设备的选择和配置、模拟电路设计、高速采样模块的设计等。

软件方面主要包括数据采集控制程序的设计和开发、数据传输协议的制定等。

2.1 采集设备的选择和配置在设计高速数据采集系统时,首先需要选择合适的采集设备。

常见的采集设备有采集卡、采集模块和数据采集仪器等。

根据实际需求,选择具有高采样率、高精度和稳定性的采集设备。

2.2 模拟电路设计模拟电路设计是高速数据采集系统设计的重要组成部分。

通过合理设计模拟电路,可以保证从传感器或信号源输入到采集设备的信号质量。

常见的模拟电路设计技术包括放大器设计、滤波器设计和抗干扰设计等。

2.3 高速采样模块的设计高速采样模块是高速数据采集系统中的核心部分,它负责将模拟输入信号转换为数字信号,并通过总线接口传输给处理部分。

高速采样模块的设计需要考虑采样率、分辨率、存储容量等因素,并采用合适的数模转换器和存储器。

3. 高速数据处理系统设计高速数据处理系统设计主要包括数据接收、数据处理和数据存储三个环节。

3.1 数据接收数据接收是指将高速采样模块采集到的数据传输到数据处理部分。

在数据接收过程中,需要考虑数据传输速率、数据稳定性和数据完整性等问题。

常见的数据传输技术有PCIe、USB和以太网等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

124高速数据采集系统院系:物理学院

高速数据采集系统

磁约束聚变中子能谱仪的数字化测量平台和数字化信号处理系统项目课题,聚变等离子体中子能谱测量与诊断及相关磁流体模式研究,2008CB717803)计划专项国内配套项目课题,托卡马克等离子体诊断技术研究,2009GB107001)计划专项国内配套项目课题,快粒子驱动磁流体模式的研究,2013GB106004三年内利用该仪器作为主要科研手段发表学术论文(三大检索) 2 篇,其中代表论文:论文题目期刊名年 卷(期)起止页码

A digital delay-line-shaping method for pulse shape discrimination in stilbene neutron detector and application to fusion neutron measurement at HL-2A tokamak Nucl. Instr. and Meth. Phys. Res. A 20126877-13。