51单片机IO口

51单片机IO口工作原理

51单片机IO口工作原理一、概述51单片机是一种广泛应用于嵌入式系统的微控制器,其IO口是其最基本和重要的功能之一。

IO口可以用于输入和输出信号,实现与外部设备的数据交互。

本文将详细介绍51单片机IO口的工作原理。

二、IO口的结构51单片机的IO口由多个引脚组成,每个引脚都有特定的功能和工作模式。

通常,一个IO口引脚可以配置为输入模式或输出模式,具体的配置由相应的寄存器控制。

三、IO口的输入模式当一个IO口引脚配置为输入模式时,它可以接收外部设备发送的信号。

在输入模式下,引脚的电平可以是高电平(1)或低电平(0),这取决于外部设备发送的信号。

在51单片机中,可以通过P1口和P3口来配置引脚为输入模式。

当一个引脚配置为输入模式时,相应的寄存器会设置为1,表示该引脚为输入状态。

此时,我们可以通过读取相应的寄存器值来获取引脚的电平状态。

四、IO口的输出模式当一个IO口引脚配置为输出模式时,它可以向外部设备发送信号。

在输出模式下,引脚的电平可以是高电平(1)或低电平(0),这取决于我们设置的值。

在51单片机中,可以通过P0口、P1口、P2口和P3口来配置引脚为输出模式。

当一个引脚配置为输出模式时,相应的寄存器会设置为0,表示该引脚为输出状态。

此时,我们可以通过写入相应的寄存器值来控制引脚的电平状态。

五、IO口的工作原理在51单片机中,IO口的工作原理是通过寄存器的读写操作来实现的。

通过读取或写入相应的寄存器值,我们可以配置引脚的工作模式和控制引脚的电平状态。

对于输入模式,我们可以通过读取相应的寄存器值来获取引脚的电平状态。

通过读取P1口和P3口的寄存器值,我们可以判断引脚的电平是高电平还是低电平。

对于输出模式,我们可以通过写入相应的寄存器值来控制引脚的电平状态。

通过写入P0口、P1口、P2口和P3口的寄存器值,我们可以将引脚的电平设置为高电平或低电平。

六、IO口的应用场景51单片机的IO口广泛应用于各种嵌入式系统中,如电子设备、家用电器、工业控制等。

51单片机IO引脚IO口工作原理

51单片机IO引脚IO口工作原理一、IO引脚的基本特性1.输入与输出:IO引脚可以配置为输入(接收外部信号)或输出(发送信号到外部设备)。

2. 高低电平:IO引脚可以输出高电平(通常为Vcc电压)或低电平(通常为接地GND电压)。

3.上拉与下拉:IO引脚可以通过上拉电阻或下拉电阻实现电平的稳定。

4. 悬空状态:未配置输入的IO引脚可能处于悬空状态(floating),容易受到噪声的干扰。

二、IO口的工作原理1.寄存器配置:通过对相应的寄存器进行配置,可以选择IO引脚的工作模式(输入或输出)、电平(高或低)、上拉或下拉等。

2.IO端口的控制:通过对控制寄存器进行设置,可以使IO引脚产生相应的电平信号,控制外部设备的操作。

3.输入输出驱动能力:IO引脚的输出能力决定了其能够驱动的外部设备的负载能力。

对于较重的负载,需要考虑使用缓冲电路或者外部驱动芯片。

三、IO口的配置与操作1.选择IO引脚功能:通过寄存器配置,将IO引脚配置为输入模式(将输入电平传递给芯片内部)或输出模式(将芯片内部的电平输出到外部设备)。

2.设置电平状态:对于输出模式的引脚,可以通过寄存器来设置输出电平的状态,使其输出高电平或低电平。

3.上拉与下拉电阻:通过配置相关寄存器,可以启用上拉电阻(使引脚在悬空状态时拉高到高电平)或下拉电阻(使引脚在悬空状态时拉低到低电平)。

四、IO端口的应用1.输入:将外部设备的信号输入到IO引脚,通过编程来实现对信号的判断和处理。

例如,读取按键的状态、读取传感器的数据等。

2.输出:将芯片内部产生的信号输出到外部设备,用于控制和驱动外部设备的操作。

例如,控制LED灯的亮灭、控制继电器的开关等。

3.通信:通过IO引脚与其他设备(例如外围设备、传感器、通信模块等)进行通信。

4.扩展IO口:通过外部的IO扩展芯片或者接口芯片,可以扩展更多的IO口。

总结:51单片机的IO口是其与外部设备通信的接口,通过配置相关寄存器来选择引脚的工作模式、电平和电阻状态。

51单片机IO口

存器可实现对全部内部资源的运行操作。

软件读/写 CPU内核 硬件映射 外围应用模块 (功能部件)

SFR(21)

用户编程

自动对应

外 界

单片机学习寄语——实践出真知!

天府电子工作室

技术支持:

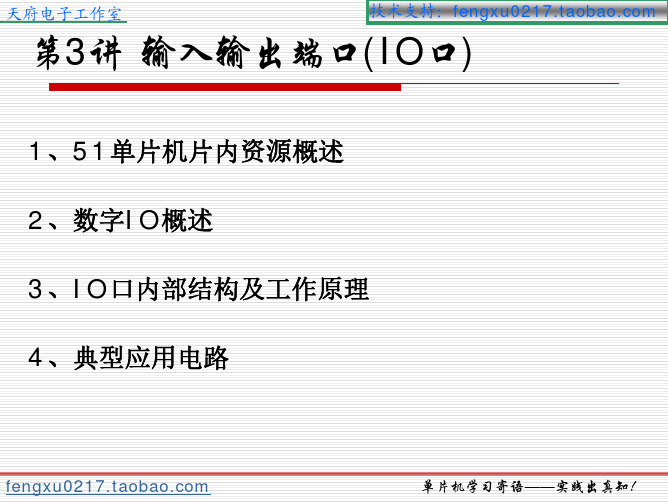

1、51单片机片内资源概述

与MCS-51单片机相关的21个SFR:

单片机学习寄语——实践出真知!

天府电子工作室

技术支持:

4、典型应用电路

输出引脚的2种不同的连接方式:

P2. 0 P2. 0

拉电流方式

灌电流方式

注意:在实际使用时,应尽量采用灌电流方式,而不要采

用拉电流方式,这样可以提高系统的负载能力和可靠性。

P1口

(P1端口)

(P0端口)

P0口

(P3端口) (P2端口)

P3口

P2口

单片机学习寄语——实践出真知!

天府电子工作室

技术支持:

2、数字I/O口 概述

P0端口(B0H)

P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0 B7H B6H B5H B4H B3H B2H B1H B0H

单片机学习寄语——实践出真知!

天府电子工作室

技术支持:

4、典型应用电路

输入引脚有2种不同的连接方式

上拉默认高电平

下拉默认低电平

单片机学习寄语——实践出真知!

天府电子工作室

技术支持:

单片机学习寄语——实践出真知!天府 Nhomakorabea子工作室

技术支持:

2、数字I/O口 概述

AT89S51单片机总共有P0、P1、P2、P3 四个8位并 行双向输入/输出端口。 “引脚”与“端口”这两个概念之间的关系就是一种“个体” 与“整体”的关系。

51单片机、AVR单片机和PIC单片机IO口的操作

51 单片机、AVR 单片机和PIC 单片机IO 口的操作

51 单片机、AVR 单片机和PIC 单片机IO 口结构的均不同,导致了IO

口操作也不同。

操作单片机IO 口的目的是让单片机的管脚输出逻辑电平和读取单片机管脚的逻辑电平。

下面我们来看看51 单片机、AVR 单片机和PIC

单片机IO 口的操作的方法。

一.51 单片机IO 口的操作

51 单片机IO 口的结构比较简单,每个IO 口只有一个IO 口寄存器Px,而且这个寄存器可以位寻址,操作起来是所有单片机里最简单的,可以直接进行

总线操作也可以直接进行位操作,这也是51 单片机之所以成为经典的原因之一。

下例的运行坏境为Keil 软件,器件为AT89S52。

#i nclude

sbit bv=P2;//定义位变量,关联P2.0 管脚。

sbit 是C51 编译器特有的数据类型

int main(void)

{

unsigned char pv;。

很全的51单片机IO端口详解(带图)

80C51的I/O端口结构及应用特性一,I/O端口的结构1,锁存器加引脚的典型结构80C51的I/O端口都有内部总线实现操作控制。

P0-P3四个I/O 口都可以做普通I/O口,因此,要求具有输出锁存功能。

内部总线有事分时操作,因此每个I/O端口都有相应的锁存器。

然而I/O端口又是外部的输入/输出通道,必须有相应的引脚,故形成了I/O端口的锁存器加引脚的典型结构。

2,I/O口的复用功能(1)I/O口的总线复用。

80C51在使用并行总线扩展时,P0口可作为数据总线口和低8位地址总线口,这是,P0为三态双向口。

P0口输出总线的地址数据信号,P2口输出高8位地址信号。

(2)I/O口的功能复用。

I/O口的P3为功能复用的I/O端口。

端口有复用输出的控制端;引脚也有复用输入的控制端。

3,准双向结构P0,P1,P2,P3口做普通I/O口使用时,都是准双向口结构。

准双向口的典型结构见P1口位结构图。

准双向口的输入操作和输出操作本质不同,输入操作时读引脚状态;输出操作时对口锁存器的写入操作。

有口锁存器和引脚电路可知:当有内部总线对只1或只0时,锁存器的0、1状态立即反应到引脚上。

但是输入操作(读引脚)时,如果口锁存器的状态为0,引脚被嵌位在0状态,导致无法读出引脚的高电平输入。

二,I/O端口的应用特性1,引脚的自动识别。

无论P0,P2口的总线复用,还是P3口的功能复用,内部资源会自动选择,不需要通过指令的状态选择。

2,口锁存器的读、该、写操作。

许多涉及到I/O端口的操作,只是涉及口锁存器的读出、修改、写入的操作。

这些指令都是一些逻辑运算指令、置位/清除指令、条件转移指令以及将I/O口作为目的地址的操作指令。

3,读引脚的操作指令。

如果某个I/O口被指定为源操作数,则为读引脚的操作指令。

例如,执行MOV A,P1时,P1口的引脚状态传送到累加器中,执行MOV P1,A是,指令则将累加器的内容传送到P1口锁存器中。

4,准双向口的使用。

51单片机IO口工作原理

51单片机IO口工作原理51单片机(英文名为8051 Microcontroller)是一种由Intel公司于1980年推出的8位单片机,广泛应用于嵌入式系统中。

作为一种高性能、低功耗的单片机,其周围有多个IO口(Input/Output ports),可以用来实现数字输入、输出、模拟输入、输出等功能。

下面将详细介绍51单片机IO口的工作原理。

1.51单片机的IO口介绍51单片机共有4个8位的IO口,依次为P0、P1、P2和P3、每个IO 口都是一个8位的寄存器,称为端口寄存器(port register),用于和外部设备进行数据通信。

其中,P0是一个具有双重输入和输出特性的端口,可以配置为输入口或输出口;P1和P3是纯输出端口;P2是输入输出混合端口。

2.IO口的工作模式IO口的工作模式由P0、P1、P2和P3的寄存器位来配置。

每个IO口的寄存器位都有对应的功能和控制位,通过设置这些位可以控制IO口的工作模式和输出状态。

2.1输入模式在输入模式下,IO口作为输入口,接受来自外部器件的信号。

通过将对应的寄存器位设置为1,可以将IO口配置为输入模式。

在输入模式下,端口寄存器的位对应的为悬空状态,可以通过主动上拉或下拉方法来确保IO口的状态。

2.2输出模式在输出模式下,IO口作为输出口,通过控制寄存器位的值可以输出高电平或低电平信号。

将对应的寄存器位设置为0,可以将IO口配置为输出模式。

在输出模式下,直接修改端口寄存器的位即可改变IO口的输出状态。

对于纯输出端口,即P1和P3,更方便地改变IO口的状态可以通过直接操作对应的位。

2.3产生中断IO口还可以通过设置为中断产生源的方式来实现中断功能。

在输入模式下,将对应的寄存器位设置为1,即可配置IO口为中断输入。

当IO口检测到中断触发条件(例如边沿触发、电平触发等),会触发相应的中断服务程序(ISR)。

3.IO口的读取和写入操作为了读取和写入IO口的状态,可以直接访问相应的寄存器。

MCS-51单片机IO口详解

单片机IO口结构及上拉电阻MCS-51有4组8位I/O口:P0、P1、P2和P3口,P1、P2和P3为准双向口,P0口则为双向三态输入输出口,下面我们分别介绍这几个口线。

一、P0口和P2口图1和图2为P0口和P2口其中一位的电路图。

由图可见,电路中包含一个数据输出锁存器(D触发器)和两个三态数据输入缓冲器,另外还有一个数据输出的驱动(T1和T2)和控制电路。

这两组口线用来作为CPU与外部数据存储器、外部程序存储器和I/O扩展口,而不能象P1、P3直接用作输出口。

它们一起可以作为外部地址总线,P0口身兼两职,既可作为地址总线,也可作为数据总线。

图1 单片机P0口内部一位结构图图2 单片机P0口内部一位结构图P2口作为外部数据存储器或程序存储器的地址总线的高8位输出口AB8-AB15,P0口由ALE选通作为地址总线的低8位输出口AB0-AB7。

外部的程序存储器由PSEN信号选通,数据存储器则由WR和RD读写信号选通,因为2^16=64k,所以MCS-51最大可外接64kB的程序存储器和数据存储器。

二、P1口图3为P1口其中一位的电路图,P1口为8位准双向口,每一位均可单独定义为输入或输出口,当作为输入口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至"1",此时该口输出为1,当0写入锁存器,Q(非)=1,T2导通,输出则为0。

图3 单片机P2口内部一位结构图作为输入口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,正因为这个原因,所以P1口常称为准双向口。

需要说明的是,作为输入口使用时,有两种情况:1.首先是读锁存器的内容,进行处理后再写到锁存器中,这种操作即读—修改—写操作,象JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。

2.读P1口线状态时,打开三态门G2,将外部状态读入CPU。

51单片机io口工作的基本原理

51单片机io口工作的基本原理51单片机是一种广泛应用于嵌入式系统开发的微控制器,其基本原理是通过控制输入/输出(I/O)口的电平状态来实现与外部设备的连接与交互。

单片机的I/O口被称为通用I/O口(General Purpose I/O,GPIO),可以通过设置其输入与输出模式以及控制电平状态来与外部设备进行数据的传输与控制。

在51单片机中,GPIO口可以进行两种模式的设置:输入模式和输出模式。

在输入模式下,GPIO口可以将外部设备的电平状态作为输入信号接收,并将该信号传送至单片机内部进行处理。

在输出模式下,单片机可以通过控制GPIO口的电平状态向外部设备发送数据或控制信号。

当GPIO口设置为输入模式时,单片机内部会初始化一个输入缓冲区,用于存储外部设备传入的电平信号。

当外部设备改变电平状态时,单片机会及时检测到,并将相应的电平状态记录在输入缓冲区中。

通过读取输入缓冲区的数值,单片机可以获取外部设备传入的数据。

这样,单片机就能够实现与外部设备的数据交互。

当GPIO口设置为输出模式时,单片机内部会初始化一个输出缓冲区,用于存储将要发送至外部设备的数据。

根据所需的传输方式,单片机可以通过改变输出缓冲区的数值来控制GPIO口的电平状态。

当输出缓冲区的数值发生改变时,单片机会通过输出电路将该数值转换为相应的电平状态,从而将数据或控制信号送至外部设备。

除了设置输入/输出模式以及控制电平状态之外,单片机还可以对GPIO口进行中断配置以及上下拉电阻的设置。

中断配置可以实现在特定事件发生时自动跳转至相应的中断服务函数,从而实现对外部设备的实时响应。

上下拉电阻则可以提供电平稳定性,防止输入口因为无输入信号而漂移到不确定状态。

综上所述,51单片机的I/O口工作基于设置输入/输出模式以及控制电平状态,通过与外部设备进行电平交互来实现数据的传输与控制。

通过合理配置中断和上下拉电阻,单片机可以实现高效稳定的IO口工作,为嵌入式系统开发提供强大的功能与灵活性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

那么这个多路选择开关就是用于选择是做为普通I/O口使用还是作为‘数据/地址’总线使用的选择开关了。

大家看上图,当多路开关与下面接通时,P0口是作为普通的I/O口使用的,当多路开关是与上面接通时,P0口是作为‘地址/数据’总线使用的。

输出驱动部份:从上图中我们已看出,P0口的输出是由两个MOS管组成的推拉式结构,也就是说,这两个MOS管一次只能导通一个,当V1导通时,V2就截止,当V2导通时,V1截止。

与门、与非门:这两个单元电路的逻辑原理我们在第四课数字及常用逻辑电路时已做过介绍,不明白的同学请回到第四节去看看。

前面我们已将P0口的各单元部件进行了一个详细的讲解,下面我们就来研究一下P0口做为I/O口及地址/数据总线使用时的具体工作过程。

1、作为I/O端口使用时的工作原理P0口作为I/O端口使用时,多路开关的控制信号为0(低电平),看上图中的线线部份,多路开关的控制信号同时与与门的一个输入端是相接的,我们知道与门的逻辑特点是“全1出1,有0出0”那么控制信号是0的话,这时与门输出的也是一个0(低电平),与让的输出是0,V1管就截止,在多路控制开关的控制信号是0(低电平)时,多路开关是与锁存器的Q非端相接的(即P0口作为I/O口线使用)。

P0口用作I/O口线,其由数据总线向引脚输出(即输出状态Output)的工作过程:当写锁存器信号CP 有效,数据总线的信号→锁存器的输入端D→锁存器的反向输出Q非端→多路开关→V2管的栅极→V2的漏极到输出端P0.X。

前面我们已讲了,当多路开关的控制信号为低电平0时,与门输出为低电平,V1管是截止的,所以作为输出口时,P0是漏极开路输出,类似于OC门,当驱动上接电流负载时,需要外接上拉电阻。

下图就是由内部数据总线向P0口输出数据的流程图(红色箭头)。

P0口用作I/O口线,其由引脚向内部数据总线输入(即输入状态Input)的工作过程:数据输入时(读P0口)有两种情况1、读引脚读芯片引脚上的数据,读引脚数时,读引脚缓冲器打开(即三态缓冲器的控制端要有效),通过内部数据总线输入,请看下图(红色简头)。

2、读锁存器通过打开读锁存器三态缓冲器读取锁存器输出端Q的状态,请看下图(红色箭头):在输入状态下,从锁存器和从引脚上读来的信号一般是一致的,但也有例外。

例如,当从内部总线输出低电平后,锁存器Q=0,Q非=1,场效应管T2开通,端口线呈低电平状态。

此时无论端口线上外接的信号是低电乎还是高电平,从引脚读入单片机的信号都是低电平,因而不能正确地读入端口引脚上的信号。

又如,当从内部总线输出高电平后,锁存器Q=1,Q非=0,场效应管T2截止。

如外接引脚信号为低电平,从引脚上读入的信号就与从锁存器读入的信号不同。

为此,8031单片机在对端口P0一P3的输入操作上,有如下约定:为此,8051单片机在对端口P0一P3的输入操作上,有如下约定:凡属于读-修改-写方式的指令,从锁存器读入信号,其它指令则从端口引脚线上读入信号。

读-修改-写指令的特点是,从端口输入(读)信号,在单片机内加以运算(修改)后,再输出(写)到该端口上。

下面是几条读--修改-写指令的例子。

这样安排的原因在于读-修改-写指令需要得到端口原输出的状态,修改后再输出,读锁存器而不是读引脚,可以避免因外部电路的原因而使原端口的状态被读错。

P0端口是8031单片机的总线口,分时出现数据D7一D0、低8位地址A7一AO,以及三态,用来接口存储器、外部电路与外部设备。

P0端口是使用最广泛的I/O端口。

2、作为地址/数据复用口使用时的工作原理在访问外部存储器时P0口作为地址/数据复用口使用。

这时多路开关‘控制’信号为‘1’,‘与门’解锁,‘与门’输出信号电平由“地址/数据”线信号决定;多路开关与反相器的输出端相连,地址信号经“地址/数据”线→反相器→V2场效应管栅极→V2漏极输出。

例如:控制信号为1,地址信号为“0”时,与门输出低电平,V1管截止;反相器输出高电平,V2管导通,输出引脚的地址信号为低电平。

请看下图(兰色字体为电平):反之,控制信号为“1”、地址信号为“1”,“与门”输出为高电平,V1管导通;反相器输出低电平,V2管截止,输出引脚的地址信号为高电平。

请看下图(兰色字体为电平):可见,在输出“地址/数据”信息时,V1、V2管是交替导通的,负载能力很强,可以直接与外设存储器相连,无须增加总线驱动器。

P0口又作为数据总线使用。

在访问外部程序存储器时,P0口输出低8位地址信息后,将变为数据总线,以便读指令码(输入)。

在取指令期间,“控制”信号为“0”,V1管截止,多路开关也跟着转向锁存器反相输出端Q非;CPU自动将0FFH(11111111,即向D锁存器写入一个高电平‘1’)写入P0口锁存器,使V2管截止,在读引脚信号控制下,通过读引脚三态门电路将指令码读到内部总线。

请看下图如果该指令是输出数据,如MOVX @DPTR,A(将累加器的内容通过P0口数据总线传送到外部RAM 中),则多路开关“控制”信号为‘1’,“与门”解锁,与输出地址信号的工作流程类似,数据据由“地址/数据”线→反相器→V2场效应管栅极→V2漏极输出。

如果该指令是输入数据(读外部数据存储器或程序存储器),如MOVX A,@DPTR(将外部RAM某一存储单元内容通过P0口数据总线输入到累加器A中),则输入的数据仍通过读引脚三态缓冲器到内部总线,其过程类似于上图中的读取指令码流程图。

通过以上的分析可以看出,当P0作为地址/数据总线使用时,在读指令码或输入数据前,CPU自动向P0口锁存器写入0FFH,破坏了P0口原来的状态。

因此,不能再作为通用的I/O端口。

大家以后在系统设计时务必注意,即程序中不能再含有以P0口作为操作数(包含源操作数和目的操作数)的指令。

二、P1端口的结构及工作原理P1口的结构最简单,用途也单一,仅作为数据输入/输出端口使用。

输出的信息有锁存,输入有读引脚和读锁存器之分。

P1端口的一位结构见下图.由图可见,P1端口与P0端口的主要差别在于,P1端口用内部上拉电阻R代替了P0端口的场效应管T1,并且输出的信息仅来自内部总线。

由内部总线输出的数据经锁存器反相和场效应管反相后,锁存在端口线上,所以,P1端口是具有输出锁存的静态口。

由上图可见,要正确地从引脚上读入外部信息,必须先使场效应管关断,以便由外部输入的信息确定引脚的状态。

为此,在作引脚读入前,必须先对该端口写入l。

具有这种操作特点的输入/输出端口,称为准双向I/O口。

8051单片机的P1、P2、P3都是准双向口。

P0端口由于输出有三态功能,输入前,端口线已处于高阻态,无需先写入l后再作读操作。

P1口的结构相对简单,前面我们已详细的分析了P0口,只要大家认真的分析了P0口的工作原理,P1口我想大家都有能力去分析,这里我就不多论述了。

单片机复位后,各个端口已自动地被写入了1,此时,可直接作输入操作。

如果在应用端口的过程中,已向P1一P3端口线输出过0,则再要输入时,必须先写1后再读引脚,才能得到正确的信息。

此外,随输入指令的不同,H端口也有读锁存器与读引脚之分。

三、P2端口的结构及工作原理:P2端口的一位结构见下图:由图可见,P2端口在片内既有上拉电阻,又有切换开关MUX,所以P2端口在功能上兼有P0端口和P1端口的特点。

这主要表现在输出功能上,当切换开关向下接通时,从内部总线输出的一位数据经反相器和场效应管反相后,输出在端口引脚线上;当多路开关向上时,输出的一位地址信号也经反相器和场效应管反相后,输出在端口引脚线上。

对于8031单片机必须外接程序存储器才能构成应用电路(或者我们的应用电路扩展了外部存储器),而P2端口就是用来周期性地输出从外存中取指令的地址(高8位地址),因此,P2端口的多路开关总是在进行切换,分时地输出从内部总线来的数据和从地址信号线上来的地址。

因此P2端口是动态的I/O端口。

输出数据虽被锁存,但不是稳定地出现在端口线上。

其实,这里输出的数据往往也是一种地址,只不过是外部RAM的高8位地址。

在输入功能方面,P2端口与P0和H端口相同,有读引脚和读锁存器之分,并且P2端口也是准双向口。

可见,P2端口的主要特点包括:①不能输出静态的数据;②自身输出外部程序存储器的高8位地址;②执行MOVX指令时,还输出外部RAM的高位地址,故称P2端口为动态地址端口。

即然P2口可以作为I/O口使用,也可以作为地址总线使用,下面我们就不分析下它的两种工作状态。