飞思卡尔单片机增强型定时器计数器ECT

增强型定时器ECT模块

队列方式

➢ TCx 与 TCxH 形成了一个类似先进先出的 队列,每个捕捉结果从 TCx 进入,然 后随 着下一个捕捉结果的到来移入 TCxH。

➢ 程序可以从 TCxH 取得结果,也可以直接 从 TCx 取得捕捉结果。

ECT控制寄存器1(TSCR1)

必须设置TSCR1才可以使主定时器工作,需要在ECT模块初始化 时就设置好。

➢TEN=1:主定时器使能。0=主定时器禁止,进入低功耗状态。 ➢TSWAI=0:等待模式时主定时器继续工作,方便调试。0= 停止工作。 ➢TSFRZ=0:冻结模式时主定时器继续工作。0=停止工作。 ➢TFFCA=0:自动清除标志位。1=手动清除。

增强型定时器ECT模块

MC9S12系列单片机增强型定时器模块是在标准定时 器模块的基础上添加了新的功能。

定时器的核心是一个16位的可编程计数器,计数的 频率可以通过分频来调整。

用途很多

➢ 普通定时器的工作,例如脉冲计数、定时等 ➢ 可以用来测量输入的脉冲宽度 ➢ 产生我们需要的脉冲波形。

ECT模块的组成:

有8个输入捕捉输出比较通道。共有8个外部引 脚,分别为IOC0—IOC7,与PORTT复用。

通过选择TIOS寄存器的IOSx位可以选择是输出 比较还是输入捕捉。

对于输入捕捉:

➢ 道

不带缓冲的输入捕捉通道

➢ 8个输入捕捉,其中4个(PT4~PT7)带有 一个捕捉寄存器用来记录管脚上电平变化 时自由计数器的锁存值。

➢ 原理是:输出比较寄存器的值和计数器的值每 隔4个总线周期比较一次,当两个值相等的时候, 会在该通道的引脚上输出预先规定的电平。

➢ 如果输出比较中断允许,还会产生一个硬件的

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置手把手教你写S12XS128程序--PWM模块介绍该教程以MC9S12XS128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。

每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM 计数器为0时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

7、有4个时钟源可供选择(A、SA、B、SB),他们提供了一个宽范围的时钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位P WMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的P WMEx 位置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL 寄存器中的CONxx置1),那么)使能相应的16位PWM 输出通道是由PWMEx 的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道 1 的使能位控制PWM 的输出。

飞思卡尔单片机 ECT学习资料

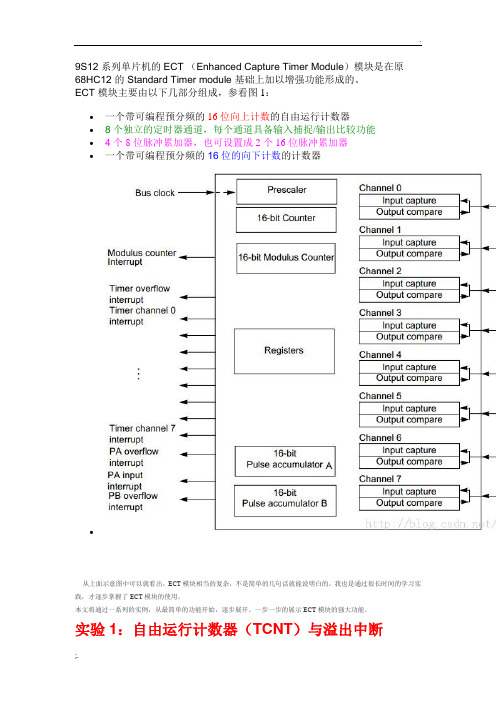

9S12 系列单片机的ECT (Enhanced Capture Timer Module)模块是在原68HC12 的 Standard Timer module 基础上加以增强功能形成的。

ECT 模块主要由以下几部分组成,参看图1:•一个带可编程预分频的16位向上计数的自由运行计数器•8个独立的定时器通道,每个通道具备输入捕捉/输出比较功能•4个8位脉冲累加器,也可设置成2个16位脉冲累加器•一个带可编程预分频的16位的向下计数的计数器•从上面示意图中可以就看出,ECT 模块相当的复杂,不是简单的几句话就能说明白的。

我也是通过很长时间的学习实践,才逐步掌握了ECT模块的使用。

本文将通过一系列的实例,从最简单的功能开始,逐步展开。

一步一步的展示ECT 模块的强大功能。

实验1:自由运行计数器(TCNT)与溢出中断自由运行计数器(TCNT)也称为自由运行主定时器,是一个16位的计数器,可以说是ECT的核心。

在系统复位时,这个自由运行计数器的初值为$0000。

当ECT 模块运行时,自由运行计数器从$0000~$FFFF 循环递增计数。

当计数器溢出复零时,会置位中断标志。

利用这个计数器,可以产生一个周期的中断信号。

TCNT 的输入时钟也是可以选择的,图2 给出了TCNT 的时钟源的示意图。

可以看出,TCNT的输入时钟可以来源于总线时钟、总线时钟经过预分频、外部引脚输入的脉冲、外部引脚输入脉冲经过脉冲累加器分频这四种选择。

当然,选择哪个时钟源其实就是在程序中设置一下相应的寄存器这么简单。

了解了上面的介绍,就可以开始本文的第一个例子了,这个例子非常简单,将BUS CLOCK 分频后作为TCNT 的输入时钟,使能TCNT 溢出中断。

在开始代码之前,还需要介绍几个程序中用到的寄存器。

TCNT寄存器(Timer Count Register)这个寄存器其实已经介绍过了,它是一个16 位的只读寄存器。

在每个时钟输入下计数值会自动加1,当计数值为0xFFFF 后下一个时钟脉冲会使计数器溢出为0x0000。

飞思卡尔16位单片机寄存器总结

一、输入输出端口寄存器I/O接口包括PORTA、B、E、K、T、S、M、P、H、J、AD。

其中PORTA、B、E、K属于复用扩展总线接口,单片机在扩展方式下工作时,作为总线信号。

1、PORTT、S、M、P、H、JI/O寄存器PTx如果对应位数据方向寄存器DDRx为“0”,输入,读取该寄存器返回引脚值;“1”,输出,读取该寄存器返回I/O寄存器的内容。

数据方向寄存器DDRx决定对应引脚为输出还是输入,“0”为输入,“1”为输出,复位后,默认为输入。

上拉/下拉使能寄存器PERx选择使用内置上拉/下拉器件,“1”允许,“0”禁用。

中断使能寄存器PIExPORTP、H、J三个端口具有中断功能。

“1”对应引脚允许中断,“0”禁止,复位后,所有端口中断关闭。

中断标志寄存器PIFxPORTP、H、J三个端口具有中断功能。

“1”对应引脚允许中断,“0”禁止,复位后,所有端口中断关闭。

2、PORTA、B、E、KI/O寄存器Px若某端口的引脚被定义为输出,写入I/O寄存器中的数值会从对应引脚输出;输入,通过I/O寄存器读取对应引脚电平。

数据方向寄存器DDRx决定对应引脚为输出还是输入,“0”为输入,“1”为输出,复位后,默认为输入。

PORTE最低两位只能为输入。

上拉电阻控制寄存器PERx第7、4、1、0位分别控制K、E、B、A端口,“1”允许使用对应端口的上拉电阻,“0”禁止,复位后,PK、PE端口使能,PB、PA禁止。

二、中断系统中断控制寄存器INTCR第7位IRQE,中断电平/边沿有效选择,0为低电平有效,1为下降沿有效;第6位IRQEN,外部中断IRQ中断请求使能,0关闭,1允许。

三、PWM模块PWM允许寄存器PWME对应每一位PWMEx,1启动输出,0停止输出,读写任意时刻。

PWM预分频时钟选择寄存器PWMPRCLK为Clock A和B选择独立的预分频因子,读写任意时刻。

Clock B对应6、5、4三位,Clock A对应2、1、0三位,分别可以实现2、4、8、16、32、64、128分频。

飞思卡尔单片机中断

在CW4.6环境下,中断编程主要有两种方式: 第一种是使用“interrupt‖关键字,―interrupt‖关键字是一个非标准ANSI-C的关键字,因此,它不能被所有ANSI-C编译器厂商所支持 。同样,对不同的编译器,interrupt‖关键字的用法可能会改变。“interrupt‖关键字同样会提示编译器下面的函数是一个中断服务例程。 例: void interrupt 20 SCI0_ISR(void); 其中,interrupt表示该函数为终端服务程序,后面的20表示中断号20,在这里SCI0的中断向量号就是20. 这种方法写起来非常简单,但是,在S12单片机实际使用中,中断号并没有在手册中给出,通常需要自己在中断向量表中从上往下 数出来,或者根据中断向量计算得到,很容易出错。 于是有了第二种方法: 在ISR程序之前,使用符号“#pragma TRAP_PROC‖,TRAP_PROC 提示编译器下面的函数是中断服务例程。编译器会用一个特 殊的中断返回指令来结束这个函数。 此时,中断函数的书写如下所示: #pragma TRAP_PROC void SCI0_ISR(void){ ...} 这时候编译器不知道这个ISR指向那个中断向量,我们需要在链接文件即:prm文件中指定之。 使用 VECTOR命令来实现中断向量与ISR程序的连接。 例:VECTOR 0 _Startup //这是系统默认prm文件中自带的,即复位后0号中断即复位中断的ISR为_Startup() 我们可以这样写: VECTOR 20 SCI0_ISR //指定中断号 或者 VECTOR ADDRESS 0xFFD6 SCI0_ISR //直接指定中断向量地址 注:使用#pragma TRAP_PROC与修改prm文件的方法,在中断服务子程序的结尾处必须要手动加入返回主程序的指令,包括取 出堆栈、中断返回两个步骤。 在S12单片机中,可以写作 asm { pula; rti;} 尾注: 两种方法所写的中断服务子程序必须被放在非分页存储区内,即non_blanked code seg. 其中一种常用的方法是在服务子程序前声明://下面代码放在NON_BANKED区 #pragma CODE_SEG NON_BANKED 在中断程序后声明://下面内容按默认放置 #pragma CODE_SEG DEFAULT Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale

ECT

ECT模块该模块的时钟频率设置:自由运行定时器是该模块核心,其工作频率直接决定IC/OC和脉冲计数器的分辨能力。

定时器的输入时钟是通过PACTL寄存器的CLK0、CLK1(0、1、2、3)位来决定,分别选择预分频器时钟、PACLK、PACLK/256、PACLK/65536作为自由定时器的时钟源。

注:PACLK为总线时钟/64。

增强型捕捉定时器ETC,计数器可以自由运行计数(做为自由运行定时器)或预置数,可以停止或清除计数器计数;定时器溢出可以引发中断,每路通道的输入捕捉和输出比较也可以引发中断。

下图为ETC 的中断源。

其对应的中断向量如下:$FFEE, $FFEF Enhanced Capture Timer channel 0 TIE (C0I)$FFEC, $FFED Enhanced Capture Timer channel 1 TIE (C1I)$FFEA, $FFEB Enhanced Capture Timer channel 2 TIE (C2I)$FFE8, $FFE9 Enhanced Capture Timer channel 3 TIE (C3I)$FFE6, $FFE7 Enhanced Capture Timer channel 4 TIE (C4I)$FFE4, $FFE5 Enhanced Capture Timer channel 5 TIE (C5I)$FFE2, $FFE3 Enhanced Capture Timer channel 6 TIE (C6I)$FFE0, $FFE1 Enhanced Capture Timer channel 7 TIE (C7I)$FFDE, $FFDF Enhanced Capture Timer overflow TSRC2 (TOI)$FFDC, $FFDD Pulse accumulator A overflow PACTL (PAOVI)$FFDA, $FFDB Pulse accumulator input edge PACTL (PAI)FFCA, $FFCB Modulus Down Counter underflow MCCTL (MCZI)$FFC8, $FFC9 Pulse Accumulator B Overflow PBCTL (PBOVI)首先应当先了解输入捕捉和输出比较的概念。

飞思卡尔单片机增强型定时器计数器ECT

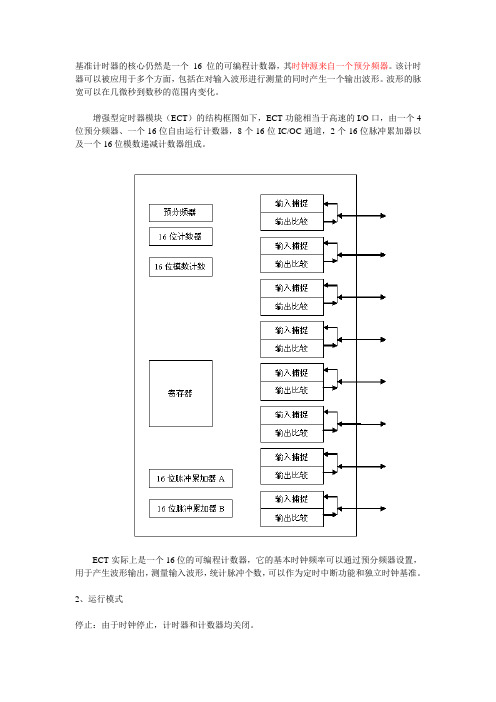

基准计时器的核心仍然是一个16 位的可编程计数器,其时钟源来自一个预分频器。

该计时器可以被应用于多个方面,包括在对输入波形进行测量的同时产生一个输出波形。

波形的脉宽可以在几微秒到数秒的范围内变化。

增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,8个16位IC/OC通道,2个16位脉冲累加器以及一个16位模数递减计数器组成。

ECT实际上是一个16位的可编程计数器,它的基本时钟频率可以通过预分频器设置,用于产生波形输出,测量输入波形,统计脉冲个数,可以作为定时中断功能和独立时钟基准。

2、运行模式停止:由于时钟停止,计时器和计数器均关闭。

冻结:计时器和计数器均保持运行,直到TSCR($06)的TSFRZ 位被置1。

等待:计数器保持运行,直到TSCR($06)的TSWAI 位被置1。

正常:计时器和计数器均保持运行,直到TSCR($06)的TEN 位和MCCTL($26)的MCEN 位被分别清0。

IC 通道组由四个标准的缓冲通道IC0-IC3 和四个非缓冲通道IC4-IC7 组成,两部分的基本功能都是捕捉外部事件发生的时刻,但是缓冲通道除了IC/OC 寄存器TCn 外,还设有保持寄存器TCnH,此外还在入口设置了延迟计数器,用来提高抗干扰能力。

非缓冲通道没有保持寄存器,入口也没有延迟计数器,但每个通道入口设置了一个 2 输入端的多路器,事件触发信号可以是来自本通道的输入引脚PORTn,也可以是来自其关联通道PORT(n-4)的延迟计数器输出,使用更加灵活。

当延迟功能有效时,输入引脚检测到一个有效的边沿后,延迟计数器开始对P 时钟(模块时钟)进行计数,当到达设定的计数值后,延迟计数器在其输出端有条件地产生一个脉冲,这个条件就是延迟前后的引脚电平相反。

这样可以避免对窄输入脉冲做出反应。

延迟计数结束后,计数器自动清除。

输入信号两个有效边沿之间的持续时间必须大于设定的延迟时间。

飞思卡尔S12单片机ECT模块使用实例

/** ###################################################################** Filename : Project_2.c** Project : Project_2** Processor : MC9S12XEP100CAG** Version : Driver 01.14** Compiler : CodeWarrior HCS12X C Compiler** Date/Time : 2014-5-21, 8:55** Abstract :** Main module.** This module contains user's application code.** Settings :** Contents :** No public methods**** ###################################################################*//* MODULE Project_2 *//* Including needed modules to compile this module/procedure */#include "Cpu.h"#include "Events.h"#include "Bit1.h"#include "Bit2.h"/* Include shared modules, which are used for whole project */#include "PE_Types.h"#include "PE_Error.h"#include "PE_Const.h"#include "IO_Map.h"/* User includes (#include below this line is not maintained by Processor Expert) *//************************************************************//* 初始化ECT模块*//************************************************************/void initialize_ect(void){//ECT_TSCR1_TFFCA = 1; // 定时器标志位快速清除ECT_TSCR1_TEN = 1; // 定时器使能位. 1=允许定时器正常工作; 0=使主定时器不起作用(包括计数器)ECT_TIOS = 0x03; //指定所有通道为输出比较方式ECT_TCTL2_OM0 = 0; // 后四个通道设置为定时器与输出引脚断开ECT_TCTL2_OL0 = 1; // 前四个通道设置为定时器与输出引脚断开ECT_TCTL2_OM1 = 0; // 后四个通道设置为定时器与输出引脚断开ECT_TCTL2_OL1 = 1; // 前四个通道设置为定时器与输出引脚断开//ECT_DL YCT = 0x00; // 延迟控制功能禁止// ECT_ICOVW = 0x00; // 对应的寄存器允许被覆盖; NOVWx = 1, 对应的寄存器不允许覆盖// ECT_ICSYS = 0x00; // 禁止IC及PAC的保持寄存器ECT_TIE = 0x00; // 禁止所有通道定时中断ECT_TSCR2 = 0x04; // 预分频系数pr2-pr0:111,,时钟周期为4us,ECT_TFLG1 = 0xff; // 清除各IC/OC中断标志位//定时器中断标志1 ECT_TFLG2 = 0xff; // 清除自由定时器中断标志位*/// ECT_TC0 = 60000 ;//ECT_TC1 = 10 ;}int x,y;void main(void){/* Write your local variable definition here *//*** Processor Expert internal initialization. DON'T REMOVE THIS CODE!!! ***/PE_low_level_init();/*** End of Processor Expert internal initialization. ***/ initialize_ect();/* Write your code here */x=0;y=0;for(;;){ECT_TFLG1_C0F = 1; //清除标志位ECT_TC0 = ECT_TCNT + 32767; //设置输出比较时间为0.125swhile(ECT_TFLG1_C0F == 0); //等待,直到发生输出比较事件// ECT_TFLG1_C0F = 1; //清除标志位// ECT_TC0 = ECT_TCNT + 31250; //设置输出比较时间为0.125s// while(ECT_TFLG1_C0F == 0); //等待,直到发生输出比较事件}/*** Processor Expert end of main routine. DON'T MODIFY THIS CODE!!! ***/for(;;){}/*** Processor Expert end of main routine. DON'T WRITE CODE BELOW!!! ***/} /*** End of main routine. DO NOT MODIFY THIS TEXT!!! ***//* END Project_2 *//*** ###################################################################**** This file was created by Processor Expert 3.02 [04.44]** for the Freescale HCS12X series of microcontrollers.**** ###################################################################*/。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基准计时器的核心仍然是一个16 位的可编程计数器,其时钟源来自一个预分频器。

该计时器可以被应用于多个方面,包括在对输入波形进行测量的同时产生一个输出波形。

波形的脉宽可以在几微秒到数秒的范围内变化。

增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,8个16位IC/OC通道,2个16位脉冲累加器以及一个16位模数递减计数器组成。

ECT实际上是一个16位的可编程计数器,它的基本时钟频率可以通过预分频器设置,用于产生波形输出,测量输入波形,统计脉冲个数,可以作为定时中断功能和独立时钟基准。

2、运行模式

停止:由于时钟停止,计时器和计数器均关闭。

冻结:计时器和计数器均保持运行,直到TSCR($06)的TSFRZ 位被置1。

等待:计数器保持运行,直到TSCR($06)的TSWAI 位被置1。

正常:计时器和计数器均保持运行,直到TSCR($06)的TEN 位和MCCTL($26)的MCEN 位被分别清0。

IC 通道组由四个标准的缓冲通道IC0-IC3 和四个非缓冲通道IC4-IC7 组成,两部分的基本功能都是捕捉外部事件发生的时刻,但是缓冲通道除了IC/OC 寄存器TCn 外,还设有保持寄存器TCnH,此外还在入口设置了延迟计数器,用来提高抗干扰能力。

非缓冲通道没有保持寄存器,入口也没有延迟计数器,但每个通道入口设置了一个 2 输入端的多路器,事件触发信号可以是来自本通道的输入引脚PORTn,也可以是来自其关联通道PORT(n-4)的延迟计数器输出,使用更加灵活。

当延迟功能有效时,输入引脚检测到一个有效的边沿后,延迟计数器开始对P 时钟(模块时钟)进行计数,当到达设定的计数值后,延迟计数器在其输出端有条件地产生一个脉冲,这个条件就是延迟前后的引脚电平相反。

这样可以避免对窄输入脉冲做出反应。

延迟计数结束后,计数器自动清除。

输入信号两个有效边沿之间的持续时间必须大于设定的延迟时间。

在ECT 中,所有IC 通道均设置了覆盖保护功能,可以通过寄存器ICOVW设置是否允许某个通道用新的捕捉结果覆盖上一个结果。

对于缓冲的IC 通道PT0-PT3,还具有锁存与队列两种工作方式。

在锁存方式下,每个有效的引脚事件只将自由定时器的值放入捕捉寄存器TCn,而TCn 到保持寄存器TCnH 的传送必须依赖递减模数计数器回0 或者其他强制锁存命令才能实现,这时IC 的工作情形与第 6 章的TIM 模块相似。

在队列方式下(图7-2),TCn 与TCnH 形成了一个类似先进先出的队列,每个捕捉结果从TCn 进入,然后随着下一个捕捉结果的到来移入TCnH,程序可以从TCnH 取得结果,然而这个队列是开放的,即程序也可以直接从TCn 取得捕捉结果。

队列方式为CPU 提供了充分的响应时间。

由于PAC0-3 与IC0-3 共享相同的引脚,而且共享入口的逻辑,因此在两种方式下,PAI 与IC 都可以同时工作,对同一引脚进行记录,前者记录脉冲或者边沿的数量,后者记录具体的时刻。

模数递减计数器

16 位递减模数计数器(MDC)可以用作时钟基准,产生周期性的中断请求,也可用于将IC 寄存器和脉冲累加器的值锁存到各自的保持寄存器中。

锁存动作可以通过程序设定为周期性的或一次性的。

MDC 的时钟频率可通过独立的定标器设定,内部设有定时常数寄存器,可以实现自动重装载,但MDC 的常数寄存器与MDC 计数器使用相同的地址,加载时通过特殊的时序实现。

每当MDC 回0 时,将在给定的时间段内控制贮和PAI 寄存器的内容向各自的缓冲寄存器传输。

反映了MDC 在IC、PAI 系统中的作用。

脉冲累加器由4 个8 位的通道PAC0-PAC3 组成,可以通过级联形成两个16 位通道PACA、PACB,它可以统计输入引脚上出现的有效边沿的数量,也可以统计有效电平出现的累计时间。

各个通道的8 位保持寄存器是与4 个缓冲IC 通道相关联的,它们共享边沿检测与延迟电路。

当IC 工作在两种不同的队列方式时,PAC 保持寄存器也处于不同的工作状态,在锁存方式下,PCnH 的加载依靠MDC 计数器或者强制命令实现,而在队列方式下,则依靠IC 通道的TCnH 读命令。

可见在ECT 模块下,IC 与PAI 的工作联系更加紧密。

此外,脉冲累加器还有饱和记忆功能,当8 位的脉冲累加器计数超过$FF 后记忆保持,而不回滚到0,这时,计数值$FF 意味着计数已经达到或超过255,如不需要,该功能可以关闭。

这可以用来监视某个通道的计数值是否已经达到预定的目标值。

值得注意的是,PACl、PAC0 级联后,输入引脚为PT0,而PAC3、PAC2 级联后,输入引脚并不是PT2,而是PT7,这样可以与那些无ECT 的MCU 保持一致性。