半导体器件烧毁的物理机理

半导体物理与器件的基本原理解析

半导体物理与器件的基本原理解析半导体是一种能够在一定条件下既能导电又能绝缘的物质,因其在电子学领域的广泛应用而备受关注。

本文将对半导体物理及器件的基本原理进行解析,为读者提供更全面的了解。

一、半导体物理基础1. 原子结构半导体是由原子构成的,涉及到原子的结构和性质非常重要。

原子包含了原子核和绕核运动的电子。

每个原子都有自己的特定电子结构和能级分布。

2. 能带理论能带理论是解释电子在固体中运动的模型。

根据能带理论,固体的电子能级可以分为多个能带,其中最高填充的被称为价带,最低未被填充的被称为导带。

价带与导带之间的能量间隙称为禁带宽度。

3. 共价键与禁带在半导体中,原子通过共价键形成晶体。

共价键是由原子之间的电子互相共享形成的。

晶体中的共价键形成了价带,而禁带宽度是导带和价带之间的能隙。

二、半导体器件原理解析1. P-N 结P-N 结是最基本也是最重要的半导体器件。

它由一片N型半导体和一片P型半导体组成。

在P-N 结中,P型半导体中的空穴与N型半导体中的电子发生重组,产生了一个空穴-电子对。

这种特殊的结构和电子重组现象使得P-N 结具有二极管特性。

2. 二极管二极管是一种基本半导体器件,它由P-N 结组成。

二极管具有一个P型区域和一个N型区域,其中P型区域为阳极,N型区域为阴极。

正向偏置时,电流可以流过二极管;反向偏置时,电流无法通过二极管。

3. 晶体管晶体管是一种用来放大和开关电信号的半导体器件。

它由三个区域构成:发射极(Emitter)、基极(Base)和集电极(Collector)。

晶体管的工作原理是通过外加电压控制基区的电流,从而控制集电极和发射极之间的电流流动。

4. MOSFETMOSFET(金属-氧化物-半导体场效应晶体管)是一种常见的半导体器件,用于放大和开关电信号。

MOSFET由金属栅极、绝缘层和半导体通道构成。

通过改变栅极电压,可以控制通道中的电流。

5. 整流器整流器是一种将交流电转换为直流电的设备。

ESD对微波半导体器件损伤的物理机理分析

ESD对微波半导体器件损伤的物理机理分析吴东岩;谭志良【摘要】为了得到电磁脉冲对微波半导体器件的损伤规律,进而研究器件的静电放电损伤机理,首先对半导体器件静电放电的失效模式即明显失效和潜在性失效进行了介绍;其次分析了器件ESD损伤模型;最后通过对器件烧毁的物理机理进行分析,得到器件在静电放电应力下内在损伤原因.在ESD电磁脉冲作用下,器件会产生击穿效应,使内部电流密度、电场强度增大,导致温度升高,最终造成微波半导体器件的烧毁.%In order to obtain the damage rule of microwave semiconductor devices caused by electromagnetic pulse and study the electrostatic damage mechanism of the devices,the failure mode of semiconductor devices caused by ESD,such as apparent failure and potential failure,is introduced.The damage modeling is analyzed.Finally,the inherent damage reason of the device under electrostatic discharge stress is obtained by analyzing the physics mechanism of the burned device.Breakdown may happen under the action of ESD EMP,the internal electric field and the current density of the device increase,which cause the temperature rise and result in microwave semiconductor device burned.【期刊名称】《河北科技大学学报》【年(卷),期】2013(034)004【总页数】6页(P308-312,349)【关键词】静电放电;半导体器件;损伤;模式;物理机理【作者】吴东岩;谭志良【作者单位】军械工程学院静电与电磁防护研究所,河北石家庄 050003;军械工程学院静电与电磁防护研究所,河北石家庄 050003【正文语种】中文【中图分类】TN385随着电子技术的迅速发展,电子系统面临的电磁环境日益复杂,各种形式的电磁脉冲可以通过孔缝或者天线耦合等方式进入电子设备内部,影响电子设备的正常工作[1-3]。

细叙各类电子元器件的失效模式与机理

细叙各类电子元器件的失效模式与机理

电子元器件的主要失效模式包括但不限于开路、短路、烧毁、爆炸、漏电、功能失效、电参数漂移、非稳定失效等。

对于硬件工程师来讲电子元器件失效是个非常麻烦的事情,比如某个半导体器件外表完好但实际上已经半失效或者全失效会在硬件电路调试上花费大把的时间,有时甚至炸机。

硬件工程师调试爆炸现场

所以掌握各类电子元器件的实效机理与特性是硬件工程师比不可少的知识。

下面分类细叙一下各类电子元器件的失效模式与机理。

电阻器失效模式与机理失效模式:各种失效的现象及其表现的形式。

失效机理:是导致失效的物理、化学、热力学或其他过程。

1、电阻器的主要失效模式与失效机理为1) 开路:主要失效机理为电阻膜烧毁或大面积脱落,基体断裂,引线帽与电阻体脱落。

2) 阻值漂移超规范:电阻膜有缺陷或退化,基体有可动钠离子,保护涂层不良。

3) 引线断裂:电阻体焊接工艺缺陷,焊点污染,引线机械应力损伤。

4) 短路:银的迁移,电晕放电。

2、失效模式占失效总比例表

(1)、线绕电阻

失效模式占失效总比例开路90%阻值漂移2%引线断裂7%其它1%

(2)、非线绕电阻

失效模式占失效总比例开路49%阻值漂移22%引线断裂17%其它7%

3、失效机理分析

电阻器失效机理是多方面的,工作条件或环境条件下所发生的各种理化过程是引起电阻器老化的原因。

(1)、导电材料的结构变化

薄膜电阻器的导电膜层一般用汽相淀积方法获得,在一定程度上存在无定型结构。

按热力。

常见的电子元器件失效机理与分析

常见的电子元器件失效机理与分析电子元器件的主要失效模式包括但不限于开路、短路、烧毁、爆炸、漏电、功能失效、电参数漂移、非稳定失效等。

对于硬件工程师来讲电子元器件失效是个非常麻烦的事情,比如某个半导体器件外表完好但实际上已经半失效或者全失效会在硬件电路调试上花费大把的时间,有时甚至炸机。

硬件工程师调试爆炸现场所以掌握各类电子元器件的实效机理与特性是硬件工程师比不可少的知识。

下面分类细叙一下各类电子元器件的失效模式与机理。

电阻器失效失效模式:各种失效的现象及其表现的形式。

失效机理:是导致失效的物理、化学、热力学或其他过程。

电阻器的失效模式与机理▶开路:主要失效机理为电阻膜烧毁或大面积脱落,基体断裂,引线帽与电阻体脱落。

▶阻值漂移超规范:电阻膜有缺陷或退化,基体有可动钠离子,保护涂层不良。

▶引线断裂:电阻体焊接工艺缺陷,焊点污染,引线机械应力损伤。

▶短路:银的迁移,电晕放电。

失效模式占失效总比例表▶线绕电阻:▶非线绕电阻:失效模式机理分析电阻器失效机理是多方面的,工作条件或环境条件下所发生的各种理化过程是引起电阻器老化的原因。

▶导电材料的结构变化:薄膜电阻器的导电膜层一般用汽相淀积方法获得,在一定程度上存在无定型结构。

按热力学观点,无定型结构均有结晶化趋势。

在工作条件或环境条件下,导电膜层中的无定型结构均以一定的速度趋向结晶化,也即导电材料内部结构趋于致密化,能常会引起电阻值的下降。

结晶化速度随温度升高而加快。

电阻线或电阻膜在制备过程中都会承受机械应力,使其内部结构发生畸变,线径愈小或膜层愈薄,应力影响愈显著。

一般可采用热处理方法消除内应力,残余内应力则可能在长时间使用过程中逐步消除,电阻器的阻值则可能因此发生变化。

结晶化过程和内应力清除过程均随时间推移而减缓,但不可能在电阻器使用期间终止。

可以认为在电阻器工作期内这两个过程以近似恒定的速度进行。

与它们有关的阻值变化约占原阻值的千分之几。

电负荷高温老化:任何情况,电负荷均会加速电阻器老化进程,并且电负荷对加速电阻器老化的作用比升高温度的加速老化后果更显著,原因是电阻体与引线帽接触部分的温升超过了电阻体的平均温升。

半导体器件烧毁的物理机理

半导体器件烧毁的物理机理*余稳蔡新华黄文华刘国治摘要叙述了半导体器件烧毁的物理机理、目前的研究进展及作者正在开展的工作.关键词半导体器件,烧毁,高功率微波MECHANISM OF BURNOUT OF SEMICONDUCTOR DEVICESYu Wen Cai Xinhua(Institute of EM Theory, Changde Teachers' College,Hunan415000)Huang Wenhua Liu Guozhi(Northwest Institute of Nuclear Technology, Xi'an710024)Abstract The general mechanism of burnout of semiconductor devices is described,as well as recent progress and our present research.Key words semiconductor devices, burnout, high power microwave(HPM)1前言高功率微波(HPM)对电子系统进行破坏,可使系统暂时失灵或永久失效,这直接涉及系统内部电子元器件的暂时失灵或永久失效.因此要研究HPM对电子系统的破坏机理,首先要研究半导体器件烧毁的物理机理.另外,从系统的抗辐射能力和加固方面看,也需要对电子系统进行在电过应力(EOS)环境下的易损性评估.以下几个问题使得评估很困难:(1)对任意一个电子器件,很难得到精确的理论或实验失效阈值;(2)实际的EOS应力参数必须与用于理论或实验上确定失效阈值时使用的理想参数相比较,过度保守的估计将导致系统的超加固,增加不必要的成本,拖延进度,降低系统性能,而过高的估计则可使系统易损;(3)器件的复杂性问题[不同的制造过程、不同种类的器件(甚至同种器件间)有变化];(4)产生EOS的电磁环境问题[如电磁脉冲(EMP)、核电磁脉冲(NEMP)、光电磁脉冲(LEMP)、电磁干扰(EMI)、静电放电(ESD)、系统电磁脉冲(SGEMP)、微波(MW)等等];(5)同一批器件,数据变化也很大,不同一批器件和不同厂家的产品,数据变化就更大.因此,从理论上探讨器件烧毁的物理机理,找出大致规律,很有意义.2器件烧毁的物理机理半导体器件承受EOS测试时,将表现出很多失效物理机理[1],几乎器件的每一部分都有可能失效:(1)敷金属和引线能被熔化,电迁移能使金属膜导体变薄,甚至导致开路;(2)在器件的绝缘材料或氧化区或器件表面,可产生导致局部高温的电击穿;(3)在有源结区,可产生导致强流和高温的二次击穿.根据研究,对双极型器件,90%的失效是由结区击穿引起的,敷金属失效仅占10%,但对MOS 器件,则63%的失效来源于敷金属失效,27%则属于氧化物击穿.通常在局部温度升高到熔点时发生敷金属和引线失效,该热量来自于金属中的强流密度或金属附近的热硅(由其他地方的强流密度引起).敷金属失效将因线路分开(有点像保险丝烧毁)而导致开路.引起失效的强流可能来自于击穿或器件其他地方的失效,所以敷金属和引线失效可能只是一种结果而不是器件失效的原因.电迁移应用于强流密度情形下金属中的质量输运.最近,人们认为,对金属膜导体截面不够的半导体器件,电迁移可能是一种消耗失效模式,该失效将导致电路开路.当半导体或绝缘体两条蚀刻导电通道之间的电场超过中间介质击穿极限时,将因产生电弧形成熔融金属通道而使电路短路,器件线度越小,该失效机制越重要.PN结的表面条件将影响其电特性.依赖于表面条件的表面复合过程,对自由载流子来说像一个阱.强场表面击穿是表面损伤的原因之一.对半导体器件,该强场发生于靠近结区与表面的交界处.器件绝缘区失效主要是高压击穿(由材料中的强瞬间电场或硅材料附近热点的热损伤或机械损伤所致).半导体器件有源结区的失效通常来自于局部熔化及随后的硅再结晶,或来自于从结表面来的实际热注入,该热量由通过结的强流密度引起,反过来又导致热或电流二次击穿.二次击穿模式有热模式和电流模式两种[2—4]. 随入射EOS功率不同而采取不同的模式,并可根据其不同的发展速度区别不同的模式.电流模式通常是ns量级,而热模式则为μs量级.二次击穿可因其负阻区而与其他(如雪崩)击穿相区别,人们对二次击穿进行过不少研究[3—5],综合这些研究,可得到二次击穿的物理机理如下:通常认为热模式击穿占主导地位,雪崩击穿产生的强流将器件加热到600—800K时,带电载流子的热产生变得很重要,器件进入热-电流失控状态,此时随着温度的升高,载流子越来越多,器件电阻率下降,这样将允许通过更大的电流,从而进一步提高器件温度.如果该失控得不到很快阻止,(通常停止对器件的功率输入),最终的高温将损伤或毁坏该器件.强场也能够通过欧姆加热而使敷金属带熔化.电流二次击穿模式则发生于较高的外加电压情形,并且其电流比热模式的要高得多.一般情况下,由于载流子浓度比掺杂浓度低得多,掺杂浓度控制着耗尽区的电场.当有高的外加电压时,由于雪崩撞电离而产生大量载流子,并注入到耗尽区.当载流子浓度超过掺杂浓度时,则是载流子浓度而不是掺杂浓度控制着耗尽区的电场.高载流子浓度将增加耗尽区的电场,这将导致在耗尽区的边缘产生雪崩,而产生所谓的“双重注入”.如果载流子注入的速度比传导过程移走它们的速度快,则从耗尽区中心到边缘的电场将得到进一步加强.最后,热-电流失控将使电流密度得到极大增加,在器件中产生大量热量.加热将抑制雪崩产生,并有可能关闭电流二次击穿模式,但是在足够高的功率水平下,将由于失控的增强高于热抑制而使二次击穿得以维持,最终将达到令器件烧毁的程度.和热模式一样,此时的强流亦可毁坏其他地方的敷金属带.电流和热丝的形成,被认为是与二次击穿相关联并同时发生的另一种现象.当强流不再均匀流过结区而集中于一个小区域时,将形成丝.该电流的集中以及它所引起的加热将进一步加强上面描述的过程,并在器件中产生热斑.已有实验工作者观察到了这种热斑.当热斑温度达到1000K 时,由于熔化和杂质迁移,器件性能将极大地降低,当温度达到1688K时,硅将熔化,导致结区短路.3失效分析模型正常半导体的行为可用电子、空穴连续性方程和泊松方程描述,对高压瞬态情形,还必须考虑热流方程及方程系数(如迁移率、热导率等)对温度和电场的依赖关系,致使对器件的行为要用一组耦合、非线性、刚性偏微分方程来描述.由于耦合和非线性,即使仅考虑一维情形,方程组也没有解析解,刚性方程组的数值解也太费机时,因此人们便设法使其简化,以便能用解析或数值的方法解方程组.这里仅讨论二次击穿的分析模型.通常有三种模型:解析模型、经验模型和数值计算模型.另外可以进一步分为热模型、电模型和热电模型,这主要根据模型所处理的方程来决定.热模型仅考虑热流方程而忽略其他,电模型则仅考虑电方程而忽略热方程,热电模型则考虑所有方程.3.1解析二次击穿模型由于方程组的复杂性,不经充分简化是无法得到解析解的.绝大多数模型都基于一维热流方程的解而忽略了所有其他方程(仅考虑了由于器件电流引起的热产生率因子).通常认为热产生于无限薄的结区,并流到一维无限介质,并假定热产生激发为单一电能方波脉冲,一般称这类模型为Wunsch-Bell模型.电模型则忽略热流方程,因此该模型仅能在低功率水平(或高功率水平的早期)给出合理的结果,对烧毁机理研究无应用价值,但对正常行为有效.3.2经验二次击穿模型主要由解析模型的作者进行,根据解析解形式,构造函数以拟合实验数据,因此本质上也属于热模式范畴.3.3数值二次击穿模型采用数值技术简化并求解方程组.它试图完整地模拟由于加有EOS而引起的依赖于时间的行为,而为是像解析模型和经验模型那样仅预测最终结果.因此数值二次击穿模型能预见半导体器件在EOS环境下所发生的具体行为,这种预见可产生器件和线路设计规则,并有可能使系统在EOS环境下的生存能力得到提高,有利于抗辐射加固.数值二次击穿模型一般又分为热模型、电模型和热电模型.关于热模型,Kusnezov[6]等,利用显式有限差分法解一维和二维传导方程,忽略其他电效应,对电效应的处理完全依赖于稳态电阻率温度曲线.这种模型对热效应和热斑形成能产生令人感兴趣的结果,但却不能产生可靠的瞬态电效应效果,同时也无法模拟任何电流二次击穿效应.电模型是对电效应方程进行详细计算,但完全忽略热效应.因此无法处理EOS环境下的强电场效应(包括依赖于场的迁移率、速度饱和及雪崩产生等).热电模型是同时考虑电方程和热流方程,有不少人开展了这方面的工作[5,7].4研究进展及将开展的工作从70年代后期开始,有一些学者致力于半导体器件烧毁物理的数值模拟,到80年代后期基本进入高潮阶段.其中Orvis及Word等人的工作尤其具有代表性.Orvis等人建立了半导体器件的一维和二维数值模型,并编制了相应的程序,同时用程序对失效机制作了分析研究,但未见任何与实验相结合的应用.而Word等人,则仅进行了一维模拟,但他们用程序进行了一系列的具体应用,对硅PIN二极管微波限幅器进行了全面系统的理论和实验研究[8],包括直流正偏开关特性、正偏电导率、尖峰漏能、分离及损伤阈值等方面.从文献看,他们认为其程序也急待修改,但未见修改后的报道.在提高计算精度方面,有一些学者考虑了诸如带宽变窄、杂质消电离、热电子及其他许多物理现象[9];在提高计算速度方面,Osman等人提出的“混合解法”[10]有其独特的功效.从文献查阅情况看,除Word等人外,其他人都很少涉及实验,仅停留在理论阶段.而Word 等人虽然和实验有比较,但计算程序较简单,且只有一维模拟,因此和实验符合不理想,目前他们正致力于完善该程序.另外,值得注意的是,以上理论研究所用的源均是阶跃电磁脉冲,没有涉及微波领域.我们将在上述这些工作的基础上,建立半导体器件模拟的一维和二维模型及相应程序,并和实验工作配合进行,重点将放在微波对半导体器件的破坏机理研究上.作者单位:余稳蔡新华湖南常德师范专科学校电磁理论研究所湖南常德415000 黄文华刘国治西北核技术研究所西安710024。

半导体器件的物理原理

半导体器件的物理原理半导体器件是当今科技进步的重要基石,广泛应用于电子设备、通信技术和能源转换等领域。

半导体器件的物理原理涉及到晶体结构、载流子运动以及电子能带等概念,下面将从这些方面展开论述。

晶体结构是半导体器件物理原理的基础。

半导体材料通常采用单晶或多晶的结构,其中单晶具有高度有序的原子排列,能够提供更好的电子传输通道。

晶体结构中的晶格常数以及晶格点的配位数决定了材料的载流子密度和能带结构。

例如,硅(Si)是一种常用的半导体材料,其晶格常数较大,晶格点配位数为4,因此具有较高的载流子密度,适用于大功率器件。

而锗(Ge)是另一种半导体材料,晶格常数较小,晶格点配位数为4,因此具有较低的载流子密度,更适用于低功率器件。

载流子运动是半导体器件工作的关键。

半导体材料中的载流子主要包括自由电子和空穴。

自由电子具有负电荷,在外电场的作用下形成电流;而空穴则相当于正电荷缺失的位置,同样能够参与电流的传输。

半导体材料内的载流子运动受到晶格振动、杂质掺杂以及温度等因素的影响。

在零温下,半导体处于绝缘态,载流子几乎没有运动能力;而在高温下,载流子的运动能力增强,半导体逐渐变为导体。

半导体器件的物理原理还涉及到电子能带结构。

在晶体中,电子的能量将按照一定规律排列成能带。

最低能量的能带称为价带,其中填满了电子;而最高能量的能带称为导带,其中没有或仅有极少数的电子。

半导体材料的价带和导带之间的能带隔离称为禁带宽度,它决定了半导体的导电性能。

当禁带宽度较小时,外界的微弱电场就能够激发半导体中的载流子,使其变为导体;而禁带宽度较大时,外界电场的激发能力较弱,使得半导体呈现绝缘性。

通过控制禁带宽度,我们可以调节半导体器件的电导率,从而实现对电流的精确控制。

为了实现特定的功能,半导体器件常常需要经过复杂的工艺制造。

例如,晶体管是一种重要的半导体器件,它通过控制电场和电流的作用,实现对电路的放大和开关功能。

晶体管的制造过程包括材料生长、掺杂、薄膜沉积、光刻、蚀刻等多个步骤,每个步骤都需要精确控制参数,以确保器件的性能和可靠性。

第01章半导体器件失效分析概论

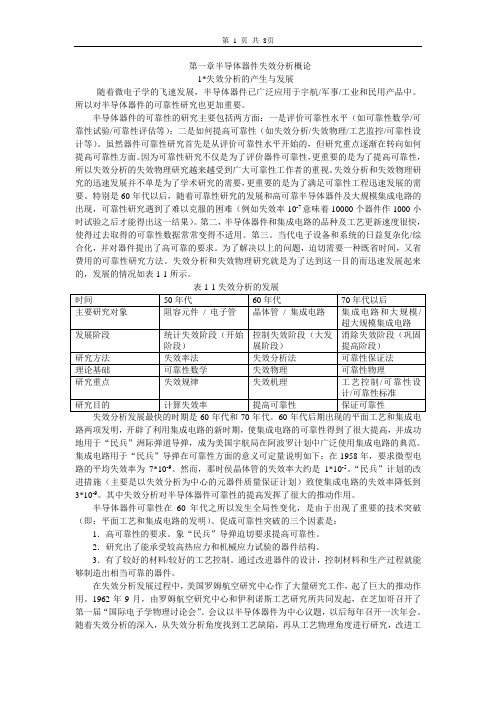

第一章半导体器件失效分析概论1*失效分析的产生与发展随着微电子学的飞速发展,半导体器件已广泛应用于宇航/军事/工业和民用产品中。

所以对半导体器件的可靠性研究也更加重要。

半导体器件的可靠性的研究主要包括两方面:一是评价可靠性水平(如可靠性数学/可靠性试验/可靠性评估等);二是如何提高可靠性(如失效分析/失效物理/工艺监控/可靠性设计等)。

虽然器件可靠性研究首先是从评价可靠性水平开始的,但研究重点逐渐在转向如何提高可靠性方面。

因为可靠性研究不仅是为了评价器件可靠性,更重要的是为了提高可靠性,所以失效分析的失效物理研究越来越受到广大可靠性工作者的重视。

失效分析和失效物理研究的迅速发展并不单是为了学术研究的需要,更重要的是为了满足可靠性工程迅速发展的需要。

特别是60年代以后,随着可靠性研究的发展和高可靠半导体器件及大规模集成电路的出现,可靠性研究遇到了难以克服的困难(例如失效率10-7意味着10000个器件作1000小时试验之后才能得出这一结果)。

第二,半导体器件和集成电路的品种及工艺更新速度很快,使得过去取得的可靠性数据常常变得不适用。

第三。

当代电子设备和系统的日益复杂化/综合化,并对器件提出了高可靠的要求。

为了解决以上的问题,迫切需要一种既省时间,又省费用的可靠性研究方法。

失效分析和失效物理研究就是为了达到这一目的而迅速发展起来的,发展的情况如表1-1所示。

路两项发明,开辟了利用集成电路的新时期,使集成电路的可靠性得到了很大提高,并成功地用于“民兵”洲际弹道导弹,成为美国宇航局在阿波罗计划中广泛使用集成电路的典范。

集成电路用于“民兵”导弹在可靠性方面的意义可定量说明如下:在1958年,要求微型电路的平均失效率为7*10-9。

然而,那时侯晶体管的失效率大约是1*10-5。

“民兵”计划的改进措施(主要是以失效分析为中心的元器件质量保证计划)致使集成电路的失效率降低到3*10-9。

其中失效分析对半导体器件可靠性的提高发挥了很大的推动作用。

物理学中的半导体元器件原理

物理学中的半导体元器件原理半导体元器件是现代电子产业的重要组成部分,其中最具代表性的是晶体管、二极管和集成电路等。

这些元器件在现代电子技术中发挥着重要的作用,被广泛应用于计算机、通信、音视频等领域。

那么,它们的基本原理是什么呢?这篇文章将从物理学的角度探讨半导体元器件的原理。

第一部分:半导体基础知识半导体是指导电性介于导体和绝缘体之间的物质,具有一些特殊的电学性质。

半导体材料中,某些元素的原子晶格存在空位或缺陷,或者在其晶格中掺入一些杂质原子,从而形成半导体材料。

半导体的导电性与其电子能级结构有关。

在半导体材料中,电子可能会占据不同的能级,其中最低的能级称为价带,最高的能级称为导带。

通常情况下,价带中的电子处于芯层原子的电场束缚之下,而不自由运动;而导带中则没有束缚,电子可以自由运动。

当半导体材料受到一定的能量激发,如光子或热能,导带内的电子就可以跃迁至价带内,将其电导率提高。

这种情况下,半导体称为“n型半导体”。

如果掺杂进杂质原子使材料生成微键,并增加占据导带的电子,则称为“p型半导体”。

第二部分:二极管的原理二极管是一种简单的半导体元器件,由p型半导体和n型半导体组成,能够实现单向电流的导通。

二极管的特点是:在正向偏置下,p区域中和n区域中的电子就会发生大规模的扩散,进而形成一个漂移电流;而在反向偏置下,无法形成漂移电流,因此电流极小,由此实现了单向导通。

简单来说,二极管的工作原理是靠材料特性,即p和n型半导体接触时,会在界面处产生电势垒。

在正向偏置下,这些电子穿越电势垒,进入p区域中,并与p区的空穴复合产生光子和热能;在反向偏置下,由于电子无法穿越电势垒,因此电流极小,达到了单向导通的效果。

第三部分:晶体管的原理晶体管是一种具有放大和开关功能的半导体器件,由三个区域组成,即发射区、基区和集电区,分别对应p-n-p型或n-p-n型半导体管。

晶体管的原理是利用反向偏置形成的p-n陡斜电势垒来操纵涉及三区域电势平衡的电流传导。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

半导体器件烧毁的物理机理*

余稳蔡新华黄文华刘国治

摘要叙述了半导体器件烧毁的物理机理、目前的研究进展及作者正在开展的工作.

关键词半导体器件,烧毁,高功率微波

MECHANISM OF BURNOUT OF SEMICONDUCTOR DEVICES

Yu Wen Cai Xinhua

(Institute of EM Theory, Changde Teachers' College,Hunan415000)

Huang Wenhua Liu Guozhi

(Northwest Institute of Nuclear Technology, Xi'an710024)

Abstract The general mechanism of burnout of semiconductor devices is described,as well as recent progress and our present research.

Key words semiconductor devices, burnout, high power microwave(HPM)

1前言

高功率微波(HPM)对电子系统进行破坏,可使系统暂时失灵或永久失效,这直接涉及系统内部电子元器件的暂时失灵或永久失效.因此要研究HPM对电子系统的破坏机理,首先要研究半导体器件烧毁的物理机理.另外,从系统的抗辐射能力和加固方面看,也需要对电子系统进行在电过应力(EOS)环境下的易损性评估.以下几个问题使得评估很困难:(1)对任意一个电子器件,很难得到精确的理论或实验失效阈值;(2)实际的EOS应力参数必须与用于理论或实验上确定失效阈值时使用的理想参数相比较,过度保守的估计将导致系统的超加固,增加不必要的成本,拖延进度,降低系统性能,而过高的估计则可使系统易损;(3)器件的复杂性问题[不同的制造过程、不同种类的器件(甚至同种器件间)有变化];(4)产生EOS的电磁环境问题[如电磁脉冲(EMP)、核电磁脉冲(NEMP)、光电磁脉冲(LEMP)、电磁干扰(EMI)、静电放电(ESD)、系统电磁脉冲(SGEMP)、微波(MW)等等];(5)同一批器件,数据变化也很大,不同一批器件和不同厂家的产品,数据变化就更大.因此,从理论上探讨器件烧毁的物理机理,找出大致规律,很有意义.

2器件烧毁的物理机理

半导体器件承受EOS测试时,将表现出很多失效物理机理[1],几乎器件的每一部分都有可能失效:(1)敷金属和引线能被熔化,电迁移能使金属膜导体变薄,甚至导致开路;(2)在器件的绝缘材料或氧化区或器件表面,可产生导致局部高温的电击穿;(3)在有源结区,可产生导致强流和高温的二次击穿.

根据研究,对双极型器件,90%的失效是由结区击穿引起的,敷金属失效仅占10%,但对MOS 器件,则63%的失效来源于敷金属失效,27%则属于氧化物击穿.

通常在局部温度升高到熔点时发生敷金属和引线失效,该热量来自于金属中的强流密度或金属附近的热硅(由其他地方的强流密度引起).敷金属失效将因线路分开(有点像保险丝烧毁)而导致开路.引起失效的强流可能来自于击穿或器件其他地方的失效,所以敷金属和引线失效可能只是一种结果而不是器件失效的原因.电迁移应用于强流密度情形下金属中的质量输运.最近,人们认为,对金属膜导体截面不够的半导体器件,电迁移可能是一种消耗失效模式,该失效将导致电路开路.当半导体或绝缘体两条蚀刻导电通道之间的电场超过中间介质击穿极限时,将因产生电弧形成熔融金属通道而使电路短路,器件线度越小,该失效机制越重要.

PN结的表面条件将影响其电特性.依赖于表面条件的表面复合过程,对自由载流子来说像一个阱.强场表面击穿是表面损伤的原因之一.对半导体器件,该强场发生于靠近结区与表面的交界处.器件绝缘区失效主要是高压击穿(由材料中的强瞬间电场或硅材料附近热点的热损伤或机械损伤所致).半导体器件有源结区的失效通常来自于局部熔化及随后的硅再结晶,或来自于从结表面来的实际热注入,该热量由通过结的强流密度引起,反过来又导致热或电流二次击穿.

二次击穿模式有热模式和电流模式两种[2—4]. 随入射EOS功率不同而采取不同的模式,

并可根据其不同的发展速度区别不同的模式.电流模式通常是ns量级,而热模式则为μs量级.二次击穿可因其负阻区而与其他(如雪崩)击穿相区别,人们对二次击穿进行过不少研究[3—5],综合这些研究,可得到二次击穿的物理机理如下:通常认为热模式击穿占主导地位,雪崩击穿产生的强流将器件加热到600—800K时,带电载流子的热产生变得很重要,器件进入热-电流失控状态,此时随着温度的升高,载流子越来越多,器件电阻率下降,这样将允许通过更大的电流,从而进一步提高器件温度.如果该失控得不到很快阻止,(通常停止对器件的功率输入),最终的高温将损伤或毁坏该器件.强场也能够通过欧姆加热而使敷金属带熔化.电流二次击穿模式则发生于较高的外加电压情形,并且其电流比热模式的要高得多.一般情况下,由于载流子浓度比掺杂浓度低得多,掺杂浓度控制着耗尽区的电场.当有高的外加电压时,由于雪崩撞电离而产生大量载流子,并注入到耗尽区.当载流子浓度超过掺杂浓度时,则是载流子浓度而不是掺杂浓度控制着耗尽区的电场.高载流子浓度将增加耗尽区的电场,这将导致在耗尽区的边缘产生雪崩,而产生所谓的“双重注入”.如果载流子注入的速度比传导过程移走它们的速度快,则从耗尽区中心到边缘的电场将得到进一步加强.最后,热-电流失控将使电流密度得到极大增加,在器件中产生大量热量.加热将抑制雪崩产生,并有可能关闭电流二次击穿模式,但是在足够高的功率水平下,将由于失控的增强高于热抑制而使二次击穿得以维持,最终将达到令器件烧毁的程度.和热模式一样,此时的强流亦可毁坏其他地方的敷金属带.

电流和热丝的形成,被认为是与二次击穿相关联并同时发生的另一种现象.当强流不再均匀流过结区而集中于一个小区域时,将形成丝.该电流的集中以及它所引起的加热将进一步加强上面描述的过程,并在器件中产生热斑.已有实验工作者观察到了这种热斑.当热斑温度达到1000K 时,由于熔化和杂质迁移,器件性能将极大地降低,当温度达到1688K时,硅将熔化,导致结区短路.

3失效分析模型

正常半导体的行为可用电子、空穴连续性方程和泊松方程描述,对高压瞬态情形,还必须考虑热流方程及方程系数(如迁移率、热导率等)对温度和电场的依赖关系,致使对器件的行为要用一组耦合、非线性、刚性偏微分方程来描述.由于耦合和非线性,即使仅考虑一维情形,方程组也没有解析解,刚性方程组的数值解也太费机时,因此人们便设法使其简化,以便能用解析或数值的方法解方程组.这里仅讨论二次击穿的分析模型.

通常有三种模型:解析模型、经验模型和数值计算模型.另外可以进一步分为热模型、电模型和热电模型,这主要根据模型所处理的方程来决定.热模型仅考虑热流方程而忽略其他,电模型则仅考虑电方程而忽略热方程,热电模型则考虑所有方程.

3.1解析二次击穿模型

由于方程组的复杂性,不经充分简化是无法得到解析解的.绝大多数模型都基于一维热流方程的解而忽略了所有其他方程(仅考虑了由于器件电流引起的热产生率因子).通常认为热产生于无限薄的结区,并流到一维无限介质,并假定热产生激发为单一电能方波脉冲,一般称这类模型为Wunsch-Bell模型.电模型则忽略热流方程,因此该模型仅能在低功率水平(或高功率水平的早期)给出合理的结果,对烧毁机理研究无应用价值,但对正常行为有效.

3.2经验二次击穿模型

主要由解析模型的作者进行,根据解析解形式,构造函数以拟合实验数据,因此本质上也属于热模式范畴.

3.3数值二次击穿模型

采用数值技术简化并求解方程组.它试图完整地模拟由于加有EOS而引起的依赖于时间的行为,而为是像解析模型和经验模型那样仅预测最终结果.因此数值二次击穿模型能预见半导体器件在EOS环境下所发生的具体行为,这种预见可产生器件和线路设计规则,并有可能使系统在EOS环境下的生存能力得到提高,有利于抗辐射加固.数值二次击穿模型一般又分为热模型、电

模型和热电模型.

关于热模型,Kusnezov[6]等,利用显式有限差分法解一维和二维传导方程,忽略其他电效应,对电效应的处理完全依赖于稳态电阻率温度曲线.这种模型对热效应和热斑形成能产生令人感兴趣的结果,但却不能产生可靠的瞬态电效应效果,同时也无法模拟任何电流二次击穿效应.

电模型是对电效应方程进行详细计算,但完全忽略热效应.因此无法处理EOS环境下的强电场效应(包括依赖于场的迁移率、速度饱和及雪崩产生等).

热电模型是同时考虑电方程和热流方程,有不少人开展了这方面的工作[5,7].

4研究进展及将开展的工作

从70年代后期开始,有一些学者致力于半导体器件烧毁物理的数值模拟,到80年代后期基本进入高潮阶段.其中Orvis及Word等人的工作尤其具有代表性.Orvis等人建立了半导体器件的一维和二维数值模型,并编制了相应的程序,同时用程序对失效机制作了分析研究,但未见任何与实验相结合的应用.而Word等人,则仅进行了一维模拟,但他们用程序进行了一系列的具体应用,对硅PIN二极管微波限幅器进行了全面系统的理论和实验研究[8],包括直流正偏开关特性、正偏电导率、尖峰漏能、分离及损伤阈值等方面.从文献看,他们认为其程序也急待修改,但未见修改后的报道.

在提高计算精度方面,有一些学者考虑了诸如带宽变窄、杂质消电离、热电子及其他许多物理现象[9];在提高计算速度方面,Osman等人提出的“混合解法”[10]有其独特的功效.

从文献查阅情况看,除Word等人外,其他人都很少涉及实验,仅停留在理论阶段.而Word 等人虽然和实验有比较,但计算程序较简单,且只有一维模拟,因此和实验符合不理想,目前他们正致力于完善该程序.另外,值得注意的是,以上理论研究所用的源均是阶跃电磁脉冲,没有涉及微波领域.

我们将在上述这些工作的基础上,建立半导体器件模拟的一维和二维模型及相应程序,并和实验工作配合进行,重点将放在微波对半导体器件的破坏机理研究上.

作者单位:余稳蔡新华湖南常德师范专科学校电磁理论研究所湖南常德415000 黄文华刘国治西北核技术研究所西安710024。