IC工艺课程设计 答辩题目

半导体器件与工艺(9)答辩

Ns x j 2 ln N B

1

2

Dt

扩散层Байду номын сангаас量参数

两式统一表示为:

x j A Dt

对余误差分布,

NB A 2erfc 1 N s

对高斯分布,

Ns A 2 ln N B

1 2

扩散层质量参数

方块电阻

扩散层质量参数

④分段击穿:

分段击穿也称管道型击穿。特点是在较低电压下有一击穿点,然 后电流随电压升高而线性增加。当电压继续升高到某一值时再次发生 击穿。产生的原因多是由于基片内存在局部薄弱点,如层错、位错密 度过高,光刻图形边缘不整齐,扩散层表面存在合金点等。

扩散条件的选择

扩散层质量参数与扩散条件密切相关。扩散条件选择合 适,才可能获得质量合乎要求的扩散层。扩散条件包括扩 散方法,扩散杂质源,扩散温度和时间。 (1)扩散方法的选择 扩散方法可以分为气 - 固扩散、液 - 固扩散和固 - 固扩散 三种类型。其中气-固扩散又可分为闭管扩散、箱法扩散和 气体携带法扩散;固-固扩散可分为氧化物源法和涂源法。 ■闭管扩散 特点是把杂质源和将要扩进杂质的衬底片, 密封于同一石英管内,因而扩散的均匀性、重复性较好, 扩散时受外界影响少,在大面积深结扩散时常采用这种方 法。由于密封,还能避免杂质蒸发。缺点是工艺操作繁琐, 每次扩散后都要敲碎石英管,石英管耗费大。另外,每次 扩散都要重新配源。

扩散条件的选择

(2)扩散杂质源的选择 对于硅器件平面工艺中的扩散,杂质源的选择主要应考虑: 对所选择的杂质,SiO2掩模应能起着有效的掩蔽扩散作用;在 硅中的固溶度足够高,要大于所需要的表面浓度;扩散系数的 大小要适当(如杂质扩散便于控制、不同杂质的扩散系数大小 搭配适当、已掺入的杂质在后续的热处理过程中杂质分布变化 小)。作为扩散用的杂质源,还有其他方面的要求,如纯度高, 杂质电离能小,使用方便、安全等。

IC制程相关技术答辩

108 - 109 ULSI ULTRA Large Scale Integration

中文名稱 小型積體電路 中型積體電路 大型積體電路 超大型積體電路 極大型積體電路

*Pentium 4

42 Million Transistors

為何矽晶是IC產業的主流材料?

具可控制的半導體特性 (diode真空管, transistor電晶 體,resistor電阻, capacitor電容, conductor銅導體…)

2.25倍

2.25 3

8” wafer

12 34

2

3456

7 8 9 10

12” wafer

11 12

*IC 廣泛應用於各式各樣電子產品

Consumer

Computer

Communication

Car Industrial

Military

*IC 運算的速度有多快?

以英特爾的 3.7GHz CPU 為例

氧化 擴散 化學氣相沉積 微影術 蝕刻 離子植入 金屬化 化學機械研磨

IC技術發展趨勢

小-元件愈來愈小 大-晶圓愈來愈大 廣-應用愈來愈廣 快-速度愈來愈快 雜-功能愈來愈雜

*元件極小化

1

7.5μm

技術進步

4

5μm

10 3μm

30

2μm

60

1μm

Area=8.75 mil 2 7.5 x 10μm 2

IC製程相關技術

指導老師:林振漢 班級:四電四乙 學生:鄭焜隆 學號:BD92128

目錄

IC簡介 IC主要結構 IC的特性 為何矽晶是IC產業的主流材料? 半導體設備及基本製造技術 IC技術發展趨勢

单片机课程设计答辩参考题目

单片机课程设计答辩单片机课程设计答辩参考参考参考题目题目答辩记录的第二部分要记录2、3个问题个问题。

在在A 类题类题中选一中选一中选一、、两题作答两题作答((所有带框的问题带框的问题只能选一题只能选一题只能选一题));在B 类题中根据自己课题选一类题中根据自己课题选一、、两题作答作答。

注意所选的问题不要太相近注意所选的问题不要太相近,,同一同一个个问题问题在一个在一个在一个班内不要班内不要班内不要重复重复重复选选。

一、 A 类题类题((通用通用题题) 1、 课题设计中你使用了哪些软件,这些软件各自的主要作用是什么?2、 说说Keil 软件的主要功能和作用。

3、 Proteus 软件的主要功能是什么?4、 你所使用的Keil 软件是哪个版本的?如果要编译时生成hex 文件,应该如何设置?5、 在keil 中对C 语言源程序调试时,若要启动调试时直接进入到main 函数,要如何设置?6、 课题中你是用C 语言编程的,使用C 语言编程有什么好处,说说你的看法。

7、 课题中你是用MCS51单片机的汇编语言编程的,使用汇编语言编程有何特点,说说你的看法。

8、 51单片机的C 语言(C51)与标准ANSI C 有何不同,简单谈谈你的体会?9、 51单片机C 语言编程,XBYTE 关键字有什么作用?试举例说明。

10、 C51语言中,如何来定义一个中断服务子程序?11、 C51语言中,中断服务子程序是如何与各自的中断类型对应的(如外部中断0)?试举例说明。

12、 能实现电子电路仿真的软件有很多,如Multisim 、PSPICE 、OrCAD 、EWB 等,Proteus 相对这些软件来说有什么特点?13、 Proteus 仿真软件中,要使用一个+9V 的POWER 电源,要在从哪个工具箱(绘图工具栏)中选取哪个部件,要如何设置成+9V ?14、 Proteus 仿真软件中,如果要使用一个多通道示波器,该从哪个工具箱(绘图工具栏)中选取哪个部件?15、 Proteus 软件中,从元器件库中调出的元件有的不能仿真,为什么?16、 Proteus 仿真时,如何指定单片机所用的程序代码?说说操作方法。

半导体器件与工艺(1)答辩

哈尔滨工程大学

微电子学

半导体基础

电阻率的结构与组分敏感性

用电阻率的高低来区分导体、半导体和绝缘体是不 够严密的 : 某些结构完整且不含杂质的半导体也会有跟 绝缘体不相上下的高电阻率,而当它们含有足够浓度的 某些特殊杂质时,其电阻率又会降到金属电阻率的范围, 甚至比某些导电性欠佳的金属导体的电阻率还低。 半导体是导电能力明显依赖于材料的内外状态的一 类特殊物质。

半导体基础

半导体导电的热敏性

载流子密度是器件特性的决定性因素。从器件工作 特性的稳定性考虑,保持载流子密度的稳定是最基本的 要求。非本征材料在一定的温度范围内主要靠杂质原子 提供载流子,而一个杂质原子最多只能提供一个电子或 空穴。当每个杂质原子都已“尽责”之后,载流子密度 即保持不变,器件即可望保持相应的稳定工作状态。因 此,实际半体器件大多采用掺杂材料。 非本征材料有本征激发和杂质电离两种载流子来源, 其载流子的总密度为二者之和。当本征激发的如状较小 时,靠杂质的完全电离保持载流子的恒定密度。当本征 载流子密度随着温度的升高而接近或超过掺杂浓度时, 非本征半导体即开始向本征半导体转变。

半导体中空穴的导电本质上还是电子的定向运动, 只不过这些电子不是自由电子而是被原子核束缚着的价 电子。半导体电导率表达式

q(nn p p )

则本征半导体电导率表达式

i qni (n p )

常用半导体的载流子迁移率也往往比金属良导体中 的自由电子的迁移率高,但是其电导率却非常小,这是 因为本征载流子浓度与金属中的载流子密度相比很小。

半导体基础

电子在金属和半导体中的能量分布

当温度 T 大于 0K 时,由于电子的平均动能为 3kT/2 ,满带 电子中会有一些能量偏高者越过禁带进入高能量的空带。任 何一个能带能够容纳的电子数很大,而在低温和常温下能够 越过一个宽度只有1eV的禁带的电子也都很少,因而这两个未 满带的特征大不一样,其能量较高者接近全空,能量较低者 接近全满。通常把非零温度下只有少许电子的近空带称为导 带,而把只有少许空状态的近满带称为价带。

IC 常见面时题目的解决方法Interview Questions-Digital Design

Dr Adnan GutubFrom:"Dr. M. E. S. El-Rabaa" <elrabaa@.sa>To:"Aiman El-Maleh" <aimane@.sa>; "alyamani" <alyamani@.sa>;"Alaaeldin Amin" <amin@.sa>; "Ashraf S. Hasan Mahmoud"<ashraf@.sa>; "Dr. Talal Al-Kharobi" <talal@.sa>Cc:<gutub@.sa>Sent:Saturday, March 11, 2006 9:50 AMSubject:Intersting!This is a good test to give to our COE202 students at the end of the semester or to our graduating COE students! Muhammad[ Verilog FAQ | Tips | Online Books | Papers | Free Stuff | Tools | Jobs | What's New ]Sample Questions asked inInterviewsRajesh Bawankule Introduction :A fresh graduate faces some tough questions in his first job interview. The questions themselves aresimple but require practical and innovative approach to solve them. I started collecting some questionsfrom my own experience and from my friends.Note: Please do not send me emails asking for solutions. You are not supposed to answer thesequestions in 10 seconds like some university multiple choice questions. Some questions may havemore than correct answers and some may not even have correct answer :)What matters is your approach to solution and understanding of basic hardware design principles.S ome other pages on interview questions:1. Electrical Engineering Technical Interview Questions/Review : This page has answers too.2. /cse517/interview.htmlRecently added questionsQ. Create 4 bit multiplier using a ROM and what will be the size of the ROM. How can you realize itwhen the outputs are specified.Q. How can you swap 2 integers a and b, without using a 3rd variableQ. Which one is preferred? 1's complement or 2's complement and why?Q. Which one is preferred in FSM design? Mealy or Moore? Why?Q. Which one is preferred in design entry? RTL coding or Schematic? Why?Q. Design a 2 input OR gate using a 2:1 mux.Q. Design a 2 input AND gate using a 2 input XOR gate.Old QuestionsQ. Design a logic which mimics a infinite width register. It takes input serially 1 bit at a time. Output is asserted high when this register holds a value which is divisible by 5.For example:Input Sequence Value Output11100102011015101010101110101210(Hint: Use a FSM to create this)Q. Design a block which has 3 inputs as followed.1. system clock of pretty high freq2. asynch clock input P3. asynch clock input QP and Q clocks have 50% duty cycle each. Their frequencies are close enough and theyhave phase difference. Design the block to generate these outputs.1. PeqQ : goes high if periods of P and Q are same2. PleQ : goes high if P's period is less than that of Q.3. PgrQ : goes high if P's period is greater than that of Q.Q. What's the difference between a latch and a flip-flop? Write Verilog RTL code for each. (This is one of the most common questions but still some EE's don't know how to explain it correctly!)Q. Design a black box whose input clock and output relationship as shown in diagram.__ __ __ __ __ __ __ __ __clk __| |__| |__| |__| |__| |__| |__| |__| |__| |____ __ __ __ __Output __| |________| |________| |________| |________| |__Q. Design a digital circuit to delay the negative edge of the inputsignal by 2 clock cycles.______________________input ________| |______________ _ _ _ _ _ _ _ _ _ _ _ _clock _| |_| |_| |_| |_| |_| |_| |_| |_| |_| |_| |_| |_| |____________________________output _________| |___________Q. Design a Pattern matching block- Output is asserted if pattern "101" is detected in last 4 inputs.- How will you modify this design if it is required to detect same "101" pattern anywhere in last8 samples?Questions:Q.The digital circuit is shown with logic delay (dly3) and two clock buffer delays (dly1, dly2). - How will you fix setup timing violations occurring at pin B?- How will you fix hold violations occurring at pin B?(Hint: Change the values of three delays to get desired effect)Q.Sender sends data at the rate of 80 words / 100 clocksReceiver can consume at the rate of 8 words / 10 clocksCalculate the depth of FIFO so that no data is dropped.Assumptions: There is no feedback or handshake mechanism. Occurrence of data in that time period is guaranteed but exact place in those clock cycles is indeterminate.QOptical sensors A and B are positioned at 90 degrees to each other as shown in Figure. Half od the disc is white and remaining is black. When black portion is under sensor it generates logic 0 and logic 1 when white portion is under sensor.Design Direction finder block using digital components (flip flops and gates) to indicate speed. Logic 0 for clockwise and Logic 1 for counter clockwise.QWill this design work satisfactorily?Assumptions: thold = tsetup = tclock_out = tclock_skew = 1ns.After reset A = 0, B = 1Q. Design a 4:1 mux in Verilog.z Multiple styles of coding. e.g.Using if-else statementsif(sel_1 == 0 && sel_0 == 0) output = I0;else if(sel_1 == 0 && sel_0 == 1) output = I1;else if(sel_1 == 1 && sel_0 == 0) output = I2;else if(sel_1 == 1 && sel_0 == 1) output = I3;Using case statementcase ({sel_1, sel_0})00 : output = I0;01 : output = I1;10 : output = I2;11 : output = I3;default : output = I0;endcasez What are the advantages / disadvantages of each coding style shown above?z How Synthesis tool will give result for above codes?z What happens if default statement is removed in case statement?z What happens if combination 11 and default statement is removed? (Hint Latch inference) (Comments : Though this questions looks simple and out of text books, the answers tosupporting questions can come only after some experience / experimentation.)Q. Design a FSM (Finite State Machine) to detect a sequence 10110.z Have a good approach to solve the design problem.z Know the difference between Mealy, Moore, 1-Hot type of state encoding.z Each state should have output transitions for all combinations of inputs.z All states make transition to appropriate states and not to default if sequence is broken. e.g. S3 makes transition to S2 in example shown.z Take help of FSM block diagram to write Verilog code.Q. One more sequence detector:Design a FSM (Finite State Machine) to detect more than one "1"s in last 3 samples.For example: If the input sampled at clock edges is 0 1 0 1 0 1 1 0 0 1then output should be 0 0 0 1 0 1 1 1 0 0 as shown in timing diagram. And yes, you have to design this FSM using not more than 4 states!!Q. Design a state machine to divide the clock by 3/2.(Hint: 2 FSMs working on posedge and negedge)Q. Draw timing diagrams for following circuit.z What is the maximum frequency at which this circuit can operate?z What is the minimum width of input pulse and position?z Problem can be given interesting twist by specifying all delays in min and max types.Q. Design a Digital Peak Detector in Verilog.Q. Design a RZ (return to zero )circuit. Design a clock to pulse circuit in Verilog / hardware gates.Q. Miscellaneous Basic Verilog Questions:z What is the difference between Behavior modeling and RTL modeling?z What is the benefit of using Behavior modeling style over RTL modeling?z What is the difference between blocking assignments and non-blocking assignments ?z How do you implement the bi-directional ports in Verilog HDLz How to model inertial and transport delay using Verilog?z How to synchronize control signals and data between two different clock domains?[ Verilog FAQ | Tips | Online Books | Papers | Free Stuff | Tools | Jobs | What's New ]Copyright Rajesh Bawankule 1997-2005。

电子课程设计答辩问题

电子课程设计答辩问题一、教学目标本课程的教学目标是使学生掌握电子课程的基本知识和技能,能够运用所学知识进行电子设计与实践。

具体目标如下:1.知识目标:学生能够理解电子元器件的基本原理和特性,掌握电子电路的设计方法,了解电子工程领域的最新发展。

2.技能目标:学生能够熟练使用电子工具和设备,进行电子电路的搭建和调试,具备一定的电子项目设计与实施能力。

3.情感态度价值观目标:学生能够认识到电子技术在现代社会中的重要性,培养对电子工程的兴趣和热情,树立正确的科学态度和创新精神。

二、教学内容本课程的教学内容主要包括电子元器件、电子电路设计、电子项目实践等。

具体安排如下:1.电子元器件:介绍电子元器件的基本原理和特性,包括电阻、电容、电感、二极管、晶体管等。

2.电子电路设计:讲解电子电路的设计方法,包括放大电路、滤波电路、稳压电路等。

3.电子项目实践:安排一定的实践项目,让学生动手搭建和调试电子电路,提高实际操作能力。

三、教学方法为了实现教学目标,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法、实验法等。

具体运用如下:1.讲授法:用于讲解电子元器件的基本原理和特性,以及电子电路的设计方法。

2.讨论法:引导学生对电子工程领域的最新发展进行讨论,培养学生的思考能力和团队协作精神。

3.案例分析法:通过分析具体的电子项目案例,让学生学会将理论知识应用于实际问题中。

4.实验法:安排实践项目,让学生动手操作,提高实际操作能力和创新能力。

四、教学资源为了支持教学内容和教学方法的实施,本课程将准备以下教学资源:1.教材:选用权威、实用的电子教材,为学生提供系统、科学的学习资料。

2.参考书:提供相关的电子技术参考书籍,丰富学生的知识储备。

3.多媒体资料:制作精美的电子课件和教学视频,提高课堂教学效果。

4.实验设备:准备充足的实验设备,确保每个学生都能动手实践,提高实际操作能力。

五、教学评估为了全面、客观地评估学生的学习成果,本课程将采用多种评估方式,包括平时表现、作业、考试等。

工艺过程课程设计问题答辩

工艺过程课程设计问题答辩一、课程目标知识目标:1. 让学生掌握工艺过程的基本概念,理解其在实际生产中的应用。

2. 使学生了解不同类型的工艺流程及其特点,能分析工艺过程中的关键环节。

3. 帮助学生了解工艺参数对产品质量的影响,能运用相关知识优化工艺过程。

技能目标:1. 培养学生运用工艺流程图表达实际生产过程的能力。

2. 提高学生分析工艺问题、提出改进措施的能力。

3. 培养学生团队合作和沟通表达的能力。

情感态度价值观目标:1. 培养学生热爱科学、积极探索工艺知识的兴趣。

2. 增强学生的环保意识,使其关注工艺过程对环境的影响。

3. 培养学生严谨认真、勇于创新的精神,提高对工艺过程的敬畏之心。

课程性质:本课程为实践性较强的学科课程,旨在帮助学生将理论知识与实际生产相结合。

学生特点:学生处于八年级阶段,已具备一定的物理、化学知识基础,好奇心强,善于合作与探究。

教学要求:结合学生特点和课程性质,注重理论与实践相结合,充分调动学生的积极性,提高学生的实践操作能力和问题解决能力。

在教学过程中,注重目标的分解和落实,确保学生能够达到预期学习成果。

二、教学内容本章节教学内容主要包括以下几部分:1. 工艺过程基本概念:介绍工艺过程的定义、分类及其在实际生产中的应用。

教材章节:第一章第一节2. 工艺流程图的绘制:讲解工艺流程图的组成、绘制方法和注意事项。

教材章节:第一章第二节3. 常见工艺流程及其特点:分析不同类型的工艺流程,如化工、机械、电子等行业的工艺流程。

教材章节:第二章4. 工艺参数对产品质量的影响:探讨温度、压力、速度等工艺参数对产品质量的作用。

教材章节:第三章5. 工艺过程优化:介绍工艺过程优化的方法、步骤和案例。

教材章节:第四章6. 实践操作:组织学生进行工艺过程实践操作,巩固理论知识。

教材章节:第五章教学内容安排与进度:第一周:工艺过程基本概念第二周:工艺流程图的绘制第三周:常见工艺流程及其特点第四周:工艺参数对产品质量的影响第五周:工艺过程优化第六周:实践操作与总结教学内容注重科学性和系统性,结合教材章节和教学目标,确保学生能够掌握工艺过程的相关知识,提高实践操作能力。

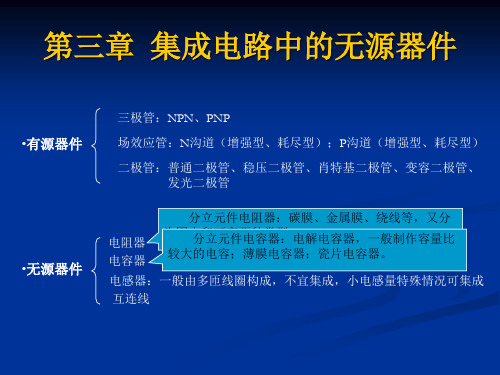

半导体集成电路原理与设计—第三章答辩

100 1500

50 1000

如果电路的某些特性取决于电阻的比值,则电阻比的温度系数可以 降低到200×10-6/℃。因为此时两电阻的载流子迁移率、结深、掺杂浓度 等相同,电阻比只取决于两电阻的L/W之比。所以在设计集成电路时,应 尽量采用电路特性只与电阻比有关的电路形式。

•集成电容器

集成电容器单位面积电容量CA较小,而C=ACA,若达到一定容量,需 要较大面积A。

0.9

0.6

流入,从侧面和背面流入很少,

0.3

端头引入附加电阻,使阻值增

20μm

0.1

大。所以引入端头修正因子K1, 0.4

15μm

30μm

~0

K1取值采用经验值。

K1=0.5方,表示整个端头电阻

0.4

50μm

~0

对总电阻贡献相当于0.5方,对

于大电阻,L>>W,K1可忽略 不计。

不同电阻条宽和端头形状的 端头修正因子

(6) 离子注入电阻,薄层电阻RSBI=0.1-20kΩ /□,由于离子注入对掺 杂浓度控制精度高,所以制作电阻精度高,适合制作高精度电阻。

•基区扩散电阻:

电阻体

电阻电 位高端

PN结隔离

基区扩散电阻结构示意图

P型衬底接低电位

• 阻值估算

R=Rѕ L/W

3.1

Rѕ为基区扩散层薄层电阻,W、L为电阻器的宽度和长度。薄层电阻 的扩散是同NPN管的区扩散同时进行的,Rѕ由NPN管的设计决定,只要 芯片上NPN管的参数确定了,Rѕ就确定了。所以说设计基区扩散电阻主 要就是设计电阻的几何尺寸,即确定W和L;另一种表示方法:确定“方 数L/W”与“条宽W”。

(3.2)

即横向扩散因子m=0.55

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IC 工艺课程设计答辩题目汇总

1、回答TTL电路制造流程,其中第二次氧化做什么用途?说出本次氧化你采用什么方法?

工艺参数是什么?画出紧接着的光刻掩膜板图形、和对应的光刻刻蚀后的剖面图。

2、回答平面三极管制造流程,其中第二次氧化做什么用途?说出本次氧化你采用什么方

法?工艺参数是什么?画出紧接着的光刻掩膜板图形、和对应的光刻刻蚀后的剖面图。

3、回答TTL电路制造流程,在你的流程中,其中氮化硅层做什么用途?说出制作氮化硅层

你采用什么方法?工艺参数是什么?质检参数是什么?画出发射区掺杂之前的剖面图。

4、回答平面三极管制造流程,其中第二次掺杂做什么用途?掺什么杂质?说出本次掺杂你

采用什么方法?工艺参数是什么?质检参数是什么?画出本次掺杂完成后的剖面图。

5、回答TTL电路制造流程,在你的流程中,其中第一次掺杂做什么用途?掺什么杂质?说

出本次掺杂你采用什么方法?工艺参数是什么?质检参数是什么?画出发射区掺杂完成后的剖面图。

6、回答TTL电路制造流程,其中制作氮化硅层之前的氧化膜做什么用途?说出制作该氧化

膜你采用什么方法?工艺参数是什么?要检验那些参数?画出基区掺杂之前的剖面图。

7、回答平面三极管制造流程,其中第一次掺杂做什么用途?掺什么杂质?说出本次掺杂你

采用什么方法?流程单中这一流程是如何设计的?画出本次掺杂完成后的剖面图。

8、回答TTL电路制造流程,其中制作金属膜之前的氧化做什么用途?说出本次氧化你采用

什么方法?质检参数是什么?画出隔离掺杂之前的光刻掩膜板图形和对应光刻刻蚀完成后的TTL剖面图。

9、回答TTL电路制造流程,其中第二次掺杂做什么用途?掺什么杂质?说出本次掺杂你采

用什么方法?工艺参数是什么?质检参数是什么?画出本次掺杂完成后的TTL剖面图。

10、回答TTL电路制造流程,其中第二次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,曝光后要检查哪些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

11、回答TTL电路制造流程,其中第三次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,显影后要检查哪些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

12、回答TTL电路制造流程,其中第四次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,旋转涂胶的工艺参数是什么?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

13、回答平面三极管制造流程,其中制作正面金属层用什么方法?流程单中这一流程是

如何设计的?画出正面金属层完成后的剖面图。

14、回答TTL电路制造流程,其中制作背面金属层用什么方法?工艺参数是什么?要

检查哪些参数?画出基区掺杂之前的光刻的掩膜板图、和对应刻蚀后的剖面图。

15、回答平面三极管制造流程,其中第二次氧化做什么用途?说出本次氧化你采用什么

方法?工艺参数是什么?画出紧接着的光刻掩膜板图形、和对应的光刻刻蚀后的TTL 电路剖面图。

16、回答TTL电路制造流程,其中第三次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,显影后要检查哪些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

17、回答平面三极管制作流程,其中第二次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,旋转涂胶的工艺参数是什么?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

18、回答TTL电路制造流程,其中制作正面金属层用什么方法?工艺参数是什么?要

检查哪些参数?画出发射区掺杂之前的光刻的掩膜板图、和对应刻蚀后的剖面图。

19、回答平面三极管制作流程,其中第三次光刻和刻蚀的目的是什么?写出光刻和刻蚀

的工艺步骤,显影后要检查哪些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。

20、回答TTL电路制造流程,其中第一次光刻和刻蚀的目的是什么?显影的工艺参数

有哪些?刻蚀后要检测那些参数?画出本次光刻的掩膜板图、和对应刻蚀后的剖面图。