TSOP叠层芯片封装的介绍

叠层TSOP封装的开发的开题报告

叠层TSOP封装的开发的开题报告题目:基于叠层TSOP封装的IC集成技术研究与开发一、研究背景自1980年代以来,集成电路技术已经取得了长足的进步。

新的集成技术的出现使得集成芯片的尺寸和整体封装尺寸不断缩小,同时提高了集成度和工作性能。

为了满足市场需求,IC集成技术在不断地更新换代,叠层TSOP封装技术是其中一种较为成熟的技术,可以在较小的面积上放置更多的器件。

二、研究内容本文旨在研究叠层TSOP封装的IC集成技术。

具体研究内容包括:1. 叠层TSOP封装的基本原理和设计方案的研究2. 叠层TSOP封装的制造流程和工艺参数的探讨3. 应用叠层TSOP封装技术设计和制造一款典型IC芯片,并对其性能指标进行测试和分析三、研究方法本研究将采用实验研究和文献调研相结合的方法。

首先通过文献和资料的调研和总结,建立起叠层TSOP封装的基本原理和设计方案,了解其在国内外的应用现状;其次,根据叠层TSOP封装的制造流程和工艺参数的探究,进行相关实验的研究,并通过对实验数据的分析进行结论;最后,应用叠层TSOP封装技术设计和制造一款典型IC芯片,并对其性能指标进行测试和分析。

四、研究意义本研究的结果对于推进集成电路技术的发展,提高芯片封装密度,减小器件体积,提高器件集成度和整体性能具有一定的实用价值和理论意义。

同时,也有助于提升我国集成电路产业在全球市场中的竞争力和地位。

五、研究进度安排1. 第一周:调研叠层TSOP封装的基本原理和设计方案2. 第二周:探究叠层TSOP封装的制造流程和工艺参数3. 第三周:进行相关实验的研究,并对实验数据进行分析4. 第四周:应用叠层TSOP封装技术设计和制造一款典型IC芯片5. 第五周:对设计的典型IC芯片进行性能测试和分析6. 第六周:进一步完善和总结论文,撰写开题报告等相关文献。

六、预期成果1. 在该领域开创性地研究和应用叠层TSOP封装技术,掌握该技术的基本原理和制造流程。

芯片封装原理及分类

芯片封装原理及分类1.芯片封装原理芯片封装是指将微电子器件(包括集成电路、晶体管等)连接到封装基座上的工艺过程。

其原理是将芯片导线通过焊接或焊球连接到封装基座上的金属脚,然后采用封装材料将芯片进行封装。

这样可以保护芯片免受外界环境的影响,并且提供了芯片与外部世界之间的连接接口。

2.芯片封装分类(1)DIP封装(Dual In-line Package)DIP封装是最早的一种芯片封装方式,其特点是通过两排金属脚与外部电路连接。

这种封装方式成本低、可焊接,但体积大,适用于较低密度的集成电路。

(2)SOP封装(Small Outline Package)SOP封装是DIP封装的改进版,其特点是脚距更近,体积更小,适用于较高密度的集成电路。

SOP封装有多种形式,如SOIC(Small Outline Integrated Circuit)、TSOP(Thin Small Outline Package)等。

(3)QFP封装(Quad Flat Package)QFP封装是一种表面贴装封装方式,其特点是四个侧面都带有金属端子,适用于较高密度、中等规模的集成电路。

QFP封装有多种形式,如TQFP(Thin Quad Flat Package)、LQFP(Low-profile Quad Flat Package)等。

(4)BGA封装(Ball Grid Array)BGA封装是一种表面贴装封装方式,在封装基座上布置了一定数量的焊球来实现与外部电路的连接。

BGA封装的特点是密封性好、性能稳定,并且适用于超高密度的集成电路。

BGA封装有多种形式,如CABGA (Ceramic Ball Grid Array)、TBGA(Thin Ball Grid Array)等。

(5)CSP封装(Chip Scale Package)CSP封装是一种紧凑型封装方式,其特点是尺寸和芯片相似,在封装基座上布置了少量焊球或焊盘。

CSP封装的优势在于占据空间小、重量轻、功耗低,并且适用于高密度的集成电路。

芯片叠层结构

芯片叠层结构

3. 硅互连层:硅互连层是芯片叠层结构的关键部分,用于实现芯片之间的电气连接。硅互 连层通常使用TSV(Through-Silicon Via)技术,在芯片表面打孔,然后通过金属填充孔, 实现芯片之间的电连接。

3. 低功耗:芯片叠层结构可以减少信号传输功耗,提供更低的功耗。

芯片叠层结构

4. 灵活性:芯片叠层结构可以根据需要选择不同的芯片组合,实现定制化的功能和性能。

芯片叠层结构在集成电路和微电子领域得到广泛应用,尤其在移动设备、高性能计算和物 联网等领域具有重要意义。

4. 封装材料:封装材料用于固定芯片和硅互连层,并提供机械支撑和保护。常见的封装材 料包括环氧树脂、有机玻璃等。

芯片叠层结构

芯片叠层结构的优点包括:

1. 高集成度:通过将多个芯片堆叠在一起,可以实现更高的集成度,将多个功能模块集成到 一个封装中,减小整体尺寸。

2. 高性能:芯片叠层结构可以实现更短的互连长度,减小信号传输延迟,提供更高的性能。

芯片叠层结构

芯片叠层结构是一种将多个芯片垂直堆叠在一起的封装技术,以实现更高的集成度和性能 。这种结构可以将多个功能模块或器件集成到一个封装中,使得整体尺寸更小、功耗更低, 并提供更高的性能和功能。

芯片叠层结构通常包括以下几个层:

1. 芯片层:每个芯每个芯片 都有自己的电路和引脚。

sd card的芯片封装方式

sd card的芯片封装方式SD卡的芯片封装方式SD卡是一种常见的存储设备,其芯片封装方式对于其性能和使用寿命有着重要的影响。

下面将介绍SD卡的芯片封装方式及其特点。

1. BGA封装(Ball Grid Array)BGA封装是一种常见的封装方式,它采用球形焊盘连接芯片与PCB 板。

BGA封装具有高密度、良好的热性能和电气性能优势,可以在较小的空间中集成更多的功能,适用于高性能和高容量的SD卡。

2. QFP封装(Quad Flat Package)QFP封装是一种常见的封装方式,它采用四个平面引脚连接芯片和PCB板。

QFP封装具有较高的可靠性和良好的电气性能,适用于中等性能和中等容量的SD卡。

3. TSOP封装(Thin Small Outline Package)TSOP封装是一种常见的封装方式,它采用薄型封装,节省空间。

TSOP封装具有较高的集成度和良好的电气性能,适用于低功耗和小容量的SD卡。

4. CSP封装(Chip Scale Package)CSP封装是一种高度集成的封装方式,它将芯片直接封装在最小尺寸的外壳中,减少了封装大小和重量。

CSP封装具有较高的集成度和良好的电气性能,适用于超小容量和高度集成的SD卡。

这些封装方式各有特点,可以根据SD卡的需求选择合适的封装方式。

无论是高性能的BGA封装、中等性能的QFP封装,还是低功耗的TSOP封装和超小容量的CSP封装,都能满足不同应用场景下的需求。

总结起来,SD卡的芯片封装方式多种多样,每种封装方式都有其自身的优势和适用范围。

选择合适的芯片封装方式可以提升SD卡的性能和可靠性,满足不同用户的需求。

低成本高可靠堆叠芯片封装技术

低成本高可靠堆叠芯片封装技术杨建生;谢炳轩【摘要】In an attempt to provide a high density memory solution, especially for workstation and PC server, a stack chips package(referred to as \"SCP\"are as follows: SCP contains a plurality of both memory chips and lead frames within a molded plastic package, chip selection is made through the wire bonding option, resulting in the package with a memory capacity twice or four times that of monolithic chip; plural lead frames are electrically interconnected all at once, using metal solders electroplated on the lead frame surface, and SCP is found reliable and cost competitive when compared to other stack packages because it basically adopts the molded plastic packaging technology as well as the metal solder interconnection method. As electrical interconnection methods, both fluxless soldering joint of Ag/Sn and high pressure mechanical joint of Ag were evaluated extensively and they successfully provided a reliable electrical conduction path without any signal degradation. Temperature cycle test and pressure cooker test were proved not to produce any micro cracks across the joint.%为了提供高密度存储解决方案,特别是工作站和PC服务器,研讨了堆叠芯片封装(SCP)技术.SCP封装技术的主要特点为:在模塑塑料封装内部SCP包含多个双存储芯片和引线框架;芯片挑选通过丝焊技术选择完成,形成单个芯片存储容量2倍或4倍的封装;采用在引线框架表面电镀金属焊料的方法,使多个引线框架与整体实现电连接;与别的堆叠封装相比,SCP封装既可靠又有成本竞争力,原因在于SCP封装主要采用了模塑塑料封装技术以及金属焊料互连方法.作为电互连方法,广泛地评定Ag/Sn无钎剂钎焊点和Ag高压机械焊点,并成功地提供可靠的电传导路径而无任何信号衰减.温度循环试验和高压蒸煮试验证明,沿焊点不会产生任何微裂纹.【期刊名称】《电子工业专用设备》【年(卷),期】2018(000)006【总页数】6页(P23-28)【关键词】无钎剂钎焊点;存储器件;可靠性;堆叠封装【作者】杨建生;谢炳轩【作者单位】天水华天科技股份有限公司, 甘肃天水 741000;天水华天科技股份有限公司, 甘肃天水 741000【正文语种】中文【中图分类】TN403随着电子系统微型化或便携化趋势的不断推进,能够实现高密度产品的封装技术越来越得到系统制造者的关注。

芯片封装类型图解

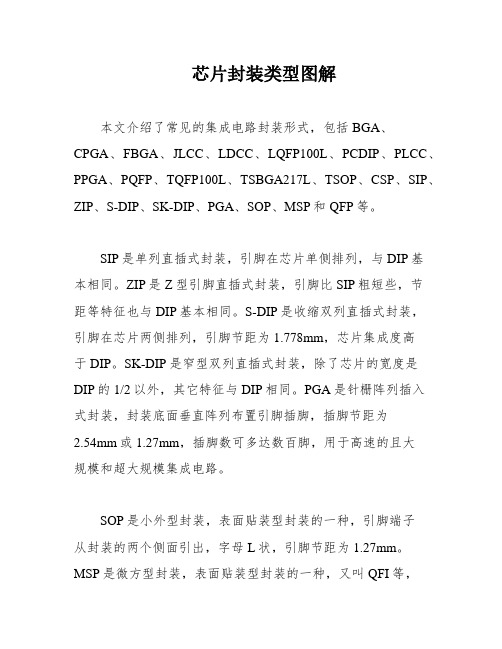

芯片封装类型图解本文介绍了常见的集成电路封装形式,包括BGA、CPGA、FBGA、JLCC、LDCC、LQFP100L、PCDIP、PLCC、PPGA、PQFP、TQFP100L、TSBGA217L、TSOP、CSP、SIP、ZIP、S-DIP、SK-DIP、PGA、SOP、MSP和QFP等。

SIP是单列直插式封装,引脚在芯片单侧排列,与DIP基本相同。

ZIP是Z型引脚直插式封装,引脚比SIP粗短些,节距等特征也与DIP基本相同。

S-DIP是收缩双列直插式封装,引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP。

SK-DIP是窄型双列直插式封装,除了芯片的宽度是DIP的1/2以外,其它特征与DIP相同。

PGA是针栅阵列插入式封装,封装底面垂直阵列布置引脚插脚,插脚节距为2.54mm或1.27mm,插脚数可多达数百脚,用于高速的且大规模和超大规模集成电路。

SOP是小外型封装,表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状,引脚节距为1.27mm。

MSP是微方型封装,表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm。

QFP是四方扁平封装,表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为1.0mm、0.8mm、0.65mm、0.5mm、0.4mm、0.3mm,引脚可达300脚以上。

SVP是一种表面安装型垂直封装,其引脚端子从封装的一个侧面引出,中间部位弯成直角并与PCB键合,适用于垂直安装,实装占有面积很小。

其引脚节距为0.65mm和0.5mm。

LCCC是一种无引线陶瓷封装载体,其四个侧面都设有电极焊盘而无引脚,适用于高速、高频集成电路封装。

PLCC是一种无引线塑料封装载体,适用于高速、高频集成电路封装,是一种塑料封装的LCC。

SOJ是一种小外形J引脚封装,其引脚端子从封装的两个侧面引出,呈J字形,引脚节距为1.27mm。

ssd 芯片的封装方式

SSD(固态硬盘)芯片的封装方式主要有以下几种:1. **BGA (Ball Grid Array)**:这是一种非常常见的封装方式,特别是在高性能的SSD 中。

BGA封装可以提供更好的电气性能和散热性能。

它通过焊球作为外部连接,通常焊接在印刷电路板(PCB)上。

2. **LGA (Land Grid Array)**:这种封装方式与BGA类似,但是使用的是接触垫(land pads)而不是焊球来进行连接。

LGA封装易于安装和升级,因为它不需要焊接到PCB上。

3. **TSOP (Thin Small-Outline Package)**:这是一种较早的封装形式,用于较低容量和较慢速度的SSD。

TSOP封装体积小,但由于其引脚数量限制,通常不适用于大容量或高速率传输的应用。

4. **CSP (Chip-Scale Package) 或者 µBGA (Micro Ball Grid Array)**:这种封装方式尺寸更小,几乎与芯片本身大小相同,适用于空间受限的应用场景。

5. **M.2 (NGFF - Next Generation Form Factor)**:虽然严格来说M.2不是一种芯片封装方式,但它是一种SSD形状规范,它定义了SSD的尺寸、接口和连接方式。

M.2 SSD通常采用BGA封装的NAND闪存。

6. **U.2 (SFF-8639)**:同样,U.2也不是芯片封装方式,而是一种SSD接口规范,主要用于企业级SSD,支持2.5英寸或3.5英寸的驱动器尺寸。

7. **eMMC (embedded MultiMediaCard)**:这是一种集成的存储解决方案,通常用于手机、平板电脑等便携式设备中。

eMMC将NAND闪存和控制器集成在一个小型BGA封装中。

8. **NVMe (Non-Volatile Memory Express)**:这也不是一种封装方式,而是一种基于PCI Express (PCIe) 接口的存储协议,用于访问高速存储介质如SSD。

芯片封装类型图解

集成电路封装形式介绍(图解)BGA BGFP132 CLCCCPGA DIP EBGA 680LFBGA FDIP FQFP 100LJLCC BGA160L LCCLDCC LGA LQFPLQFP100L Metal Qual100L PBGA217LPCDIP PLCC PPGAPQFP QFP SBA 192LTQFP100L TSBGA217L TSOPCSPSIP:单列直插式封装.该类型的引脚在芯片单侧排列,引脚节距等特征和DIP基本相同.ZIP:Z型引脚直插式封装.该类型的引脚也在芯片单侧排列,只是引脚比SIP粗短些,节距等特征也和DIP基本相同.S-DIP:收缩双列直插式封装.该类型的引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP.SK-DIP:窄型双列直插式封装.除了芯片的宽度是DIP的1/2以外,其它特征和DIP相同.PGA:针栅阵列插入式封装.封装底面垂直阵列布置引脚插脚,如同针栅.插脚节距为2.54mm或1.27mm,插脚数可多达数百脚.用于高速的且大规模和超大规模集成电路.SOP:小外型封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状.引脚节距为1.27mm.MSP:微方型封装.表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm.QFP:四方扁平封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为1.0mm,0.8mm,0.65mm,0.5mm,0.4mm,0.3mm,引脚可达300脚以上.SVP:表面安装型垂直封装.表面贴装型封装的一种,引脚端子从封装的一个侧面引出,引脚在中间部位弯成直角,弯曲引脚的端部和PCB键合,为垂直安装的封装.实装占有面积很小.引脚节距为0.65mm,0.5mm.LCCC:无引线陶瓷封装载体.在陶瓷基板的四个侧面都设有电极焊盘而无引脚的表面贴装型封装.用于高速,高频集成电路封装.PLCC:无引线塑料封装载体.一种塑料封装的LCC.也用于高速,高频集成电路封装.SOJ:小外形J引脚封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈J字形,引脚节距为1.27mm.BGA:球栅阵列封装.表面贴装型封装的一种,在PCB的背面布置二维阵列的球形端子,而不采用针脚引脚.焊球的节距通常为1.5mm,1.0mm,0.8mm,和PGA相比,不会出现针脚变形问题.CSP:芯片级封装.一种超小型表面贴装型封装,其引脚也是球形端子,节距为0.8mm,0.65mm,0.5mm等.TCP:带载封装.在形成布线的绝缘带上搭载裸芯片,并和布线相连接的封装.和其他表面贴装型封装相比,芯片更薄,引脚节距更小,达0.25mm,而引脚数可达500针以上.介绍:1 基本元件类型Basic Component Type盒形片状元件(电阻和电容)Box Type Solder ComponentResistor and Capacitor小型晶体管三极管及二极管SOTSmall Outline TransistorTransistor and Diodeelf类元件Melf type Component [Cylinder]Sop元件Small outline package小外形封装TSop元件Thin Sop薄形封装SOJ元件Small Outline J-lead Package 具有丁形引线的小外形封装QFP元件Quad Flat Package方形扁平封装PLCC元件Plastic Leaded Chip Carrier 塑料有引线芯片载体BGABall Grid Array 球脚陈列封装球栅陈列封装CSPChip Size Package芯片尺寸封装2特殊元件类型Special Component Type钽电容( Tantalium Capacitor)铝电解电容(Aalminum Electrolytic Capacitor )可变电阻( Variable Resistor )针栅陈列封装BGABin Grid Array连接器ConnectorIC卡连接器IC Card Connector附BGA 封装的种类APBGAPlastic BGA塑料BGABCBGACeramic BGA陶瓷BGACCCGACeramic Column Grid Array陶瓷柱栅陈列DTBGATape Automated BGA载带自动键合BGAEMBGA微小BGA注芯片的封装技术已经历了好几代的变迁从DIPQFPPGABGA到CSP再到MCM技术指标一代比一代先进包括芯片面积和封装面积之比越来越接近于1适用频率越来越高耐温性能越来越好引脚数增多引脚间距减少重量减少可靠性提高使用更加方便等(MCMMulti Chip Model 多芯片组件)英汉缩语对照SMTSurface Mount Technology 表面贴装技术SMDSurface Mounting Devices 表面安装器件SMBSurface Mounting Printed Circuit Board 表面安装印刷板DIP Dual-In-Line Package 双列直插式组件THTThough Hole Mounting Technology插装技术PCB Printed Circuit Board 印刷电路板SMC Surface Mounting Components表面安装零件PQFP Plastic Quad Flat Package 塑料方形扁平封装SOIC Small Scale Integrated Circuit小外形集成电路LSI Large Scale Integration 大规模集成注意芯片封装图鉴封装大致经过了如下发展进程:结构方面:DIP封装(70年代)->SMT工艺(80年代 LCCC/PLCC/SOP/QFP)->BGA封装(90年代)->面向未来的工艺(CSP/MCM)材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装一.TO 晶体管外形封装TO(Transistor Out-line)的中文意思是“晶体管外形”。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TSOP叠层芯片封装的介绍第六图书馆叠层芯片封装技术,简称3D,是指在不改变封装体外型尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上的芯片的封装技术,它起源于快闪存储器(NOR/NAND)及SDRAM的叠层封装。

叠层芯片封装技术具有大容量、多功能、小尺寸、低成本的特点,2006年以来3D技术逐渐成为主流。

随着NAND快闪存储器市场的高速增长及3D技术的兴起,加之TSOP封装成本低、柔韧性强,所以TSOP封装得以重新焕发生机。

叠层芯片封装技术,简称3D,是指在不改变封装体外型尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上的芯片的封装技术,它起源于快闪存储器(NOR/NAND)及SDRAM的叠层封装。

叠层芯片封装技术具有大容量、多功能、小尺寸、低成本的特点,2006年以来3D技术逐渐成为主流。

随着NAND快闪存储器市场的高速增长及3D技术的兴起,加之TSOP封装成本低、柔韧性强,所以TSOP封装得以重新焕发生机。

叠层芯片封装技术 3D 快闪存储器 TSOP叠层芯片封装 环氧树脂薄膜半导体行业张德洪星科金朋上海有限公司LDP技术部2007第六图书馆第六图书馆TSOP叠层芯片封装的介绍张德洪星科金朋上海有限公司L D P技术部摘要:叠层芯片封装技术,简称3D,是指在不改变封装体外型尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上的芯片的封装技术,它起源于快闪存储器(NOR/NAND)及SD RAM的叠层封装。

叠层芯片封装技术具有大容量、多功能、小尺寸、低成本的特点,2006年以来3D技术逐渐成为主流。

随着NA ND快闪存储器市场的高速增长及3D技术的兴起,加之TSOP封装成本低、柔韧性强,所以T SOP封装得以重新焕发生机。

关键词:叠层芯片封装技术;3D;快闪存储器;TS OP叠层芯片封装;环氧树脂薄膜前言近年来,叠层芯片封装逐渐成为技术发展的主流。

叠层芯片封装技术,简称3D,是指在不改变封装体的尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上的芯片的封装技术,它起源于快闪存储器(NOR/NAND)及SDRAM的叠层封装。

叠层芯片封装技术对于无线通讯器件、便携器件及存储卡来讲是最理想的系统解决方案。

近年来,手机、PD A、电脑、通讯、数码等消费产品的技术发展非常快,这些行业的迅猛发展需要大容量、多功能、小尺寸、低成本的存储器、DSP、ASI C、R F、M EM S等半导体器件,于是叠层芯片技术在近几年得到了蓬勃发展。

3D封装技术的有以下几个特点:1多功能、高效能2大容量高密度,单位体积上的功能及应用成倍提升3这种新技术带来了新一轮的技术革新低成本近几年来在NAND封装领域发展最快的是SIP。

但是,T SO P仍然是大容量NAND的一个主要的解决方案。

和SI P相比,TSO P更具有柔韧性,因为T SOP可能通过SM D制作成SD卡、M i ni SD卡、CF卡或是集成到M P3/M P4、SDRAM中,Si P一旦完成组装,它就是成品了、不能再根据市场需求来进行调整。

和另一种同样可以通过S MD组装的PBG A封装形式相比,TSOP具有非常明显的成本优势。

TSO P单芯片封装工艺介绍半导体封装工艺分为两段,分别叫前道(Fr ont-of-l i ne,FO L)和后道(End-of-l i ne,EO L),前道(FO L)主要是将芯片和引线框架(L eadf r am e)或基板(Subsr t at e)连接起来,即完成封装体内部组装。

后道(EOL)主要是完成封装并且形成指定的外形尺寸。

单芯片TSO P生产工艺流程如下:一、前道生产工艺:封装测试2007/127第六图书馆半导体行业338半导体行业半导体行业SEMICONDUCT OR INDUSTRY二、后道生产工艺:由于单芯片与叠层芯片的后道生产工艺是相同的,所以我们不多作叙述。

多芯片TSO P 封装技术首先我们来看看如何根据封装名称来识别叠层芯片封装中有多少个芯片。

比如,“T S OP 2+1”就是指一个TS OP 封装体内有两个活性芯片、一个空白芯片,如果我们说“T S O P 3+0”,那就是说一个TSOP 封装体内有三个活性芯片、没有空白芯片,以此类推。

下图是最典型的TSOP2+1的封装形式剖面图,上下两层是真正起作用的芯片(A ct i ve D i e ),中间一层是为了要给底层芯片留出焊接空间而加入的空白芯片(空白芯片)。

空白芯片由硅片制成,里面没有电路。

为了要实现叠层芯片封装,显然,我们需要多次的贴片(D /A )及引线键合(W/B )。

例如上图中的TSOP 2+1,我们需要三次贴片(D/A )、两次引线键合(W /B)。

一最简单的TSO P 叠层芯片的封装工艺:下面,我们以最简单的二芯片叠层封装(T S OP 2+X )为例,看看其工艺流程:第一种方法,仍然沿用单芯片封装的液态环氧树脂作为芯片粘合剂、多次重复单芯片的工艺,其工艺流程如下:第二种方法,使用环氧树脂薄膜作为芯片贴合剂。

这种方法需要改变原材料,用环氧树脂薄膜胶带替代传统的蓝膜(如SPV224)。

下图是使用环氧树脂薄膜胶替代蓝膜后装片工序的情形,装片完成后,环氧树脂薄膜就已经和芯片粘在了一起:用固态的环氧树脂模薄膜替代了液态环氧树脂混合液,其好处是在贴片工序时我们只需要将芯片贴到引线框架上,不再需要在引线框架涂一层液态环氧树脂,这就大大简化了工艺。

工艺流程如下:采用上述两种方法来实现TSOP2+1封装都是可行的。

对比以上两种工艺,我们可以发现第二种工艺流程少了两次烘烤,第二种方法生产工艺简单、生产周期比第一种方法短,而且,由于多次烘烤会造成引线框架氧化及芯片粘污,烘烤次数减少对提高成品率和减少可靠性失效也很有好处。

另一种最简单的方法是,TSOP2+0,将两个芯片错开一点位置,采用环氧树脂薄膜作为芯片贴合剂。

但是这种方法,需要改变晶圆的生产工艺,将焊盘都放置在芯片的一端,如下图所示,仅一端有焊线:2007/12第六图书馆半导体行业3第三种方法,如果我们使用的机器可以在同时完成多次贴片,则实际上贴片工序就更加简单,实际只有一次,这样它的生产工艺甚至比单芯片封装还好简单。

对比上述三种叠层芯片的封装工艺,它们的优缺点如下:上述三种叠层芯片的封装工艺,第一种,使用环氧树脂银浆,成本低,但是工艺难度很高、成品率低,即使是最简单的TSO P2+1其成品率能达到99.5%就几乎不可能再提升了,由于其工艺性差,目前不能使用更高高密度的封装中。

第二种,虽然环氧树脂薄膜成本高,但是由于环氧树脂薄膜是在装片(W /M )的时候粘贴到芯片背面,不必考虑液态环氧树脂工艺的复杂性,所以工艺简单、成品率高,成品率可达99.9%。

第三种,由于只有两次贴片(D /A)、一次引线键合(W /B ),所以不仅工艺简单、成品率高,可以稳定在99.90%以上,而且成本相对也比较低。

如果我们将成品率与成本相结合,最好的方法显然是第三种,成本最低、工艺最简单。

但是,这种工艺有其局限性,需要改变芯片的制作布局,将焊盘布置在芯片的一端,如果晶圆的布线无法做到,则无法实现。

第二、第三种方法,都可以用于更密度的封装中,T S OP 4+0、TS OP 5+0、TSOP4+3等等都是在TSOP 2+X 基础上发展起来的。

二、使用液态环氧树脂银浆作为粘合的最重要问题芯片破裂(D i e C r ack)的解决:接下来,我们需要进一步讨论贴片(D /A )最复杂的问题:芯片破裂(D i e C r ack)及引线键合(W /B )的关键参数的优化问题,这两个问题叠层芯片封装工艺成功与否的关键。

如果采用环氧树脂银浆作为芯片粘合剂,其最难解决的的技术问题是在完成塑封工序以后的芯片破裂(D i e C r ack),在单芯片封装时我们不会面对这个问题,因为芯片厚度较大,在0.28mm 左右,而对于叠层芯片封装,就算是最简单的TSOP2+1,其芯片的厚度也只有0.1mm 左右,非常容易破裂。

典型的芯片破裂(D i e C r ack)如下,其破裂呈现出网状:其破裂呈现出网状,通常我们在单芯片封装中看到大多都是一条或几条裂纹,而且是在贴片(D/A)出现,不会在塑封(M OL D)以后出现。

这种多芯片的网状芯片破裂(Di e C r ack),由于我们在贴片(D /A )无法检测、在塑封(M O LD)结束以后我们需要采用有损检查(即开盖)才能发现,就算是我们进行有限的开盖检查,我们也只能看到上层芯片,对于下层芯片我们照样很难看到,所以我们很难知道什么情况下会芯片破裂(D i e C r ack),也就很难解决这个问题。

开盖是一种有损检查,采用强酸将芯片上面的环氧树脂腐蚀掉,将芯片重新裸露在外。

首先我们来分析这种芯片破裂(D i e C r ack)发生的机理。

在叠层芯片封装中,由于液态环氧树脂的流动性强,所以在贴片工艺中,我们通常难以保证环氧树脂能够完全充满两层芯片之间的空隙,如上图所示。

注塑工序所使用的环氧树脂,和贴片(D /A )是不一样的,注塑所使用的环氧树脂,其成份中含有大量50-125um 的颗粒。

通常,我们在贴片(D )形成的环氧树脂层的厚度介封装测试2007/129/A 第六图书馆半导体行业半导体行业SEMICONDUCT OR INDUSTRY于12-38u m ,这就意味着,只有少量小颗粒的注塑工序所使用的环氧树脂混合物可以进入这层空间,而大量大颗粒则只能在外围。

于是,在注塑过程中,由于我们在施加很大的压力(通常压强在10MP a 左右),由于中间的空隙不能被塑封料填充,于是芯片就在外力的作用下被压碎。

这就是使用液态环氧树脂作为芯片粘合剂时为什么会在注塑工序完成后会有网状的芯片破裂(D i e C r ac k)的原因。

这种芯片破裂(D i e C r ack),由于液态环氧树脂很难控制其流动性,我们很难解决。

下面,我们来讨论如何解决。

首先,我们来看看,如果超声波扫描来实现无损方法检测芯片破裂(D i e C r ac k)。

通常的超声波扫描,我们使用反射模式,这种方式我们只能得到一个比较清晰的层面。

最简单的办法,我们使用穿透模式,凡是有阴影的地方就是可疑点。

当然,这种方法仍然不能告诉我们有没有芯片破裂(D i e C r ack),只能预警。

更好的方法,是TA M I(To m o g r a ph i c A c ou s t i c M i c r o I m ag i n g ),它是一种逐层超声波扫描的方法:下图就是一个用逐层超声波扫描法(T AM I )扫描的样图,我们可以很显看出有网状的芯片破裂(Di e Cr a ck ):有了好的检查方法,于是我们就可以方便地进行实验,优化工艺控制以解决芯片破裂(D i e Cr ac k)。