多功能数字钟的设计

多功能数字钟设计报告

电子设计竞赛设计报告多功能数字钟专业班级姓名时间多功能数字钟摘要:本文将介绍一种带有温度显示功能的电子钟。

电子钟由单片机系统、可编程逻辑器件、LED 显示、温度传感器、语音报时系统等组成。

该电子钟具有闹钟功能,并可以整点语音报时,是一种多功能的数字钟。

关键词:89C51,EPM240,AD590,ISD1420一、设计要求:1.任务设计制作一个24小时制多功能数字钟。

2.要求(1)基本要求●具有时间设置(小时和分钟)、闹钟时间设置、闹钟开、闹钟关功能。

●数字显示小时、分钟、秒,有AM、PM指示器,闹钟就绪灯,蜂鸣器(2)发挥部分●具有整点用语音报时功能;●具有温度显示功能;●按键控制应尽可能少。

二、方案比较、设计与论证1.控制器件选择为使电子钟能够运行,须有主控器件。

我们考虑了三种器件选择方案方案一:采用单片机89C51(89V51、89C52及类似产品)。

该方案的优点是单片机价格便宜,ROM容量较大,可以实现电子钟简单功能;缺点是编程语句繁琐冗长,复杂功能占用CPU 时间长,容易产生不必要的延时,使得时钟不够准确,而且I/O引脚不足,需要大量外接设备。

方案二:采用可编程器件EPF10K20RC208-3。

该方案的优点是所有功能都由器实现,系统结构明确、简洁;缺点是价格过于昂贵。

方案三:采用单片机89C51及可编程器件EPM240。

该方案的优点是混合了两种控制器件的优点,由单片机主控逻辑部分,可编程器件处理其它功能,系统稳定;缺点是较第一种略贵,但可以接受。

权衡利弊,第三种方案可互补一二方案的优缺,我们决定采用方案三以实现系统的控制功能。

2.温度器件选择该系统要求完成温度显示功能。

基于上述原因,我们考虑了两种方案:方案一:采用温度控制器件DS18B20。

该方案的优点是集成温度传感器和A/D转换功能,直接输出数字信号;缺点是不易购买。

方案二:采用温度传感器AD590和模数转换器AD0809。

该方案实现较复杂,需要连接各种电桥元件,但是可以通过使用学习控制系统的部分原理应用,而且价格便宜,容易获得。

多功能数字钟-电子设计

多功能数字钟-电子设计

第一步实现多功能数字钟的基本功能,包括显示当前时间和设置定时

功能。

为了实现这一功能,我们需要使用一个定时器,以实现每秒钟更新

一次时间并显示在LCD屏上,同时实现定时功能。

第二步用一个按钮来切换显示当前时间和定时时间。

为了实现这一功能,我们需要在LCD屏上显示当前时间和定时时间,当按钮按下时,可以

改变当前时间和定时时间的显示。

第三步加入计时功能,使用者可以设置一个计时时间,当计时结束时,会有一个提醒和发出报警声。

为了实现这一功能,我们需要使用一个计数器,计算出时间差,当到达设定的计时时间时,发出报警声或者显示一个

提醒。

第四步增加闹钟功能,使用者可以设置一个闹钟时间,当达到闹钟时

间时,会有一个提醒和发出报警声。

为了实现这一功能,我们需要在指定

的时间段内,获取当前时间,通过一个实时检查程序,来实现闹钟功能,

当到达时间时,发出报警声或者显示一个提醒。

第五步加入天气预报功能,使用者可以查询当前城市的天气情况,以

及未来三天的天气预报。

为了实现这一功能,我们需要使用一个API来获

取天气情况,并将获取的信息在LCD屏上显示出来,方便使用者查询。

多功能数字钟设计

多功能数字钟设计1 设计任务与要求设计一个具有“时”、“分”、“秒”显示的数字钟,具体要求:(1)具有正常走时的基本功能;(2)具有校时功能(只进行分、时的校时);(3)具有整点报时功能;(4)具有定时闹钟功能;(5)秒信号产生电路采用石英晶体构成的振荡器;(6)写出设计步骤,画出设计的逻辑电路图;(7)对设计的电路进行仿真、修改,使仿真结果达到设计要求;(8)安装并测试电路的逻辑功能。

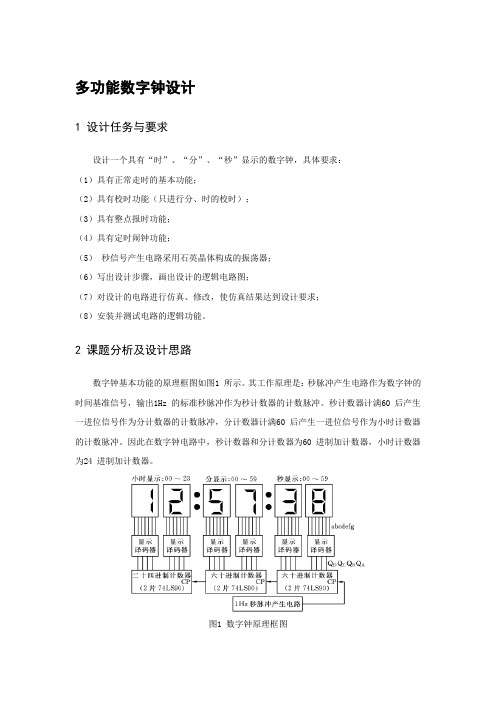

2 课题分析及设计思路数字钟基本功能的原理框图如图1 所示。

其工作原理是:秒脉冲产生电路作为数字钟的时间基准信号,输出1Hz 的标准秒脉冲作为秒计数器的计数脉冲。

秒计数器计满60 后产生一进位信号作为分计数器的计数脉冲,分计数器计满60 后产生一进位信号作为小时计数器的计数脉冲。

因此在数字钟电路中,秒计数器和分计数器为60 进制加计数器,小时计数器为24 进制加计数器。

图1 数字钟原理框图2.1 秒脉冲产生电路的设计秒脉冲产生电路是数字钟的核心,它的稳定度和精确度决定了数字钟走时的准确度。

因此通常选用石英晶体振荡电路。

图2 是由集成电路CD4060(14 位二进制串行计数器)和石英晶体构成的一种典型的脉冲产生电路,图中晶振的谐振频率为32768Hz,经CD4060 内部的14 级二分频器后,从Q4~ Q10 和Q12~ Q14 各输出端可分别得到频率为2048 Hz,1024 Hz,512 Hz,256 Hz,128 Hz,64 Hz,32 Hz,8 Hz,4 Hz 和2 Hz 的脉冲信号。

将2Hz 信号再经一个外接的二分频电路即可得到1Hz 的秒脉冲信号。

图2 石英晶体振荡器构成的秒脉冲电路2.2时、分、秒计数器的设计分和秒计数器均为 60 进制加计数器,秒计数器为24 进制加计数器,它们可分别由两片74LS90 级联并采用“反馈清零法”构成,设计中的难点是各个进位信号的产生。

2.3 校时电路的设计当数字钟接通电源或走时出现误差时,需要校时。

多功能数字钟设计

port map(clk=>clk1s,clr=>disable,en=>s_mh_en,count=>s_mh);

SET_H: counter

generic map( count_value => 23)

port map(clk=>clk1s,clr=>disable,en=>s_h_en,count=>s_h);

architecture rtl of TIMER is

Begin

定义语句区

End rtl;

功能描述(并发描述语句)

㈠时钟信号生成功能部分

signal clk1s: std_logic; --1s计数时钟

signal cnt: std_logic_vector( 9 downto 0);

signal dy : std_logic; --整点报时控制时钟,50’’、52”、54”、56”、 58” generat_1s_clock: PROCESS (scanclk)

h<=c_h when set = '0' else s_h; hh<=1 when h>=10 and h<20 else

2 when h>=20 else 0; hl<=(h-0) when h<10 else (h-10) when h>=10 and h<20 else (h-20);

㈢闹表计时功能描述

signal s_ml_en , s_mh_en, s_h_en : std_logic; 定义语句区

signal s_mh,: integer range 0 to 5;

signal s_ml: integer range 0 to 9;

(数电)多功能数字钟—设计报告

1、设计内容及要求:①基本功能:以数字形式显示时、分、秒的时间,小时计数器的计时要求为24进制,并要求手动快校时、校分。

②扩展功能:整点报时。

2、系统设计原理:系统要求:数字电子钟由555集成芯片构成的振荡电路、计数器、译码器、显示器和校时电路组成。

555集成芯片构成的振荡电路产生的信号作为秒脉冲,秒脉冲送入计数器,计数结果通过“时”、“分”、“秒”译码器显示时间。

在功能方面,对于本次综合设计,还要求有校时与整点报时功能。

方案设计:图1. 数字钟电路框图电子钟的计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能和报时功能。

因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校时电路、报时电路和振荡器组成。

主电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路组成。

系统工作原理:秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,用555振荡器来实现。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态用七段显示译码器译码,通过七段显示器显示出来。

校时电路时用来对“时”、“分”显示数字进行校对调整。

3.单元电路的设计:3.1、基于555电路的秒脉冲发生器的设计3.1.1用555芯片设计一个多谐振荡器,输出方波用作计数器。

脉冲频率公式:f=1/(R1+2R2)C㏑2选择R1=1K,R2=5K,RV1=2K,C=100nF,形成电路图如图所示:图2. 555振荡器电路图仿真波形如图所示图3. 555脉冲仿真波形图555振荡器输出f=1000HZ,通过分频得出1HZ的脉冲,此脉冲当做秒时针脉冲。

电子综合设计多功能数字钟报告

电子综合设计多功能数字钟报告报告内容如下:一、设计目的和原理多功能数字钟是一种能够显示时间,并具有闹钟、计时、倒计时等功能的电子设备。

本设计的目的是通过FPGA实现一个多功能数字钟的功能,以实现时间的显示和闹钟的设置功能。

二、设计方案和实现1.硬件设计方案:本设计使用FPGA作为主控芯片,使用七段数码管作为显示器,通过与FPGA的IO口连接来实现时间的显示功能。

同时,使用按键作为输入进行功能的选择和设置。

2.硬件连接:将FPGA的IO口连接到七段数码管的控制端,通过IO口输出相应的数字信号来控制数码管的亮灭。

将按键连接到FPGA的IO口,通过IO口输入按键的信号。

此外,还需要连接一个晶振电路来提供时钟信号。

3.软件设计方案:本设计使用VHDL语言进行程序设计,通过状态机来实现多功能数字钟的功能。

具体实现包括时间的显示、闹钟的设置和启动、计时和倒计时功能的实现。

通过按键的输入来切换不同的状态,实现不同功能的切换和设置。

4.软件实现具体步骤:(1)定义状态机的状态,包括时间显示、闹钟设置、计时和倒计时等状态。

(2)在时间显示状态下,通过FPGA的IO口输出相应的数字信号来控制七段数码管的亮灭,实现时间的显示。

(3)在闹钟设置状态下,通过按键的输入来设置闹钟时间,并将设置好的时间保存在寄存器中。

(4)在计时和倒计时状态下,通过按键的输入来实现计时和倒计时功能,并通过七段数码管的显示来实时显示计时和倒计时的时间。

以下为本设计的完整程序代码:```vhdl--时钟频率--定义状态signal state : state_type;--定义时钟、按键和数码管信号signal clk : std_logic;signal key : std_logic_vector(1 downto 0);signal seg : std_logic_vector(6 downto 0);--闹钟时间寄存器signal alarm_hour_reg : std_logic_vector(5 downto 0);signal alarm_min_reg : std_logic_vector(5 downto 0);--计时和倒计时寄存器signal count_up_reg : std_logic_vector(23 downto 0); signal count_down_reg : std_logic_vector(23 downto 0); signal count_down_flag : std_logic := '0';beginclock : processbeginwhile true loopclk <= '0';wait for 10 ns;clk <= '1';wait for 10 ns;end loop;end process;key_scan : process(clk)beginif rising_edge(clk) thenkey <= key_scan_func; -- 按键扫描函数end if;end process;fsm : process(clk, key)beginif rising_edge(clk) thencase state isif key = "10" then -- 第一个按键按下state <= set_alarm;elsif key = "01" then -- 第二个按键按下state <= count_up;end if;when set_alarm =>seg <= set_alarm_func; -- 闹钟设置函数if key = "00" then -- 两个按键同时按下elsif key = "01" then -- 第一个按键按下state <= count_up;end if;when count_up =>seg <= count_up_func; -- 计时函数if key = "00" then -- 两个按键同时按下elsif key = "10" then -- 第二个按键按下state <= count_down;count_down_flag <= '1';end if;when count_down =>seg <= count_down_func; -- 倒计时函数if key = "00" then -- 两个按键同时按下count_down_flag <= '0';elsif key = "01" then -- 第一个按键按下state <= count_up;count_down_flag <= '0';end if;end case;end if;end process;--数码管信号和显示模块的连接display : entity work.seg_displayport mapclk => clk,seg => segend architecture;```四、总结与展望通过FPGA实现多功能数字钟的设计,在硬件和软件的配合下,实现了时间的显示和闹钟的设置功能。

多功能数字钟电路设计

多功能数字钟电路设计

1.时钟显示:设计一个数字时钟显示电路,可以显示当前的时间(小

时和分钟)。

可以使用七段显示器来显示数字。

2.闹钟功能:设计一个闹钟功能,可以设置闹钟时间,并在到达闹钟

时间时发出提示声音或闹铃。

3.温度显示:设计一个温度传感器电路,并将当前温度显示在数字时

钟上。

4.日历功能:设计一个日历功能,可以显示当前的日期和星期。

5.定时器功能:设计一个定时器功能,可以设置一个特定的时间间隔,并在到达时间间隔时发出提示声音或闹铃。

6.闹钟休眠功能:设计一个闹钟休眠功能,可以设置一个特定的时间

间隔,在此时间间隔内按下按钮可以将闹钟功能暂时关闭。

7.闹钟重复功能:设计一个闹钟重复功能,可以设置一个特定的时间

间隔,使闹钟在每天相同的时间段重复响铃。

8.亮度调节功能:设计一个亮度调节功能,可以调整数字时钟的显示

亮度。

这些功能可以根据需求进行组合设计,可以使用逻辑门、计数器、显

示器驱动器、温度传感器、按钮等元件来完成电路设计。

多功能数字钟设计

数字电子钟实验报告一、课程设计的内容及要求1.设计一个数字电子钟电路。

要求:a)按24小时制直接显示“时”、“分”、“秒”。

b)当电路发生走时误差时具有校时功能。

c)具有整点报时功能。

d)具有闹钟功能。

2.中、小规模集成电路组成数字电子钟,并在实验仪器上进行组装和测试。

二、数字钟的基本工作原理数字钟一般都由计数器、译码器、显示器等几部分组成。

不同进制的计数器、译码器和显示器组成计时系统。

秒信号送入计数器进行计数,把累计的结果以“时”、“分”、“秒”、“星期”的数字显示出来。

多功能数字钟设计原理图:多功能数字钟设计电路图:1、分频电路48分频原理图2分频模块原理图1000分频模块60进制秒、分计数器24进制小时计数器7进制星期计数器校时电路报时电路显示电路闹钟电路三、实验小结通过这次装数字电子钟的实验,使我们有机会来实践我们平日里所学的理论知识,更好地做到学以致用。

由于还有许多理论知识不知道,这就促使我去查阅相关资料,通过这种方式我又学到了以往在课堂里老师未曾提到过的知识,体会到了自己自己获得知识的乐趣。

这次实验,不仅锻炼了我的动手能力,还让我们体会到了要做一件事,细心和耐心的重要性。

在此次的实验中,我遇到了许多未曾料到的错误和失误,当理论已经通过的时候,实践是却又有很多问题,通过这一点,我们深刻理解了理论与实践的不同,实践不仅涉及到课堂中所学习到的知识,更考验我们对现实问题的灵活处理的能力。

这样的一次经历确实受益匪浅。

最后,感谢老师这么多天的耐心指导和帮助!。

多功能数字钟设计

EDA实验设计(II)--多功能数字钟设计姓名:学号:院系:指导老师:目录一,内容摘要…………………………………. 二,引言……………………………………. 三,实验要求………………………………四,方案论证…………………………………五,各模块设计……………………………….1,频率产生电路……………………….2,基本计数电路……………………….3,动态显示电路……………………4,清零,保持电路………………….5,快速校分校时校星期电路……….6,整点报时电路……………………………7,闹钟彩铃电路……………………………六,实验中遇到的问题及解决方案………………七,总结与体会……………………………………一,内容摘要中文摘要本实验利用QuartusII软件,结合所学的数字电路的知识设计一个24时多功能数字钟,具有正常分、秒计时,动态显示,保持、清零、快速校分、整点报时、闹钟功能。

文章分析了整个电路的工作原理,还分别说明了各子模块的设计原理和调试、仿真、编程下载的过程,并对最终结果进行总结,最后提出了在实验过程中出现的问题和解决的方案。

通过实验掌握了一些逻辑组合器件的基本功能和用法,同时体会到了利用软件设计电路的方便快捷,避免了硬件布线的繁琐,提高了效率。

关键词数字计数器动态显示保持清零快速校分整点报时闹钟软件设计外文摘要Title DIGITAL CLOCKDESIGN PROPOSAlAbstractUsing the QuartusII, we design a digital clock of 24 hours with learning electric circuit knowledge. The circuit can keep the time, display, reset, adjust the minute and hour, ring the time in the round number time and alarm clock.The paper has analyzed the principle of all work andexplained the designing principle of different parts separately. By debugging, simulating, compiling, programming, Iput forward a matter and give a settling plan.I know about the basic functions and using method of some electric pieces in this experiment. At the same time,I realized the convenience of making use of the software to carry on the electric circuit,which is fast, avoided the hardware cloth line tedious, and raised the efficiency.Keywords digital counter, dynamic display, keep, clear, check time, time, alarm clock,software design二,引言由于传统硬件电路在设计存在资源浪费,连线麻烦,出错率高且不易修改,很难控制成本,而软件电路设计连线方便,修改容易,电路结构清楚,功能一目了然,软件内部提供有丰富的元件库;节省实验时间,故障率低,出错时,有错误提示,明显提高了效率。

多功能数字钟的设计

1多功能数字钟的设计1.1设计要求设计一个能进行时、分、秒计时的十二小时制或二十四小时制的数字钟,并具有定时与钟功能,能在设定的时间发出闹铃音,能非常方便地对小时、分钟和秒进行手动调节以校时间,每逢整点,产生报时音报时。

系统框图如图1-1所示:系统模式手动IHZ时钟源复位选择校时输入图IT多功能数字钟系统框图显示部分可以使用数码管(基本)或液晶LCD(扩展)。

1.2设计提示此设计问题可分为主控电路、计数器模块和扫描显示三大部,主控电路中各种特殊功能的实现设计问题的关键。

用两个电平信号A、B进行模式选择,AB=OO为模式0,系统为计时状态;AB=Ol为模式1,系统为手动校时状态;AB=Io为模式2,系统为闹钟设置状态。

设置一个turn信号,当turn=0时,表示在手动校对时,选择调整分钟部分;当turn=l 时,表示在手动校对时,选择调整小时部分。

设置一个Change信号,在手动校时或闹钟设置模式下,每按一次,计数器加1。

设置一个reset信号,当reset=O时,整个系统复位;当reset=1时,系统进行计时或其他特殊功能操作。

设置一个闹钟设置信号resell,当resetl=O时,对闹钟进行设置,当resetl=O时,关闭闹钟信号。

设置状态显示信号(连发光二极管):LD_alert指示是否设置了闹铃功能;LDjI指示当前调整的是小时信号;LD_m指示当前调整的是分钟信号。

当闹钟功能设置后(LD_alert=l),系统应启动一个比较电路,当计时与预设闹铃时间相等时,启动闹铃声,直到关闭闹铃信号有效。

整点报时部分由分和秒计时同时为0(或60)启动,与闹铃共用一个扬声器驱动信号OUto 系统计时时钟为Clk=IHz,选择另一时钟clk」k=1024Hz作为产生闹铃声、报时音的时钟信号。

主控电路状态表如表1-1所示。

硬件系统示意图如图1-2所示。

晶振[OOO1.D_hLD_mMs6Ms5..LD_alertclkjkClkFP∈Λ∕(PLDturnchangeresetreset1AIIII IIII IIII LlL∣abCdefg图1-2数字钟硬件系统示意图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字钟设计

一、工作原理

设计一种简易数字钟,该数字钟具有基本功能,包括准确计时,以数字形式显示时、分,以二极管显示秒的时间和校时功能。

实现以下功能:

(1)时的计时要求为24进制,分和秒的计时要求为60进制。

(2)准确计时,以数字形式显示时,分时间,用两个二极管显秒的时间。

(3)校正时间。

二、电路分析

1. 设计原理及思路

数字钟实际上是一个对标准频率进行计数的计数电路。

它的计时周期是24小时,由于计数器的起始时间不可能与标准时间一致所以采用校准功能和报时功能。

数字钟电路主要由译码显示器、校准电路、报时电路、时计数、分计数、秒计数器,振荡电路和单次脉冲产生电路组成。

其中电路系统由秒信号发生器、“时”、“分”、“秒”计数器、译码器及显示器、校准电路、整点报时电路组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现,将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个时脉冲信号,该信号将被送到时计数器。

时计数器采用24进制计时器,可实现对一天24小时的计时。

译码显示电路将“时”、“分”、“秒”计数器的输出状态通过显示驱动电路,七段显示译码器译码,在经过六位LED 七段显示器显示出来。

整点报时电路时根据计时系统的输出状态产生一个脉冲信号,然后去触发一蜂鸣器产生声音。

校准电路时用来对“时”、“分”、“秒”显示数字进行校对调整的。

根据设计要求首先建立了一个简易数字钟电路系统的组成框图,框图如下图所示。

2.设计步骤与方法

(1) 振荡电路

数字电路中的时钟是由振荡器产生的,振荡器是数字钟的核心。

振荡器的稳定度及频率的精度决定了数字钟计时的准确程度,振荡器的频率越高,计时精度越高。

方案一:石英晶振

因为想到要使产生的脉冲较稳定,我们首先想到了使用石英晶振电路,即采用37267Hz晶体震荡器,电路图如图

工作原理:由晶体振荡器产生37268Hz的1KHz的脉冲经集成块CD4060分频后变为10Hz 脉冲,再经74LS160计数器分频得到了所需要的1Hz稳定脉冲。

方案二:555定时器

振荡电路由555构成的自激多谐振荡器直接产生 1Hz时钟脉冲频率。

555定时器

注:电路中R2为一可调电阻,我们可以通过调节R2的阻值获得所需的1H的秒脉冲,而需要采用分频电路。

方案选择:刚开始的时候我们选择555作为发生器,因为我们刚刚才学过,可以根据要求设计出1hz频率。

但经过和大家的讨论,觉得晶振电路产生频率高、更精确,所以最终选用晶振电路的方案。

(2) 计数电路

数字钟的计数电路是用两个六十进制计数电路和24进制计数电路实现的。

数字钟的计数电路的设计可以用反馈清零法。

当计数器正常计数时,反馈门不起作用,只有当进位脉冲到来时,反馈信号将计数电路清零,实现相应模的循环计数。

以60进制为例,当计数器从00,01,02,……,59计数时,反馈门不起作用,只有当第60个秒脉冲到来时,反馈信号随即将计数电路清零,实现模为60的循环计数。

下面将分别介绍60进制分秒计数器和24进制小时计数器。

60进制计数电路

24进制电路

(3)译码显示电路

译码和数码显示电路是将数字钟和计时状态直观清晰地放映出来,被人们的视觉器官所接受,它的任务就是将计数器输出的8421BCD码译成数码器显示所需要的高低电平。

这里所选用的译码器就是常用的BCD译码/驱动器74LS48,其中A1、A2、A3、A4与计数器的四个输出端按设计要求相连或接地,a、b、c、d、e、f、g则与七段数码显示器对应端相连。

具体电路图见总图部分。

(4)校时电路

电路的工作原理:在此电路中,用到的元器件就只有两个双刀双掷开关,非常简单。

在此开关中起作用的可以是123脚或者456脚。

而在此次设计中我们使用123管脚。

管脚1接从晶振出来的1H标准脉冲,管脚2接正常的进位脉冲,两管脚3分别接时个位的脉冲和分个位的脉冲。

当正常工作开关打到2,进行正常的计数,打到1时进行调时。

(5)电源配位器电路

此电路可以通过变压器将220V的电压转换为5V的电压,可接一适配器插座直接接220V电源给数字钟供电。

三、仿真分析

1. 1HZ脉冲产生电路仿真

振荡器可由晶振组成,也可以由555与RC组成的多谐振荡器。

由555定时器得到1Hz的脉冲,功能主要是产生标准秒脉冲信号和提供功能扩展电路所需要的信号。

仿真分析开始前可双击仪器图标打开仪器面板。

准备观察被测试波形。

按下程序窗口右上角的启动/停止开关状态为1,仿真分析开始。

若再次按下,启动/停止升关状态为0,仿真分析停止。

电路启动后,需要调整示波器的时基和通道控制,使波形显示正常。

为了便于观察特把频率加大。

由图可见,所设计的电路可以产生方波。

2. 脉冲输出电压观察

在仪表栏里选用万用表接到555定时电路的输出端,设置万用表输出为直流电压。

点击运行按钮,由仿真结果可知脉冲输出电压较稳定,开始小幅度变化,最后稳定在3.33v 。

与最初设计基本相符。

3. 60进制计数器计数仿真结果

如图连接好电路,点击运行按钮,经过观察电路仿真结果所设计的电路是正确的,可以正常工作。

计数显示从0到59。

当计数器数到59后有一个短暂的60显示,这是异步清零的原因。

实际工作后不会出现计数不准的现象。

图7(a). 产生1kHz 的脉冲波形 图7(b). 产生1Hz 的脉冲波形

图8. 脉冲数出电压电路

4. 24进制计数器计数仿真结果

给电路加脉冲信号源,频率可以加大。

如图,频率为1kHz ,经过观察电路的仿真结果可以看到显示数字是从0到23与设计相符。

特别注意74LS160的连接。

5. 总体电路仿真结果

1). 秒计数向分计数进位仿真。

如图连接好电路,点击运行后,可以看到秒计数计到59后可以向分计数器进位,电路运行正常。

图9. 60进制计数器计数仿真电路

图10. 24进制计数器计数仿真电路

2). 分计数向时计数进位仿真。

给分计数器的个位计数片上加1kHz的时钟信号源,经过运行仿真后,可以看出分位计数到59时可以向时位进位。

电路运行正常。

6. 开关校时电路仿真结果

校时电路由开关、或非门和反相器构成,当A、B、E闭合,C、D断开时,电路正常计时;当A、B随意,C、D闭合时,时,分自动校时;当手动校时时,每开关一次示数增加1。

E开关用来较秒的,闭合时正常工作,断开时秒显示器为零,整个电路不工作。

可以起到较秒的作用。

经过仿真实验开关设置合理,可以起到预定的效果,能够有效地校准时、分、秒。

四、总体电路图,PCB图设计

将各模块的电路结合起来,得到数字钟的总体电路原理图如下:

原理图画好后,再将其转化成PCB图。

在制作PCB的过程时,我采取的方法是先用Altium Designer自动布线,之后再进行手动布线。

Altium Designer自动布线重合的很多,这花了不少时间,试了很多次效果都不理想,最后还是用手动布线进行布线。

虽然比较麻烦,但可以区分线路,有目的进行调整,最后还要用二十多根飞线才使得pcb 图得以布通。

PCB图如下图。