课后习题答案 第3章 门电路

数字电路第三章答案

第三章习题答案参考3-1.解:(a)由于74148是优先编码器当6I =0时,由表3-5可知道,当6I =0且7I=1时,编码器会对优先级别高的编码,所以输出就是6I 对应的输出。

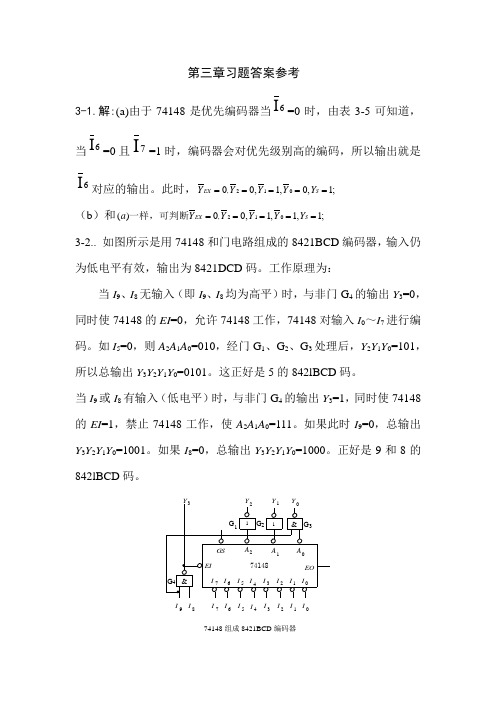

此时,,21000,1,0,1;EXS YY Y Y Y =====(b )和,210()00,1,1,1;EX S a Y Y Y Y Y =====一样,可判断3-2.. 如图所示是用74148和门电路组成的8421BCD 编码器,输入仍为低电平有效,输出为8421DCD 码。

工作原理为:当I 9、I 8无输入(即I 9、I 8均为高平)时,与非门G 4的输出Y 3=0,同时使74148的EI =0,允许74148工作,74148对输入I 0~I 7进行编码。

如I 5=0,则A 2A 1A 0=010,经门G 1、G 2、G 3处理后,Y 2Y 1Y 0=101,所以总输出Y 3Y 2Y 1Y 0=0101。

这正好是5的842lBCD 码。

当I 9或I 8有输入(低电平)时,与非门G 4的输出Y 3=1,同时使74148的EI =1,禁止74148工作,使A 2A 1A 0=111。

如果此时I 9=0,总输出Y 3Y 2Y 1Y 0=1001。

如果I 8=0,总输出Y 3Y 2Y 1Y 0=1000。

正好是9和8的842lBCD 码。

I I 457I 162I I I 03I I I 98I74148组成8421BCD 编码器3-3由于74147时优先编码器,优先级别为从9到1依次降低,而且是低电平有效,对照引脚图与真值表所以有(1)引脚为1.3.5时,看引脚5,即是8I,输出为:0111(2)引脚为2.4.10时,看引脚10,即是9I,输出为:0110(3)引脚为3.5.11时,看引脚5,即是8I,输出为:0111(4)引脚为4.10.12时,看引脚10,即是9I,输出为:0110(5) 引脚为5.10.13时,看引脚10,即是9I,输出为:0110(6) 引脚为10.11.13时,看引脚10,即是9I,输出为:01103-4(1)解:F1(A,B,C)=AB+C=1m+m3+m5+m6+m7=71m mmmm365实现的电路图如下:(2)解:F2(A,B,C)=m1+m2+m4+m5+m6=m6m1m5m2m4实现的电路图如下:(3)解:F 3(A,B,C )=∑)(5,3,1m =531m m m 实现的电路图如下:(4)解:F 4(A,B,C )=∑),(6,2,10m =6210m m m m 实现的电路图如下:(5)解:F 5(A,B,C )=∑),(6,5,30m =6530m m m m 实现的电路图如下:(6)解:F 6(A,B,C )=∑),(7,5,21m =7521m m m m 实现的电路图如下:(7)解:F7(A,B,C)=∑)m=72(7,6,3,mm2m3m6实现的电路图如下:(8)解:F8(A,B,C)=∑)m=7(7,4,1mm41m实现的电路图如下:3-5(1)解:F1(A,B,C,D)= ∑)9107811132m14,35,612,,,(14,,,,,,,=14mmmmmmmmmmmmm61091112131m823475实现的电路图如下:(2)解:F2(A,B,C,D)= )11102145m,(15,,,,=15mmmmm10142m115实现的电路图如下:=12mmmmmmm7896452m实现的电路图如下:(4)解:F4(A,B,C,D)= ∑)1011,61m4(14,,,,,,12=14mmmmmmm611120m1041实现的电路图如下:=15mmmmmmm911813472m实现的电路图如下:(6)解:F6(A,B,C,D)= ∑)4,27m9,,,,(11 =11mmmmm290m74实现的电路图如下:3-6 解:利用真值表,可以将Y 换成Y ,易得如下的表达式:A A A A Y123=A A A A Y 01231=A A A Y122=A A A Y 0123=A A A Y 0124= A A A Y125=A A A Y126=A A A Y 0127=A A Y38=A A Y 039=3-7解:根据题3-6的结果,F 1(A,B,C,D)= YY Y 52=A A A A A A A A A A 0120120123=A 3同理可得:F 2(A,B,C,D)= Y Y Y 641=A 3 F3(A,B,C,D)= Y Y Y 973=A A 03波形图如下:3-8解:波形如图所示:3-9解:图中的C in接地,为0,得全加器的函数式: S=B ABA+C o u t=AB+(A+B) C in得:1ACD BCDF=+2()() AB AB CD DF=++ 3-10设计如图所示:3-12解:(1)在八选一选择器74151中令A2=A ,A1=B ,A0=C 将F 1 (A,B)加多一个C ,换成F 1 (A,B,C)得F 1(A,B)= F1(A,B,C)=∑),,(543,2m 得D2=D3=D4=D5= 1 D0=D1= D6=D7=0(2)在八选一选择器74151中令A2=A ,A1=B ,A0=CF2(A,B,C)=∑),,(421,0m 得D0=D1=D2=D4=1 D3=D5=D6=D7=0(3)在八选一选择器74151中令A2=A ,A1=B ,A0=CF3(A,B,C)=∑),,(7,6,5,421m 得D1=D2=D4= D5=D6=D7=1 D0=D3= 0(4)在八选一选择器74151中令A2=A ,A1=B ,A0=CF4(A,B,C)=∑),,(6,5,4,321,0m 得D0=D1=D2=D3=D4=D5=D6=1 D7=0(5)在八选一选择器74151中令A2=A ,A1=B ,A0=C F4(A,B,C,D)=∑),,(13,12,1198,3m得D4= D6=1 D1= D5=D D0= D2= D3=D7=0(6)在八选一选择器74151中令A2=A ,A1=B ,A0=CF6(A,B,C)=∑),(6,5,30m 得D0= D3= D5=D6=1 D1=D2= D4=D7=0(7)在八选一选择器74151中令A2=A ,A1=B ,A0=CF7(A,B,C)=∑),(7,6,31m 得D1= D3= D6= D7=1 D0 =D2= D4= D5= 0(8)在八选一选择器74151中令A2=A ,A1=B ,A0=CF8(A,B,C,D)=∑),,(13,1110,54,3m得D2= D5=1 D1= D6 =DD0= D3= D4=D7=03-13解:设计如图所示:14解:输出的逻辑图如下:得逻辑表达式:Y=DBAA++CDBBA15解:如图所示:。

数电题第3章练习题答案

1.CMOS电路的两个主要优点是和。

(低功耗,抗干扰能力强)2.代表门电路抗干扰能力的参数是。

(噪声容限)3.三态门输出的三种状态分别为:、和。

(0)(1)(高阻)4.在CMOS门电路的输入端与电源之间接一个1K W电阻,相当于在该输入端输入电平。

(高)5.能够实现“线与”的TTL门电路叫,能够实现“线与”的CMOS门电路叫。

(OC门)(OD门)6.在CMOS门电路的输入端与电源之间接一个1K W电阻,相当于在该输入端输入电平。

(高)三极管通常工作在和状态。

(饱7.在逻辑电路中,在逻辑电路中,三极管通常工作在和)(截止)8.使用TTL与非门时下列做法中错误的是()。

(C)A、不用的输入端空着或剪去;B、将各输入端并联作非门用;C、将几个门的输出端并联作线与9.下列几种TTL电路中,输出端可实现线与功能的电路是()。

(D)A、或非门B、与非门C、异或门D、OC门10.对CMOS与非门电路,其多余输入端正确的处理方法是()。

(D)A、通过大电阻接地(>1.5KΩ);B、悬空;C、通过小电阻接地(<1KΩ);D、通过电阻接VCC 11.使用TTL与非门时下列做法中错误的是(与非门时下列做法中错误的是( )。

(C)A、不用的输入端空着或剪去;B、将各输入端并联作非门用;C、将几个门的输出端并联作线与12.对CMOS与非门电路,其多余输入端正确的处理方法是()。

(D)A、通过大电阻接地(>1.5KΩ);B、悬空;C、通过小电阻接地(<1KΩ);D、通过电阻接V DD13.使用TTL与非门时下列做法中错误的是(与非门时下列做法中错误的是( )。

(C)A、不用的输入端空着或剪去;B、将各输入端并联作非门用;C、将几个门的输出端并联作线与。

第3章-门电路-课后答案

第3章-门电路-课后答案- 2 -第三章 门 电 路【题3.1】 在图3.2.5所示的正逻辑与门和图3.2.6所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明Y 和A,B 之间是什么逻辑关系。

图3.2.5的负逻辑真值表图3.2.6的负逻辑真值表【题3.5】已知CMOS 门电路的电源电压5DDVV=,静态电源电流2DDIAμ=,输入信号为200ZKH 的方波(上升时间和下降时间可忽略不计),负载电容200LC pF=,功耗电容20pdCpF=,试计算它的静态功耗、- 3 -动态功耗、总功耗和电源平均电流。

【解】 静态功耗 621050.01S DD DD P I V mW mW-==⨯⨯=动态功耗()()2125220020102105 1.10D L pd DD P C C fV mW mW -=+=+⨯⨯⨯⨯=总功耗0.01 1.10 1.11TOT S D P P P mW=+=+= 电源平均电流1.110.225TOT DD DDP I mA mA V ===【题3.5】已知CMOS 门电路工作在5V 电源电压下的静态电源电流5A μ,在负载电容100LC pF 为,输入信号频率为500ZKH 的方波时的总功耗为1.56mW 试计算该门电路的功耗电容的数值。

【解】首先计算动态功耗()31.565510 1.54D TOT STOT DD DDP P P P I V mW mW-=-=-=-⨯⨯≈ 根据()2DLpd DDP CC fV =+得3122521.541010010135105Dpd L DDP C C F pF fV --⎛⎫⨯=-=-⨯≈ ⎪⨯⨯⎝⎭【题3.7】试分析图P3.7 中各电路的逻辑功能,写出输出逻辑函数式。

AB CDDYV DDY(b)A- 4 -- 5 -A BDC INHV DDY图P3.7【解】 (a )Y A B C =++ (b )Y A B C =•• (c )Y AB CD INH =+•【题3.11】 在图P3.11的三极管开关电路中,若输入信号Iv 的高、低电平分别为50IH IL V V V V==、,试计算在图中标注的参数下能否保证IIHvV =时三极管饱和导通、IILvV =时三极管可靠地截止?三极管的饱和导- 6 -通压降()0.1CE sat VV=,饱和导通内阻()20CE sat R=Ω。

数电 第3章习题及解答

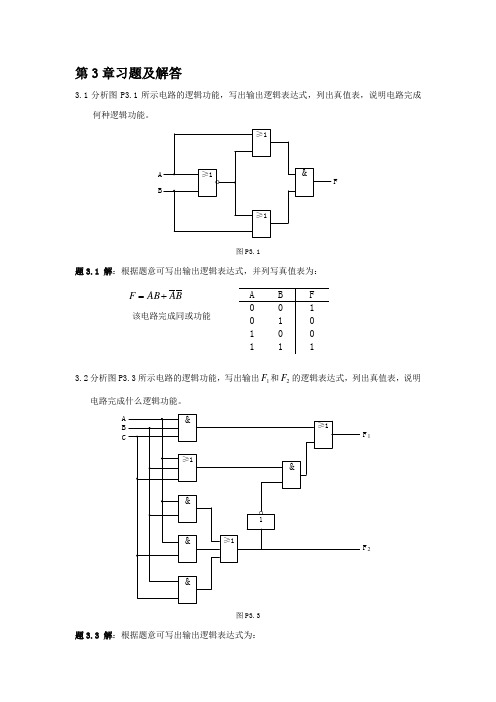

第3章习题及解答3.1分析图P3.1所示电路的逻辑功能,写出输出逻辑表达式,列出真值表,说明电路完成何种逻辑功能。

F图P3.1题3.1 解:根据题意可写出输出逻辑表达式,并列写真值表为:B A AB F +=该电路完成同或功能3.2 分析图P3.3所示电路的逻辑功能,写出输出1F 和2F 的逻辑表达式,列出真值表,说明电路完成什么逻辑功能。

A B CF F 12图P3.3题3.3 解:根据题意可写出输出逻辑表达式为:AC BC AB F C B A F ++=⊕⊕=21列写真值表为:该电路构成了一个全加器。

3.5 写出图P3.5所示电路的逻辑函数表达式,其中以S 3、S 2、S 1、S 0作为控制信号,A ,B作为数据输入,列表说明输出Y 在S 3~S 0作用下与A 、B 的关系。

图P3.5题3.5 解:由逻辑图可写出Y 的逻辑表达式为: A B S B S B A S AB S Y ++⊕+=0123图中的S 3、S 2、S 1、S 0作为控制信号,用以选通待传送数据A 、B ,两类信号作用不同,分析中应区别开来,否则得不出正确结果。

由于S 3、S 2、S 1、S 0共有16种取值组合,因此输出Y 和A 、B 之间应有16种函数关系。

列表如下:3.7 设计一个含三台设备工作的故障显示器。

要求如下:三台设备都正常工作时,绿灯亮;仅一台设备发生故障时,黄灯亮;两台或两台以上设备同时发生故障时,红灯亮。

题3.7 解:设三台设备为A 、B 、C ,正常工作时为1,出现故障时为0; F 1为绿灯、F 2为黄灯、F 3为红灯,灯亮为1,灯灭为0。

根据题意可列写真值表为:求得F 1、F 2、F 3的逻辑表达式分别为: C A C B B A F C AB C B A BC A F ABC F ++=++==321;;根据逻辑表达式可画出电路图(图略)。

3.9 设计一个组合逻辑电路,该电路有三个输入信号ABC ,三个输出信号XYZ,输入和输出信号均代表一个三位的二进制数。

第3章习题答案

思考题:题3.1.1 组合逻辑电路在结构上不存在输出到输入的 ,因此 状态不影响 状态。

答:反馈回路、输出、输入。

题3.1.2 组合逻辑电路分析是根据给定的逻辑电路图,而确定 。

组合逻辑电路设计是根据给定组合电路的文字描述,设计最简单或者最合理的 。

答:逻辑功能、逻辑电路。

题3.2.1 一组合电路输入信号的变化顺序有以下三种情况,当 时,将可能出现竞争冒险。

(A )00→01→11→10 (B )00→01→10→11 (C )00→10→11→01 答:B题3.2.2 清除竞争冒险的常用方法有(1)电路输出端加 ;(2)输入加 ;(3)增加 。

答:电容,选通脉冲,冗余项。

题3.2.3 门电路的延时时间是产生组合逻辑电路竞争与冒险的唯一原因。

( ) 答:×题3.2.4 根据毛刺产生的方向,组合逻辑的冒险可分为 冒险和 冒险。

答:1型、0型。

题3.2.5 传统的判别方法可采用 和 法来判断组合电路是否存在冒险。

答:代数法、卡诺图。

题3.3.1 进程行为之间执行顺序为 ,进程行为内部执行顺序为 。

答:同时、依次。

题3.3.2 行为描述的基本单元是 ,结构描述的基本单元是 。

答:进程、调用元件语句。

题3.3.3 结构体中的每条VHDL 语句的执行顺序与排列顺序 。

答:无关题3.4.1串行加法器进位信号采用 传递,而并行加法器的进位信号采用 传递。

(A )超前,逐位 (B )逐位,超前 (C )逐位,逐位 (D )超前,超前 答:B题3.4.2 一个有使能端的译码器作数据分配器时,将数据输入端信号连接在 。

答:使能端题 3.4.3 优先编码器输入为70I I -(0I 优先级别最高),输出为2F 、1F 、0F (2F 为高位)。

当使能输入00,651====I I I S 时,输出012F F F 应为 。

答:110题3.4.4 用4位二进制比较器7485实现20位二进制数并行比较,需要 片。

数电第五版(阎石)第三章课后习题及答案

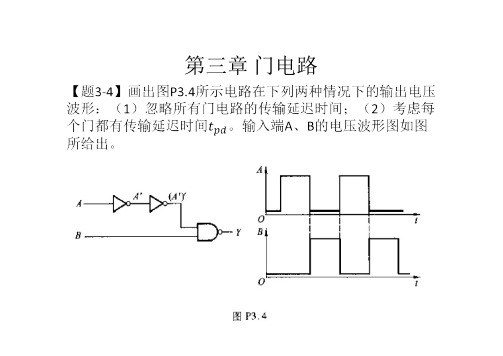

第三章门电路解:两种情况下的电压波形图如图A3.4所示。

【题3.7】试分析图3.7中各电路图的逻辑功能,写出输出的逻辑函数式。

(a )图P3.7(a )电路可划分为四个反相器电路和一个三输入端的与非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式,'111'1'1'1)(,,,C B A D C C B B A A ''''111')(C B A C B A C B A D Y(b )图P3.7(b )电路可划分为五个反相器电路和一个或非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:'111''''()()YA B C A B C ABC(c )图P3.7(c )电路可划分为三个与非门电路、两个反相器电路和一个或非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:''')(,)(,)'(,)(G INHH EF G CD F AB E '''''()()'()'()()Y I H AB CD INH AB CD INH(d)图P3.7(d)电路可划分为两个反相器电路和两个传输门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:'YBAAB'【题3.8】试画出图3-8(a)(b)两个电路的输出电压波形,输入电压波形如图(c)所示。

输出电压波形如右图所示:【题3.9】 在图3-21所示电路中,G 1和G 2是两个OD 输出结构的与非门74HC03,74HC03输出端MOS 管截止电流为 导通时允许的最大负载电流为这时对应的输出电压V OL (max )=0.33V 。

负载门G 3-G 5是3输入端或非门74HC27,每个输入端的高电平输入电流最大值为 ,低电平输入电流最大值为 ,试求在 、、、、并且满足 ,的情况下, 的取值的允许范围。

课后习题答案_第3章_门电路

数字电子技术基础第三章习题答案3-1 如图3-63a~d所示4个TTL门电路,A、B端输入的波形如图e所示,试分别画出F1、F2、F3和F4的波形图。

略3-2 电路如图3-64a所示,输入A、B的电压波形如图3-64b所示,试画出各个门电路输出端的电压波形。

略3-3 在图3-7所示的正逻辑与门和图3-8所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F和A、B之间是什么逻辑关系。

答:(1)图3-7负逻辑真值表F与A、B之间相当于正逻辑的“或”操作。

(2)图3-8负逻辑真值表F与A、B之间相当于正逻辑的“与”操作。

3-4 试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,各输入端应如何连接?答:三种门经过处理以后均可以实现反相器功能。

(1)与非门: 将多余输入端接至高电平或与另一端并联;(2)或非门:将多余输入端接至低电平或与另一端并联;(3) 异或门:将另一个输入端接高电平。

3-5 为了实现图3-65所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

答:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b)多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

3-6 如要实现图3-66所示各TTL 门电路输出端所示的逻辑关系,请分析电路输入端的连接是否正确?若不正确,请予以改正。

答:a )不正确。

输入电阻过小,相当于接低电平,因此将Ω50提高到至少2K Ω。

b) 不正确。

第三脚V CC 应该接低电平。

c )不正确。

万用表一般内阻大于2K Ω,从而使输出结果0。

因此多余输入端应接低电平,万用表只能测量A 或B 的输入电压。

3-7 (修改原题,图中横向电阻改为6k Ω,纵向电阻改为3.5 k Ω,β=30改为β=80) 为了提高TTL 与非门的带负载能力,可在其输出端接一个NPN 晶体管,组成如图3-67所示的开关电路。

第3章 CMOS gates解析

• 1.Logic level for CMOS Logic circuits • 2.CMOS inverter

Logic level for CMOS Logic circuits

5.0v 3.5v 1.5v 0v

Logic 1(high)

Undefined state

Logic 0(Low)

• 5.线‘与’逻辑(Wiring “AND” Logic)

1.EX-OR gate

(1).电路结构

T10 T4 T3 T1 T2 T6 T5

T9

p

T8

F=AB’+A’B

T7

=1

(2).异或门的性质及可编程性

• 电路符号

D A =1 En B F B En A D F

UDD

3.5v

+5v

-

-

0

1.5v

开

门

关

门

Vin (UGS)

CMOS inverter

Vout

VDD=+5v 5.0v

3.5V 1.5V

0.0v

Vin

Q2 p-Channel

Vout N-Channel Q1

+5v

3.5v

Vin

Q1

Q2 on off

Vout 5.0v 0.0

0.0V off 5.0v on

MOSFET的结构和原理

N沟道增强型MOS管结构示意图及增强型MOS的符号

返回

图1.4.8

uDS =0时uGS对导电沟道的影响

uGS为大于UGS(th)的某一值时uDS对iD的影响

返回

N沟道增强型MOS管的特性曲线

返回

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电子技术基础第三章习题答案

3-1如图3-63a~d所示4个TTL门电路,A、B端输入的波形如图e所示,试分别画出F1、F2、F3和F4的波形图。

略

3-2电路如图3-64a所示,输入A、B的电压波形如图3-64b所示,试画出各个门电路输出端的电压波形。

略

3-3

答:

F与

(2)图

A B F

000

010

100

111

F与A、B之间相当于正逻辑的“与”操作。

3-4试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,各输入端应如何连接?

答:三种门经过处理以后均可以实现反相器功能。

(1)与非门:将多余输入端接至高电平或与另一端并联;(2)或非门:将多余输入端接至低电平或与另一端并联;(3)异或门:将另一个输入端接高电平。

3-5为了实现图3-65所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

答:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;

b)多余输入端接低电平或与另两个输入端的一端相连;

c)未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;

d )未用或门的两个输入端悬空或都接高电平。

3-6如要实现图3-66所示各TTL 门电路输出端所示的逻辑关系,请分析电路输入端的连接是否正确?若不正确,请予以改正。

答:a )不正确。

输入电阻过小,相当于接低电平,因此将Ω50提高到至少2K Ω。

b)不正确。

第三脚V CC 应该接低电平。

c )不正确。

万用表一般内阻大于2K Ω,从而使输出结果0。

因此多余输入端应接低电平,万用表只能测量A 或B 的输入电压。

3-7(修改原题,图中横向电阻改为6k Ω,纵向电阻改为3.5k Ω,β=30改为β=80)为了提高TTL 与非门的带负载能力,可在其输出端接一个NPN 晶体管,组成如图3-67所示的开关电路。

当与非门输出高电平V OH =3.6V 时,晶体管能为负载提供的最大电流是多少?

答:如果输出高电平,则其输出电流为(3.6-0.7)/6=483u A ,而与非门输出高电平时最大负载电流是400u A ,因此最大电流L I (4000.7/3.5)8016mA =−×=。

3-8如图3-68所示TTL 与非门,其多发射晶体管的基极电阻R 1=2.8kΩ,若在A 输入端分别为5V 、3.6V 、0.6V 、0.3V 、0V 的电压,试分析计算接到B 输入端的电压表的读数是多少?输出电压v O 是多少?

答:(1)当输入5V 时,表的电压读数为1.4V,v O =0V;

(2)当输入3.6V 时,表的电压读数为1.4V,v O =0V;

(3)当输入0.6V 时,表的电压读数为0.6V,v O =3.6V;

(4)当输入0.3V 时,表的电压读数为0.3V,v O =3.6V;

(5)当输入0V 时,表的电压读数为0V,v O =3.6V;

3-9用双线示波器观测到某TTL 与非门的输入信号v 1和输出信号v 0的波形如图3-69所示,试求此与非门的传输延迟时间t PHL 、t PLH 和平均传输延迟时间t PD 。

答:t PHL =7ns ,t PLH =10ns ,t PD =8.5ns

3-10为什么说TTL 与非门的输入端悬空相当于接高电平?多余的输入端应如何处理?

答:由于TTL 与非门输入端负载特性决定,当输入端悬空时,输出将为低电平,因此相当于接入高电平。

因此多余的输入端悬空,或接高电平。

3-11有TTL 与非门、或非门和三态门组成的电路如图3-70a 所示,图b 是各输入端的输入波形,试画出F 1和F 2的波形图。

答:(1)当E 为高电平时,缓冲器(三态门)输出为高阻,对应与非门与或非门的输入相当于悬空,而TTL 门悬空相当于输入高电平,因此12F B,F 0==。

(2)当E 为低电平时,缓冲器(三态门)输入同输入,输出为0,因此12F 1,F A ==。

3-12(修改原题,a )图中的PNP 管改为NPN 管)试分析图3-71所示3个逻辑电路的逻辑功能,列出其值表,写出其逻辑函数表达式,指出它们能完成的逻辑功能。

答:(a)图真值表

b”运算,然后进行

(c

A B F

000

011

101

110

因此,B A B A F +=,电路实现“异或”运算功能。

3-13图3-72所示逻辑电路中,G 1、G 2、G 3是OC 门。

负载电阻R L =2kΩ,其输出低电平的输出特性如图b 所示。

负载门是CT74H 系列的与非门,其多发射极晶体管的基极电阻R1=2.8kΩ,输入高电平漏电流I IH =40μA ,OC 门输出高电平

的漏电流I OH =2μA ,V OHmin =3V ,V OLmax =0.4V 。

试求此“线与”输出能带二输入TTL

与非门多少个?

答:OC 门输出短接时可以实现“线与”功能,分析图中所示电路驱动双输

(1)CC V n =(2)L

OL I CC OL max OLMAX L IL V V 50.4I 16R 2n 9I 1.5

−−−

−==≈综合以上情况,图中“线与”输出最多能带9个二输入TTL 与非门。

3-14图3-73所示3个CMOS 门电路,为实现图中各输出端所示逻辑函数表达式的逻辑关系,多余输入端C 应如何处理?

答:a)C端接低电平或与其他端并连使用。

b)C端接高电平或与其他端并连使用。

c)C端接高电平或与其他端并连使用。

3-15如图3-74所示逻辑电路,图中G1是TTL三态输出与非门,G2是74系列TTL与非门,电压表的量程为5V,内阻为100kΩ。

试问,在下列四种情况下电压表的读数以及G2的输出电压v0各为多少?

(1)v A=0.3V,开关S打开;(2)v A=0.3V,开关S闭合;

(3)v A=3.6V,开关S打开;(4)v A=3.6V,开关S闭合。

答:(1)电压表没有读数,v O=0.3V。

(2)电压表读数1.4V,v O=0.3V。

(3)电压表读数0.3V,v O=0.3V。

(4)电压表读数0.3V,v O=3.6V。

3-16由TTL三态门和OC门组成的逻辑电路如图3-75所示,试用内阻为20 kΩ/V的万用表测量图中A、B、C共3点的电压,读数各为多少?

答:A点电压:0.3V,B点电压:0.1V,C点电压:10V。

3-17当电源电压V DD改变时,CMOS反相器的电压传输特性为什么会像图3-47所示那样变化,试分析说明其原理。

答:由于CMOS器件工作时NMOS和PMOS交替工作,输出不同电平时,总有一种MOS管截止,从而使得输出电平接近于电源电压。

以CMOS反相器为例,当输出高电平时,NMOS管截止,PMOS管没有压降,其输出高电平就为电源供电电压,因此传输特性曲线随电源电压改变。

从图中也可看出CMOS器件工作电压的范围要比TTL宽。

3-18在CMOS传输门TG的输出端接电阻R L=1kΩ,如图3-76所示,设TG的导通电阻为R TG,截止电阻大于109Ω,求:

(1)当C=1时,v 0与v 1的关系;

(2)C=0时,输出v 0的状态如何?

答:(1)L

TG L i o R R R v v +=(2)v 0为高阻态。

3-19将CMOS 门电路的输入悬空,其输出状态如何?请说明其原理。

答:输入端悬空,会受到感应信号干扰而误认为是有效输入信号,易出现错

3-20在析图a 答:3-21TTL 会被抬高降低作。

3-22能够将两个CMOS 与非门或者或非门的输出端直接并联连接使用,请说明其原因。

答:不能。

只有OC 门、OD 门或者三态门的输出能够直接并联,其他门电路输出端不能直接连接,否则会提升输出低电平的电压值,也容易烧毁器件。

3-23试比较TTL 电路和CMOS 门电路的优缺点。

答:

1)TTL电路是电流控制器件,而CMOS电路是电压控制器件。

2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

CMOS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。

CMOS电路本身的功耗与输入信号的脉冲频率有关,频率越高,功耗越高,芯片越热。

3)CMOS电路的锁定效应:CMOS电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。

这种效应就是锁定效应。

当产生锁定效应时,CMOS的内部电流能达到40mA以上,很容易烧毁芯片。

3-24试说明在使用CMOS门电路时不宜将输入端悬空的理由。

答:CMOS电路的输入阻抗非常高,很容易受到干扰,并且CMOS电路为场效应管,输入电压控制输出电流,悬空时容易出现静电等瞬时高压烧毁器件的现象,所以必须不用的输入端不能悬空,就根据器件功能进行相应的处理。

3-25在做CMOS门电路的实验时发现,输入脉冲信号的频率越高,器件的温升越高,这种现象是否正常?试说明理由。

答:CMOS器件的总功耗包括静态功耗和动态功耗,当工作频率较高时,动态功耗远大于静态功耗,此时的静态功耗几乎可以忽略不计。

当输入脉冲信号的频率越高,动态功耗越大,器件的温升越高,这种现象是正常的。