第八章 输入输出接口8255A(8.1-8.3)

合集下载

第8章(8255)

A口/B口可分别定义为输入或输出

支持查询、中断方式传送数据 C口部分位作为控制信号和状态信号

C口其余位可独立置位/复位

方式1输出(A口)

方式1输出(B口) PB7~PB0 8位

方式1输出

PA7~PA0 8位

INTEA

PC7 PC6

OBFA ACKA

INTEB

PC1 PC2

OBFB ACKB

A1

0 0 1 0 0 1

A0

端口及操作功能

0 0 0 1 1 1 1 × 0 1 1 1 0 0 0 0 × 1 0 0 0 0 0 0 0 1 0 端口A数据总线 端口B数据总线 端口C数据总线 数据总线端口A 数据总线端口B 数据总线端口C 数据总线控制寄存器 未选中8255A,数据总线三态 非法状态 断开功能 输出操作(写) 输入操作(读)

A组

A组 C口高位 (4位) B组 C口低位 (4位) B组 C口 (8位) PC7~PC4

读/写控 制逻辑

端口C

PC3~PC0

B组

PB7~PB0

B组控制 内部总线

端口B

8255A内部结构框图

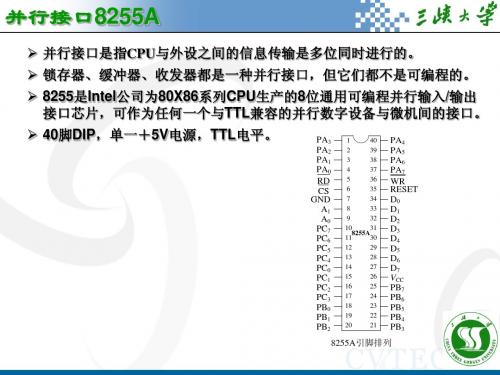

三个端口:8位,A口(端口A)、B口(端口B)、C口(端口C)

二组:A组(A口+C口高位)、B组(B口+C口低位)

工作方式2(双向输入输出)

只适用于A口,占用5条联络线 B口可工作于方式0、方式1 C口的PC2~0 可作为B口方式1的联络线 或独立使用 控制信号定义与前述相同 不同 ACK有效时,输出端口才打开,无效时呈高阻态 输入、输出均可锁存

WR

RD

& & ≥1

PC3

8

INTRA

可编程的输入输出芯片8255APPT教学课件

8.1 可编程的输入输出接口芯片8255A 8.1.4 8255A的工作方式 8.2 8255A 复习:P295~300 预习:D/A、A/D;

P318~326 作业:7-23;7-25 思考题:7-26 第11、12周的实验时间进行实验上机考试

2020/12/11

1

3. 方式2

(1)方式2的基本功能 这是一种双向工作方式,使外设在单一的

e.STB 外设给8255A的选通信号,低电平 有效,此信号将外设送到8255A的数据打入输 入锁存器。

2020/12/11

5

f.IBF 输入锁存器满信号,这是8255A 送给CPU的状态信号,高电平有效,表示当 前已有一个新数据送到输入锁存器,等待 CPU取走。

g.INTE2 中断允许信号,当PC4设置为1, 则INTE2=1,表示端口A的输入处于中断允 许状态。

2020/12/11

6

(3)方式2的控制字

当端口A工作在方式2时,端口B可工作 在方式0,亦可工作在方式1,既可作输入 口也可作输出口。而端口C剩下3位视B口 而定,若B口工作在方式0,C口剩下3位可 工作在方式0,若B口工作在方式1,则C口 剩下3位作B口的联络线。

2020/12/11

7

例1: 设A端口工作于方式2,B端口工作 于方式0输出,PC2~PC0工作在方式0输入。 则控制字为:

主程序段:

SUB AX,AX

MOV DS,AX

MOV AX,1000H

MOV WORD PTR[003CH],AX ;设置偏址

MOV AX,5000H

MOV WORD PTR[003EH],AX ;设置段址

MOV AL,0A0H

;置方式控制字

OUT 0F7H,AL

P318~326 作业:7-23;7-25 思考题:7-26 第11、12周的实验时间进行实验上机考试

2020/12/11

1

3. 方式2

(1)方式2的基本功能 这是一种双向工作方式,使外设在单一的

e.STB 外设给8255A的选通信号,低电平 有效,此信号将外设送到8255A的数据打入输 入锁存器。

2020/12/11

5

f.IBF 输入锁存器满信号,这是8255A 送给CPU的状态信号,高电平有效,表示当 前已有一个新数据送到输入锁存器,等待 CPU取走。

g.INTE2 中断允许信号,当PC4设置为1, 则INTE2=1,表示端口A的输入处于中断允 许状态。

2020/12/11

6

(3)方式2的控制字

当端口A工作在方式2时,端口B可工作 在方式0,亦可工作在方式1,既可作输入 口也可作输出口。而端口C剩下3位视B口 而定,若B口工作在方式0,C口剩下3位可 工作在方式0,若B口工作在方式1,则C口 剩下3位作B口的联络线。

2020/12/11

7

例1: 设A端口工作于方式2,B端口工作 于方式0输出,PC2~PC0工作在方式0输入。 则控制字为:

主程序段:

SUB AX,AX

MOV DS,AX

MOV AX,1000H

MOV WORD PTR[003CH],AX ;设置偏址

MOV AX,5000H

MOV WORD PTR[003EH],AX ;设置段址

MOV AL,0A0H

;置方式控制字

OUT 0F7H,AL

第8章-8255

A1、A0端口选择

0 0 1 1 0----A端口 1----B端口 0----C端口 1----控制端口

6

8-2 可编程并行接口芯片8255 四、8255的控制字

1、方式选择控制字(D7位置1)

2、端口C按位置位/复位控制字(位操作) (D7置0)

控制寄存器:

D7 D6 D5 D4 D3 D2 D1 D0

14

INTEA A口

STBA :选通信号;其上升沿将输 入数据锁存到输入缓冲器 IBFA

PC5 PC4

PC3 INTEB

:输入缓冲器满信号,选 通信号将数据存入缓冲器 后IBFA=1,表示输入数据 有效。

•仅剩余PC6、PC7引脚作为I/O线

8-2 可编程并行接口芯片8255

方式1 ---选通输入/输出方式: •INTE----中断允许,用来决定A、 选通输入方式: B口是否允许中断:

X D3 D2 D1 D0

注意: 端口C按位置位/复位控制字与方 式选择控制字均写入控制字寄存 器,但它们的标志位不同。

9

8-2 可编程并行接口芯片8255

例、请编程:8255的 A、B、C和控制端口的地址分别为60H、 61H、62H和63H。当某开关闭合时,点亮相应的指示灯。

8255A PA7~PA0 +5V 第一步:首先初始化,确定工作方式

•INTRA ----中断请求 :当INTEA、 IBFA、 STBA均置1时INTRA=1, 通知CPU读取A口,CPU读取数 据后 INTRA=0。

15

8-2 可编程并行接口芯片8255

方式1 ---选通输入/输出方式:

选通输入方式:

PA7~PA0 IBFA STBA INTRA PB7~PB0 B口 PC1 PC2 PC0 IBFB STBB INTRB PC6、PC7

【微机原理】第8章输入输出接口II-8255

AB

DB

M/IO RD WR

CPU INTR

CS

DB

DB RDY

RD WR STB

INTR I/O接口芯片

DB

RDY

STB I/O设备

• 所谓“可编程”是指芯片的功能和一些参数是可由用户选 择和改变的。

• 通过向芯片内部写入特定的“工作方式控制字”,就可以 选择这个芯片的工作方式。

• 例如,可以将某芯片的数据端口设定为“输入”,也可以 将它设定为“输出”。

• 显然,芯片的可编程特性扩大了其使用范围,使用上也更 方便。

• 按照可编程接口芯片的用途,可以将其分为“通用接口芯 片”和“专用接口控制器”两类。

8.3.1 8255A芯片内部结构和引脚功能

1. 8255A的基本性能

• 8255A是具有多种功能的可编程并行接口电路芯片 • 其内部最基本的接口部件是: • 三态缓冲器、锁存器 • 此外,还包括与CPU的联络电路及与外设的联络电路: • 状态寄存器、控制寄存器 • 端口译码电路、控制电路(如读写控制、中断控制)

每位可独立进行输出控制(位控制)

使用最灵活,较难掌握

⑶ 数据总线缓冲器

这是一个三态双向8位缓冲器,它是8255A芯片 与系统数据总线的接口。

输入输出的数据,输出的指令以及CPU发出的控制 字和外设的状态信息,也都是通过这个缓冲器传送的

⑷ 读/写和控制逻辑

它与CPU的地址总线中的A1、A0以及有关的控 制信号(RD,WR,RESET,IO/M)相连,由它控制 把CPU的控制命令或输出数据送至相应的端口,也由 它控制把外设的状态信息或输入数据通过相应的端口, 送至CPU。

• 8255A有3个8位的数据端口(A/B/C), • 共24个I/O引脚, • 共有3种输入输出工作方式 • 基本输入/输出(A/B/C口) • 选通输入或选通输出(A/B口) • 双向选通(A口)

8255A接口技术PPT课件

2

本章 学习要求

1.掌握

并行接口的概念,可编程并行接口芯片的功能; 可编程并行接口芯片8255A的结构,其三种工作方式及特点; 8255A的使用; 8255A的端口地址分配,方式0的功能及端口命令字的设置。

2.理解

8255A各种工作方式的区别

3.了解

主机与外设间数据传送的基本控制方式(程序控制方式,中断 方式,DMA方式)

18

C口的作用与8255A的工作方式有关,它除了作数据口 以外,还有其他用途,故C口的使用比较特殊,单独介绍 如下:

a.作数据口。 b.作状态口。 c.作专用(固定)联络(握手)信号线。 d.作按位控制用。

(2)内部结构

8255A的内部结构如图所示。它由以下4个部分组成。

19

D0~D8

CS WR A1 A0 RD RESET

21

8255A引脚

PA4 PA5 PA6 PA8

WR RESET D0 D1 D2 D3 D4 D5 D6 D8 VCC PB8 PB6 PB5 PB4 PB3

RD:读信号,低电平有效。 WR:写信号,低电平有效。 RESET:复位信号,高电平

有效。它清除控制寄存器 并将8255A的A、B、C三 个端口均置为输入方式; 输入寄存器和状态寄存器 被复位,并且屏蔽中断请 求;24条面向外设信号线 呈现高阻悬浮状态。

0 ×× 1 1

总线悬浮

0 11 0 1

控制口不能读

63H

202H 203H

203H

22

二、8255A的编程命令 1.方式命令 作用:指定8255A的工作方式及其方式下3个并行端口(PA、

PB、PC)的功能,是作输入还是作输出。 格式:8位,其中最高位是特征位,一定要写1,其余各位定

本章 学习要求

1.掌握

并行接口的概念,可编程并行接口芯片的功能; 可编程并行接口芯片8255A的结构,其三种工作方式及特点; 8255A的使用; 8255A的端口地址分配,方式0的功能及端口命令字的设置。

2.理解

8255A各种工作方式的区别

3.了解

主机与外设间数据传送的基本控制方式(程序控制方式,中断 方式,DMA方式)

18

C口的作用与8255A的工作方式有关,它除了作数据口 以外,还有其他用途,故C口的使用比较特殊,单独介绍 如下:

a.作数据口。 b.作状态口。 c.作专用(固定)联络(握手)信号线。 d.作按位控制用。

(2)内部结构

8255A的内部结构如图所示。它由以下4个部分组成。

19

D0~D8

CS WR A1 A0 RD RESET

21

8255A引脚

PA4 PA5 PA6 PA8

WR RESET D0 D1 D2 D3 D4 D5 D6 D8 VCC PB8 PB6 PB5 PB4 PB3

RD:读信号,低电平有效。 WR:写信号,低电平有效。 RESET:复位信号,高电平

有效。它清除控制寄存器 并将8255A的A、B、C三 个端口均置为输入方式; 输入寄存器和状态寄存器 被复位,并且屏蔽中断请 求;24条面向外设信号线 呈现高阻悬浮状态。

0 ×× 1 1

总线悬浮

0 11 0 1

控制口不能读

63H

202H 203H

203H

22

二、8255A的编程命令 1.方式命令 作用:指定8255A的工作方式及其方式下3个并行端口(PA、

PB、PC)的功能,是作输入还是作输出。 格式:8位,其中最高位是特征位,一定要写1,其余各位定

汇编语言第8章输入输出接口

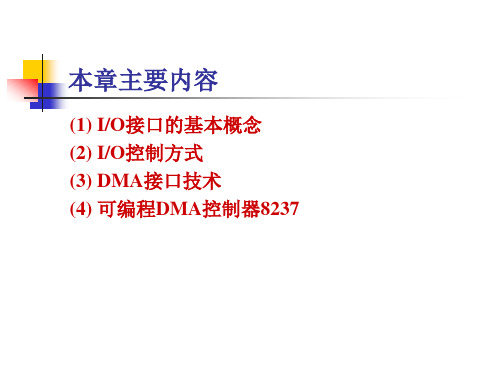

本章主要内容

(1) I/O接口的基本概念 (2) I/O控制方式 (3) DMA接口技术 (4) 可编程DMA控制器8237

8.1 I/O接口概述

8.1.1 I/O接口的基本功能

(1) 数据缓冲 (2) 提供联络信息 (3) 信号与信息格式的转换 (4) 设备选择 (5) 中断管理 (6) 可编程功能

IOW

图8.4 片选信号的产生

8.2 I/O控制方式

主机与外围设备之间的数据传送控制方式(即I/O控制 方式)主要有三种:

程序控制方式、中断控制方式和直接存储器存取 (DMA)方式。

8.2.1 程序控制方式

程序控制方式是指在程序控制下进行的数据传送方式。 它又分为无条件传送和程序查询传送两种。

地址空间 200~20FH 210~217H 218~2F7H 2F8~2FFH 300~31FH 320~32FH 330~377H 378~37FH

器件/接口适配器 地址空间

游戏卡

380~38FH

扩充部件

390~3AFH

未用

3B0~3BFH

异步通信卡(COM2) 3C0~3CFH

未用

3D0~3DFH

(5) DMA控制器发出存储器写信号MEMW,将数据传送 到由地址总线上的地址所指向的内存单元;

(6) DMA控制器放弃对总线的控制权;

(7) 地址寄存器加1;

(8) 字节计数寄存器减1;

(9) 如果字节计数寄存器的值不为零,则返回第一步,否 则结束。

第8章 作业

8.1 8.2 8.3 8.5 8.6 8.7 8.11

硬盘卡

3E0~3EFH

未用

3F0~3F7H

打印卡

3F8~3FFH

(1) I/O接口的基本概念 (2) I/O控制方式 (3) DMA接口技术 (4) 可编程DMA控制器8237

8.1 I/O接口概述

8.1.1 I/O接口的基本功能

(1) 数据缓冲 (2) 提供联络信息 (3) 信号与信息格式的转换 (4) 设备选择 (5) 中断管理 (6) 可编程功能

IOW

图8.4 片选信号的产生

8.2 I/O控制方式

主机与外围设备之间的数据传送控制方式(即I/O控制 方式)主要有三种:

程序控制方式、中断控制方式和直接存储器存取 (DMA)方式。

8.2.1 程序控制方式

程序控制方式是指在程序控制下进行的数据传送方式。 它又分为无条件传送和程序查询传送两种。

地址空间 200~20FH 210~217H 218~2F7H 2F8~2FFH 300~31FH 320~32FH 330~377H 378~37FH

器件/接口适配器 地址空间

游戏卡

380~38FH

扩充部件

390~3AFH

未用

3B0~3BFH

异步通信卡(COM2) 3C0~3CFH

未用

3D0~3DFH

(5) DMA控制器发出存储器写信号MEMW,将数据传送 到由地址总线上的地址所指向的内存单元;

(6) DMA控制器放弃对总线的控制权;

(7) 地址寄存器加1;

(8) 字节计数寄存器减1;

(9) 如果字节计数寄存器的值不为零,则返回第一步,否 则结束。

第8章 作业

8.1 8.2 8.3 8.5 8.6 8.7 8.11

硬盘卡

3E0~3EFH

未用

3F0~3F7H

打印卡

3F8~3FFH

第8章可编程输入输出接口2014(新简)

当A1A0=11时 选择控制端口

20

表8.1 8255A的读写操作控制

21

8.1.2 8255A的控制字及其工作方式

8255A 共有两个控制字:即工作方 式控制字和对C口臵位/复位控制字。 1. 控制字 (1)工作方式控制字: 控制字和各位的含义如图所示。

22

D7

D6 D 5

D4 D3

D2 D1 D0

下图示出 8255A 方式 1 选通输入时的内部 结构图。

35

•STB:选通信号。外设准备好数据发 送STB#,低电平有效。

•IBF:输入缓冲器满信号,STB#下降 沿8255向外设输出IBF信号,表示输入 缓冲器满,高电平有效。

36

INTR:中断请求信号,高电平有效 。STB#上升沿使INTR从无效到有效 ,请求CPU读数据。CPU接到INTR, 读数据发送RD#,RD#下降沿变INTR 有效为无效,表示已经得到响应, RD#上升沿使IBF满变为不满,表示 数据已经读走。 INTE:中断允许信号,它是通过端 口PC4(端口A)或PC2(端口B)的位来编 程的内部位。

ACK: 外设应答信号。该信号的下 降沿使OBF臵高,表示输出缓冲器 空,低电平有效.当外设读取数据以 后,由外设输入给8255,表示数据

42

INTR:中断请求信号。写信 号的下降沿使INTR引脚无效, 表示CPU正在响应中断,高电 平有效。

INTE : 中断允许信号。在中

断允许情况下, ACK 的

出数据均受到锁存。

端口 B 和 C: 都包含一个 8 位数据输入缓

冲器和一个 8位的数据输出锁存器和缓冲器,

输出数据能锁存,输入数据不锁存。

7

端口 C: 可分成两个 4 位端口,分别定义 为输入或输出端口,还可定义为控制、状 态端口,配合端口A和端口B工作。 在实际应用中C口 的8位可分为两个4位

第八章 输入输出接口8255A(8.1-8.3)

B组控制电路用来控制B口及C口的低4位。

3、 数据总线缓冲器 8位的双向的三态缓冲器。作为8255A与系统总线连 接的界面,输入/输出的数据,CPU的编程命令以及外设 通过8255A传送的工作状态等信息,都是通过它来传输的。 4、 读/写控制部件

读 / 写控制逻辑电路负责管理 8255A 的数据传输过程。

RS-232C标准(协定)的全称是EIA-RS-232C标 准,其中EIA(Electronic Industry Association)代表美 寻址外设: 国电子工业协会,它规定连接电缆和机械、电气特性 、信号功能及传送过程。RS-232C接口最大传输速率 不同的外设需要不同的接口电路 为20Kbps,线缆最长为15米。RS-232C接口通常被用 同一外设中存在不同的端口 于将电脑信号输入控制,当通信距离较近时,可不需 信息变换: 要Modem,通信双方可以直接连接,这种情况下,只 CPU与外设的信息编码方式不同,如七段数码管 需使用少数几根信号线。

一个控制寄存器 ,用来接收CPU对它的控制命令。 一个状态寄存器,提供各种状态位供CPU查询。 输入缓冲寄存器和输出寄存器,实现输入和输出。

1.输入过程

输入缓冲寄存器

图8-4(P199)

2.输出过程

§8-3 可编程并行通信接口8255A

8255A是INTEL系列的并行接口芯片。它是可编程 的,可以通过软件来设置芯片的工作方式。

将80H端口的内容送AL。

M/IO=1(此为8088引脚),RD=0, AL=10H

例2:输出:OUT 82H,AL;AL=10H 将AL中的内容送82H端口。 M/IO=1,WR=0,(82H)=10H

无条件传送方式小结:

3、 数据总线缓冲器 8位的双向的三态缓冲器。作为8255A与系统总线连 接的界面,输入/输出的数据,CPU的编程命令以及外设 通过8255A传送的工作状态等信息,都是通过它来传输的。 4、 读/写控制部件

读 / 写控制逻辑电路负责管理 8255A 的数据传输过程。

RS-232C标准(协定)的全称是EIA-RS-232C标 准,其中EIA(Electronic Industry Association)代表美 寻址外设: 国电子工业协会,它规定连接电缆和机械、电气特性 、信号功能及传送过程。RS-232C接口最大传输速率 不同的外设需要不同的接口电路 为20Kbps,线缆最长为15米。RS-232C接口通常被用 同一外设中存在不同的端口 于将电脑信号输入控制,当通信距离较近时,可不需 信息变换: 要Modem,通信双方可以直接连接,这种情况下,只 CPU与外设的信息编码方式不同,如七段数码管 需使用少数几根信号线。

一个控制寄存器 ,用来接收CPU对它的控制命令。 一个状态寄存器,提供各种状态位供CPU查询。 输入缓冲寄存器和输出寄存器,实现输入和输出。

1.输入过程

输入缓冲寄存器

图8-4(P199)

2.输出过程

§8-3 可编程并行通信接口8255A

8255A是INTEL系列的并行接口芯片。它是可编程 的,可以通过软件来设置芯片的工作方式。

将80H端口的内容送AL。

M/IO=1(此为8088引脚),RD=0, AL=10H

例2:输出:OUT 82H,AL;AL=10H 将AL中的内容送82H端口。 M/IO=1,WR=0,(82H)=10H

无条件传送方式小结:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

它接收片选信号及系统读信号 、写信号、复位信号 RESET,还有来自系统地址总线的端口地址选择信号A0 和A1。

DMA 的传送原理

实现DMA传送的基本操作如下:

DMA方式的主要优点是速度快,数据传送速度只受存贮器存取时间的限 制,其缺点是需要一个专用的芯片——DMA控制器来加以控制、管理, 硬件连接也稍为复杂些。一般微处理器都设有用于DMA传送请求的应答 联络线。实现DMA传送的基本操作如下: ① 外设可通过DMA控制器向CPU发出DMA请求;如DMA控制器通过向 8086/8088的HOLD引脚发送一个高电平信号。 ② CPU响应DMA请求,把总线控制权交给DMA控制器,使系统转变为 DMA工作方式;如8086/8088CPU在现行总线周期完成后作出响应,使 HLDA引脚变成高电平,通知DMA控制器可以使用系统总线。

③ DMA控制器接收到HLDA引脚的高电平后,掌握系统总线控制权。由 DMA控制器发出I/O数据的存贮地址,并决定传送数据块的长度;

④ 执行DMA传送; ⑤ DMA操作结束,并将控制权交还给CPU。撤销发向HOLD引脚的总线 请求信号,CPU重新获得对系统总线的控制权。

2、DMA的功能:

A端口引脚 ,连外设 控制信号 ,与CPU 相连

端口选择 信号

C端口引脚 ,连外设或 作为控制

与CPU相 连的双向 数据线

B端口引脚 ,连外设

图8-6 8255A 的芯片引脚图

2、 A组和B组控制部件

这是两组根据CPU命令控制8255A工作方式的电路,这

些控制电路内部设有控制寄存器,可以根据CPU送来的编程 命令来控制8255A的工作方式,也可以根据编程命令来对C口 的指定位进行置/复位的操作。 A组控制电路用来控制A口及C口的高4位;

CPU通过状态端口输入外设的状态信号

CPU与外设的数据宽度不同,如并-串转换

CPU与外设的电平逻辑不同,如RS-232C

8-1、微型计算机的输入输出方式

接口就是CPU与外界的连接部件,是CPU与外界交换 信息的中转站。

原始数据通过接口由输入设备送进去; 运算结果通过接口由输出设备送出来; 控制命令通过接口发出去;

一个控制寄存器 ,用来接收CPU对它的控制命令。 一个状态寄存器,提供各种状态位供CPU查询。 输入缓冲寄存器和输出寄存器,实现输入和输出。

1.输入过程

输入缓冲寄存器

图8-4(P199)

2.输出过程

§8-3 可编程并行通信接口8255A

8255A是INTEL系列的并行接口芯片。它是可编程 的,可以通过软件来设置芯片的工作方式。

优点:软件比较简单

缺点:CPU效率低,数据传送的实时性差, 速度较慢

二 中断控制传送方式(P198)

1).中断传送方式的原理

启动外设 外设准备好数据,发一个选通信号 外设向CPU发中断请求 CPU受到中断请求信号,暂停现行程序

CPU执行中断服务程序,执行输入输出操作

§8-2 并行通信和并行接口

并行通信就是把一个字符的各数位用几条线进行传输。 和串行通信相比,在同样的传输率下,并行通信的信 息实际传输速度快,信息率高。 实现并行通信的接口就是并行接口。 一个并行接口可以设计为只用来作为输出接口,也可 以只用来作为输入接口,此外,还可以将它设计成既 作为输入又作为输出的接口。

– 发光器件(如发光二极管、7段数码管、灯泡等)

– 继电器 – 步进电机

Hale Waihona Puke 优点:软件及接口硬件简单

缺点:只适用于简单外设,适应范围较窄

2、条件(查询)传送方式 程序测试外 设的状态,若满足,传送。不满足,等待。

即CPU在I/O操作前,必须首先查询外设的状态;

若外设未准备好,则继续查询等待; 若外设准备好,则直接I/O; 需增加状态端口。 数据传送过程:

现场数据通过接口从输入设备送进去。

8-1-1、CPU和I/O设备之间的信号

一)、数据信息(详细见书本P196) 1、数字量 2、模拟量 3、开关量 4、脉冲量 二)、状态信息 反映当前外设所处的工作状态。 三)、控制信息 CPU 通过接口向外设传送控制信息。

接口部件的I/O端口

一个接口有几个寄存器,不同类型的信息进 入不同的寄存器,一般称这些寄存器为端口。

缺点:程序的执行速度限定了传送的最大速 度(约为几十KB/秒)—解决:DMA传输

DMA传输:

外设

内存

– 外设直接与存储器进行数据交换 ,CPU不再担 当数据传输的中介者; – 总线由DMA控制器(DMAC)进行控制(CPU 要放弃总线控制权),内存/外设的地址和读写 控制信号均由DMAC提供。

第八章

8-1 8-2 8-3 8-4 8-5

输入/输出接口

微型计算机的输入/输出接口 并行通信与并行接口 可编程并行通信接口芯片8255A 串行通信与串行接口 可编程串行通信接口芯片8251A

第八章 小结

学习内容

1. 微机的输入/输出接口

2. 并行通信与并行接口

3. 串行通信与串行接口

输入输出接口技术 的基本要领

①能接受外设的请求,并能向CPU发DMA请求信号;

②CPU接到DMA请求信号,如果允许,CPU发DMA响应信号,

DMA控制器接管总线,进入DMA方式; ③能寻址存储器,并修改地址; ④能向外设发读/写信号; ⑤能控制传诵的字节数,判断DMA是否结束;

⑥DMA结束时,能向CPU发出结束信号,将总线控制权交

注:相应的查询式输 入输出接口电路见书 本图8-2与图8-3,见 P197-198

查询部分的程序: POLL:IN AL,S-PORT ;读入状态

TEST AL,40H

JNZ POLL

;检查忙标志

MOV AL,STORE

OUT D-PORT,AL …….. ;输出数据

条件传送方式小结:

适用于外设并不总是准备好,而且对传送速率、传送效率 要求不高的场合。 CPU在与外设交换数据前必须询问外设状态——“你准备 好没有?” 对外设的要求:应提供设备状态信息 对接口的要求:需要提供状态端口

将80H端口的内容送AL。

M/IO=1(此为8088引脚),RD=0, AL=10H

例2:输出:OUT 82H,AL;AL=10H 将AL中的内容送82H端口。 M/IO=1,WR=0,(82H)=10H

无条件传送方式小结:

适用于总是处于准备好状态的外设 以下外设可采用无条件传送方式: – 开关

写信号

M/IO

&

输入端口

读信号

WR

RD

&

图8-1、无条件传送

1、执行输入指令时,例:IN AL,80H, RD信号有,M/IO=0,输入三态缓冲 器,被选通,已准备好的数据进入数据总线,送到AL. 2.执行输入指令时,

M/IO有效(8086)

&

读信号有效 80H

&

例1:输入:IN

AL,80H;(80H)=10H

B组控制电路用来控制B口及C口的低4位。

3、 数据总线缓冲器 8位的双向的三态缓冲器。作为8255A与系统总线连 接的界面,输入/输出的数据,CPU的编程命令以及外设 通过8255A传送的工作状态等信息,都是通过它来传输的。 4、 读/写控制部件

读 / 写控制逻辑电路负责管理 8255A 的数据传输过程。

常用的三 种传送控 制方式

一、程序传送方式

由程序控制CPU与外设之间的数据交换。

1)、无条件传送方式

外设已准备好,不查询外设的状态。CPU 不关心外设的状态,直接进行I/O操作 输入时,外设的数据已送到三态缓冲器。 输出时,CPU的输出信息已送到输出锁存器 的输入端。

数据

D7-D0

输出端口

选中地址

优点:数据传输由DMA硬件来控制,数据直接在内 存和外设之间交换,可以达到很高的传输速率(可 达几MB/秒)

三、直接存储器存取方式(DMA) (Direct Memory Access)

为什么要用DMA方式传送数据 什么是DMA方式 DMA传送原理 DMA控制器的工作特点

(一)、为什么要用DMA方式传送数据

RS-232C标准(协定)的全称是EIA-RS-232C标 准,其中EIA(Electronic Industry Association)代表美 寻址外设: 国电子工业协会,它规定连接电缆和机械、电气特性 、信号功能及传送过程。RS-232C接口最大传输速率 不同的外设需要不同的接口电路 为20Kbps,线缆最长为15米。RS-232C接口通常被用 同一外设中存在不同的端口 于将电脑信号输入控制,当通信距离较近时,可不需 信息变换: 要Modem,通信双方可以直接连接,这种情况下,只 CPU与外设的信息编码方式不同,如七段数码管 需使用少数几根信号线。

查询方式传送数据:

查询时占用CPU时间

中断方式传数据:

比查询方式传送数据效率要高,但执行中 断服务程序,CPU要保护断点、保护一些寄存 器等操作,使CPU花费时间。

DMA方式

用专用接口电路直接和存储器进行数据传 送。

(二)、DMA的传送原理

1、DMA控制器与其它接口电路的不同点: 具有接管和控制系统总线的功能,但在取 得总线控制权之前,与其它接口芯片一样,受 CPU的控制。 在DMA方式,DMA管理总线,控制传送数据 的开始与结束,传送的字节数,传送的方向及 地址。

8-3-1、8255A的内部结构及其功能

1.数据端口A、B、C

DMA 的传送原理

实现DMA传送的基本操作如下:

DMA方式的主要优点是速度快,数据传送速度只受存贮器存取时间的限 制,其缺点是需要一个专用的芯片——DMA控制器来加以控制、管理, 硬件连接也稍为复杂些。一般微处理器都设有用于DMA传送请求的应答 联络线。实现DMA传送的基本操作如下: ① 外设可通过DMA控制器向CPU发出DMA请求;如DMA控制器通过向 8086/8088的HOLD引脚发送一个高电平信号。 ② CPU响应DMA请求,把总线控制权交给DMA控制器,使系统转变为 DMA工作方式;如8086/8088CPU在现行总线周期完成后作出响应,使 HLDA引脚变成高电平,通知DMA控制器可以使用系统总线。

③ DMA控制器接收到HLDA引脚的高电平后,掌握系统总线控制权。由 DMA控制器发出I/O数据的存贮地址,并决定传送数据块的长度;

④ 执行DMA传送; ⑤ DMA操作结束,并将控制权交还给CPU。撤销发向HOLD引脚的总线 请求信号,CPU重新获得对系统总线的控制权。

2、DMA的功能:

A端口引脚 ,连外设 控制信号 ,与CPU 相连

端口选择 信号

C端口引脚 ,连外设或 作为控制

与CPU相 连的双向 数据线

B端口引脚 ,连外设

图8-6 8255A 的芯片引脚图

2、 A组和B组控制部件

这是两组根据CPU命令控制8255A工作方式的电路,这

些控制电路内部设有控制寄存器,可以根据CPU送来的编程 命令来控制8255A的工作方式,也可以根据编程命令来对C口 的指定位进行置/复位的操作。 A组控制电路用来控制A口及C口的高4位;

CPU通过状态端口输入外设的状态信号

CPU与外设的数据宽度不同,如并-串转换

CPU与外设的电平逻辑不同,如RS-232C

8-1、微型计算机的输入输出方式

接口就是CPU与外界的连接部件,是CPU与外界交换 信息的中转站。

原始数据通过接口由输入设备送进去; 运算结果通过接口由输出设备送出来; 控制命令通过接口发出去;

一个控制寄存器 ,用来接收CPU对它的控制命令。 一个状态寄存器,提供各种状态位供CPU查询。 输入缓冲寄存器和输出寄存器,实现输入和输出。

1.输入过程

输入缓冲寄存器

图8-4(P199)

2.输出过程

§8-3 可编程并行通信接口8255A

8255A是INTEL系列的并行接口芯片。它是可编程 的,可以通过软件来设置芯片的工作方式。

优点:软件比较简单

缺点:CPU效率低,数据传送的实时性差, 速度较慢

二 中断控制传送方式(P198)

1).中断传送方式的原理

启动外设 外设准备好数据,发一个选通信号 外设向CPU发中断请求 CPU受到中断请求信号,暂停现行程序

CPU执行中断服务程序,执行输入输出操作

§8-2 并行通信和并行接口

并行通信就是把一个字符的各数位用几条线进行传输。 和串行通信相比,在同样的传输率下,并行通信的信 息实际传输速度快,信息率高。 实现并行通信的接口就是并行接口。 一个并行接口可以设计为只用来作为输出接口,也可 以只用来作为输入接口,此外,还可以将它设计成既 作为输入又作为输出的接口。

– 发光器件(如发光二极管、7段数码管、灯泡等)

– 继电器 – 步进电机

Hale Waihona Puke 优点:软件及接口硬件简单

缺点:只适用于简单外设,适应范围较窄

2、条件(查询)传送方式 程序测试外 设的状态,若满足,传送。不满足,等待。

即CPU在I/O操作前,必须首先查询外设的状态;

若外设未准备好,则继续查询等待; 若外设准备好,则直接I/O; 需增加状态端口。 数据传送过程:

现场数据通过接口从输入设备送进去。

8-1-1、CPU和I/O设备之间的信号

一)、数据信息(详细见书本P196) 1、数字量 2、模拟量 3、开关量 4、脉冲量 二)、状态信息 反映当前外设所处的工作状态。 三)、控制信息 CPU 通过接口向外设传送控制信息。

接口部件的I/O端口

一个接口有几个寄存器,不同类型的信息进 入不同的寄存器,一般称这些寄存器为端口。

缺点:程序的执行速度限定了传送的最大速 度(约为几十KB/秒)—解决:DMA传输

DMA传输:

外设

内存

– 外设直接与存储器进行数据交换 ,CPU不再担 当数据传输的中介者; – 总线由DMA控制器(DMAC)进行控制(CPU 要放弃总线控制权),内存/外设的地址和读写 控制信号均由DMAC提供。

第八章

8-1 8-2 8-3 8-4 8-5

输入/输出接口

微型计算机的输入/输出接口 并行通信与并行接口 可编程并行通信接口芯片8255A 串行通信与串行接口 可编程串行通信接口芯片8251A

第八章 小结

学习内容

1. 微机的输入/输出接口

2. 并行通信与并行接口

3. 串行通信与串行接口

输入输出接口技术 的基本要领

①能接受外设的请求,并能向CPU发DMA请求信号;

②CPU接到DMA请求信号,如果允许,CPU发DMA响应信号,

DMA控制器接管总线,进入DMA方式; ③能寻址存储器,并修改地址; ④能向外设发读/写信号; ⑤能控制传诵的字节数,判断DMA是否结束;

⑥DMA结束时,能向CPU发出结束信号,将总线控制权交

注:相应的查询式输 入输出接口电路见书 本图8-2与图8-3,见 P197-198

查询部分的程序: POLL:IN AL,S-PORT ;读入状态

TEST AL,40H

JNZ POLL

;检查忙标志

MOV AL,STORE

OUT D-PORT,AL …….. ;输出数据

条件传送方式小结:

适用于外设并不总是准备好,而且对传送速率、传送效率 要求不高的场合。 CPU在与外设交换数据前必须询问外设状态——“你准备 好没有?” 对外设的要求:应提供设备状态信息 对接口的要求:需要提供状态端口

将80H端口的内容送AL。

M/IO=1(此为8088引脚),RD=0, AL=10H

例2:输出:OUT 82H,AL;AL=10H 将AL中的内容送82H端口。 M/IO=1,WR=0,(82H)=10H

无条件传送方式小结:

适用于总是处于准备好状态的外设 以下外设可采用无条件传送方式: – 开关

写信号

M/IO

&

输入端口

读信号

WR

RD

&

图8-1、无条件传送

1、执行输入指令时,例:IN AL,80H, RD信号有,M/IO=0,输入三态缓冲 器,被选通,已准备好的数据进入数据总线,送到AL. 2.执行输入指令时,

M/IO有效(8086)

&

读信号有效 80H

&

例1:输入:IN

AL,80H;(80H)=10H

B组控制电路用来控制B口及C口的低4位。

3、 数据总线缓冲器 8位的双向的三态缓冲器。作为8255A与系统总线连 接的界面,输入/输出的数据,CPU的编程命令以及外设 通过8255A传送的工作状态等信息,都是通过它来传输的。 4、 读/写控制部件

读 / 写控制逻辑电路负责管理 8255A 的数据传输过程。

常用的三 种传送控 制方式

一、程序传送方式

由程序控制CPU与外设之间的数据交换。

1)、无条件传送方式

外设已准备好,不查询外设的状态。CPU 不关心外设的状态,直接进行I/O操作 输入时,外设的数据已送到三态缓冲器。 输出时,CPU的输出信息已送到输出锁存器 的输入端。

数据

D7-D0

输出端口

选中地址

优点:数据传输由DMA硬件来控制,数据直接在内 存和外设之间交换,可以达到很高的传输速率(可 达几MB/秒)

三、直接存储器存取方式(DMA) (Direct Memory Access)

为什么要用DMA方式传送数据 什么是DMA方式 DMA传送原理 DMA控制器的工作特点

(一)、为什么要用DMA方式传送数据

RS-232C标准(协定)的全称是EIA-RS-232C标 准,其中EIA(Electronic Industry Association)代表美 寻址外设: 国电子工业协会,它规定连接电缆和机械、电气特性 、信号功能及传送过程。RS-232C接口最大传输速率 不同的外设需要不同的接口电路 为20Kbps,线缆最长为15米。RS-232C接口通常被用 同一外设中存在不同的端口 于将电脑信号输入控制,当通信距离较近时,可不需 信息变换: 要Modem,通信双方可以直接连接,这种情况下,只 CPU与外设的信息编码方式不同,如七段数码管 需使用少数几根信号线。

查询方式传送数据:

查询时占用CPU时间

中断方式传数据:

比查询方式传送数据效率要高,但执行中 断服务程序,CPU要保护断点、保护一些寄存 器等操作,使CPU花费时间。

DMA方式

用专用接口电路直接和存储器进行数据传 送。

(二)、DMA的传送原理

1、DMA控制器与其它接口电路的不同点: 具有接管和控制系统总线的功能,但在取 得总线控制权之前,与其它接口芯片一样,受 CPU的控制。 在DMA方式,DMA管理总线,控制传送数据 的开始与结束,传送的字节数,传送的方向及 地址。

8-3-1、8255A的内部结构及其功能

1.数据端口A、B、C