嵌入系统中断控制器的设计

嵌入式系统的设计和实现

嵌入式系统的设计和实现嵌入式系统是指集成了计算机芯片、控制器、传感器等硬件设备的特殊电子设备系统。

它通常运行在一些资源受限的嵌入式处理器上,具有实时性、可靠性、成本低廉等特点。

如今,随着信息技术的迅速发展,嵌入式系统已经广泛应用在各种领域,例如智能家居、智能交通、智能医疗等。

嵌入式系统设计开发的核心,在于硬件电路的设计和程序代码的编写。

本文将从嵌入式系统的设计和实现两个方面,探讨如何开发一款成功的嵌入式系统。

一、嵌入式系统的设计1.硬件电路设计嵌入式系统的硬件设计是系统整体性能的基础,是开发过程中必不可少的一步。

在设计硬件电路时,需要首先了解嵌入式系统所需的硬件组件,比如处理器、存储器、输入输出设备、传感器等。

其次,需要根据设计目标和系统要求,选择合适的硬件设备,并将其组合成合理的电路结构。

最后,需要完成电路设计的的绘制及原理图、PCB的布线等工作。

在这个过程中,设计者需要考虑功耗、散热、成本等多个因素。

2.软件设计嵌入式系统的软件设计是嵌入式系统开发的重中之重。

在软件设计方面,需要仔细考虑嵌入式系统的程序架构及程序设计模式,比如事件驱动模型或多任务模型。

同时,需要考虑系统的实时性和稳定性,确保系统代码的质量和可靠性。

在软件设计过程中,需要使用一些工具和开发环境,如Keil、IAR、Eclipse等集成开发环境。

3.测试与调试测试和调试是嵌入式系统开发的重要环节,只有将系统进行充分测试与调试,才能保证系统的正确性和稳定性。

在测试过程中,需要首先进行各个模块的单元测试,以验证系统的功能是否正常。

然后进行集成测试,交叉验证各个模块的协同工作是否正常。

最后进行耐久性测试和压力测试,确保系统能够在各种恶劣环境环境下正常运行。

二、嵌入式系统的实现1. 系统内核系统内核是嵌入式操作系统的核心,也是嵌入式系统的核心。

系统内核需要提供一个可靠的执行环境和一些重要的操作系统服务,如任务管理、内存管理、中断管理、设备驱动程序和通讯协议等。

C51单片机的几种常用延时程序设计2024

引言概述:C51单片机是一种广泛应用于嵌入式系统中的微控制器,它具有高度集成化、易于编程和灵活性强等特点。

在C51单片机的软件开发过程中,延时程序设计是非常重要的一部分。

本文将介绍C51单片机中几种常用的延时程序设计方法,包括循环延时、定时器延时、外部中断延时等。

这些方法不仅可以满足在实际应用中对延时的需求,而且可以提高程序的稳定性和可靠性。

正文内容:一、循环延时1. 使用循环控制语句实现延时功能,例如使用for循环、while循环等。

2. 根据需要设置延时的时间,通过循环次数来控制延时的时长。

3. 循环延时的精度受到指令执行时间的影响,可能存在一定的误差。

4. 循环延时的优点是简单易用,适用于较短的延时时间。

5. 注意在循环延时时要考虑其他任务的处理,避免长时间的等待造成程序卡死或响应延迟。

二、定时器延时1. 使用C51单片机内置的定时器模块来实现延时。

2. 配置定时器的工作模式,如工作方式、定时器精度等。

3. 设置定时器的初值和重装值,控制定时器中断的触发时间。

4. 在定时器中断服务函数中进行延时计数和延时结束标志的设置。

5. 定时器延时的优点是精确可控,适用于需要较高精度的延时要求。

三、外部中断延时1. 在C51单片机上配置一个外部中断引脚。

2. 设置外部中断中断触发条件,如上升沿触发、下降沿触发等。

3. 在外部中断中断服务函数中进行延时计数和延时结束标志的设置。

4. 外部中断延时的优点是能够快速响应外部信号,适用于实时性要求较高的场景。

5. 注意在外部中断延时时要处理好外部中断的抖动问题,确保延时的准确性。

四、内部计时器延时1. 使用C51单片机内部的计时器模块来实现延时。

2. 配置计时器的工作模式,如工作方式、计时器精度等。

3. 设置计时器的初值和重装值,使计时器按照一定的频率进行计数。

4. 根据计时器的计数值进行延时的判断和计数。

5. 内部计时器延时的优点是能够利用单片机内部的硬件资源,提高延时的准确性和稳定性。

片上系统中断机制的可靠性设计

Re i b l y o n e r p e h n s n S C l i t fI t r u tM c a im i o a i

W e P n u ine gAn Xio aF n n igS o Ja fn a y a

进 入核 心态 , 如果 中断机 制存 在 问题 , 在严 重情 况下

可能导致安全漏洞和系统隐患。因而 中断机制的可

靠性问题对于高可靠性系统来说是一个重要 问题 。

维普资讯

L I

设 计

I_ 置 舢 出 _ I W 圈 I W_

本文尝试对 中断机制的可靠性问题进行 了一些探 这 里 所 涉 及 的安 全 问题 主要 是 不 会 遗 漏 发 生 的 中 讨, 从中断检测 、 中断转移和中断处理三个角度提 出 了安全性原则和相关的解决方法 , 并针对这些问题

r l b l y o t ru tme h im. n t i p p r e tyt l b u ei b l y o tr u t c a im. e s g e t ei i t f n e r p c a s I s a e ,w r ot k a o t l i t f n e r p a i i n h a r a i i me h s W u g s n a ei oa c u t ei i t f n e r p h s f m e r p t ci , n e r p a se e r p ai . tk t c o n l b l y o tr u t c a im o i tr u t ee t n i tru t r n fra d it ru t e l g n r a i i me n r n d o t n n d n W ea s i eaw oe s l t n i a e i . logv h l o u i ar l d sg o n e n Ke r s I tru t Rei b l y S C y wo d : n e r p , l i t , o a i

ARM嵌入式系统中触摸屏的中断控制方法

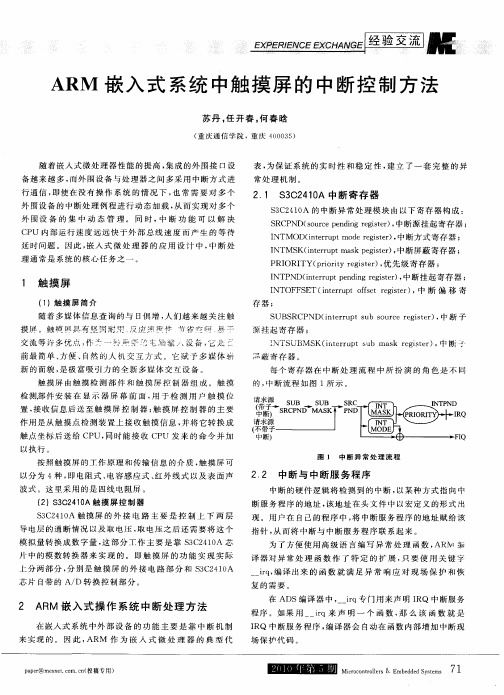

2 2 中 断 与 中 断 服 务 程序 .

中 断 的硬 件 逻辑 将 检 测 到 的 中 断 , 以某 种 方 式 指 向 中 断 服 务 程 序 的 地 址 , 地 址 在 头 文 件 中以 宏 定 义 的 形 式 出 该 现 。用 户 在 自己 的程 序 中 , 中断 服 务 程 序 的 地址 赋 给 该 将 指 针 , 而将 中 断 与 中 断 服 务 程 序联 系起 来 。 从 为 了方 便 使 用 高 级 语 言 编 写 异 常 处 理 函数 , ARM

常处理机制 。

备 越来 越 多 , 而外 围设 备 与处 理 器 之 间 多采 用 中 断 方 式 进

行通信 , 即使 在 没有 操 作 系统 的 情 况 下 , 常 需 要 对 多 个 也 外 围设 备 的 中断 处 理 例 程 进 行 动 态 加 载 , 而实 现 对 多个 从

外 围 设 备 的 集 中 动 态 管 理 。 同 时 , 断 功 能 可 以 解 决 中

译 器 对 异 常处 理 函数 作 了 特 定 的 扩 展 , 要 使 用 关 键 字 只

一

¥ C 4 0 触 摸屏 的 外 接 电 路 主 要 是 控 制 上 下 两 层 3 21A 导电层 的通 断 情 况 以及 取 电压 , 电压 之 后 还 需 要 将 这 个 取 模 拟 量 转 换 成 数 字 量 , 部 分 _ 作 主 要 是 靠 ¥ C2 1 A 芯 这 T 3 40

复 的需 要 。

2 A M 嵌 入 式 操 作 系统 中断处 理 方 法 R

I NTP ND( tru tp n igrgse) 中断 挂 起 寄存 器 ; i er p e dn e i r , n t

基于Xilinx FPGA的中断处理

本栏目责任编辑:梁书计算机工程应用技术基于Xilinx FPGA 的中断处理杨媛媛,王晓华,李敏,冯思桐(航空工业西安航空计算技术研究所,陕西西安710069)摘要:在嵌入式系统和各类操作系统中,中断是系统确保实时响应各类异步事件的重要机制。

中断驱动系统的合理设计能够保证在完整实现系统功能的同时,保证系统设计的正确性和时间约束。

本文研究了典型Xilinx FPGA 芯片中的中断处理,提出了一种中断队列处理方法,并在一款基于Xilinx FPGA 芯片开发的通信子卡上对该方法进行了验证。

关键词:中断处理;FPGA ;SDK 中图分类号:TP18文献标识码:A文章编号:1009-3044(2021)05-0244-02开放科学(资源服务)标识码(OSID ):中断是指处理器受到内部或外部事件触发,暂停当前程序的执行,转而执行处理紧急事件的处理程序,并在该事件处理完后能自动恢复执行原先程序的过程。

我们称引起紧急事务的事件为中断事件,处理紧急事务的程序为中断服务例程。

在嵌入式系统和各类操作系统中,中断是系统确保实时响应各类异步事件的重要机制。

中断驱动系统的合理设计能够保证在完整实现系统功能的同时,保证系统设计的正确性和时间约束。

本文首先介绍了Xillinx FPGA 芯片中典型利用中断控制器核进行中断处理的原理,其次典型处理方法存在的弊端,针对性地设计了一种队列中断处理方法,并在一款基于Xilinx FP⁃GA 芯片开发的通信子卡上对该方法进行了验证。

1典型中断处理方法在进行软件开发时,设计人员可以通过XILLINX 公司提供的中断控制器核来进行管理中断。

中断控制器核可以同时接收并判别多个外部中断,根据优先级的高低顺序向处理器输送中断请求,当处理器响应中断并进入中断处理例程后,该控制器仍负责对外部中断的管理[5]。

开发人员为每一种类型的中断分配中断状态寄存器的某一个比特位,当中断到来时,将对应比特位置1,同时调用对应的中断处理例程进行中断处理,软件人员可通过查看中断状态寄存器的值来获知当前的中断情况,处理完中断后,将对应的中断状态位清零,即完成本次中断处理。

基于ARM的嵌入式系统设计硕士学位论文

硕士学位论文基于ARM的嵌入式系统设计第一章摘要嵌入式系统以其小型、专用、易携带、可靠性高的特点,已经在各个领域得到了广泛的应用,如军事国防、消费电子、通信设备、工业控制等。

嵌入式处理器内嵌实时操作系统(RTOS),具有实时性、低成本、小型化、专用化和高可靠性,克服了传统的基于单片机控制系统功能不足和基于PC的系统非实时性的缺点。

随着嵌入式系统软硬件技术的飞速发展,其应用领域必将更为广阔,嵌入式系统的研究将会有非常广泛的前景。

本课题的目的就是研究适用于学校教学的嵌入式系统平台,这对于提高对嵌入式系统的理解具有重要意义。

本课题以嵌入式系统设计原理和实际应用为核心,从理论上和技术方法上开展了一系列研究。

主要工作有: 1、全面系统地概述了嵌入式系统的发展过程和分类,及其在各个领域内的应用,以及嵌入式系统的发展方向;2、基于嵌入式系统设计原理的嵌入式开发平台的设计的总体方案,从硬件和软件两个方面讲述了嵌入式系统的设计思想和方法,及其可行性的论证;3、嵌入式系统硬件平台的设计与调试,着重叙述了硬件平台的整体设计方案,包括各个设计模块的选型与接口电路的设计;4、嵌入式系统所采用的操作系统的移植与调试,详细讲叙了µC/OS-II实时操作系统在基于LPC2136的嵌入式控制器硬件平台上的移植过程及注意事项;5、对µC/OS-II内核实时性能进行了深入的分析,通过实际测试得出了在特定条件下µC/OS-II的实时响应参数。

6、在后继的工作中,我们还要在实时嵌入式操作系统的基础上完成对操作系统的扩展以及对各个模块的驱动。

总之,本文完成了嵌入式系统的硬件平台构架、实时嵌入式操作系统的移植,为今后嵌入式系统的后继开发提供了一个嵌入式平台。

关键词:嵌入式系统ARM RTOS µC/OS-II第二章AbstractWith the development of IT network technology, embedded system shows a new direction of technology development. Embedded system has been applied in military, electronics, communication, industrial control and so on, with respect to its small size, high performance, low cost, high reliability and oriented object program.Embedded controller with RTOS gets over the traditional microcontroller and the disadvantage of the un-real time specialty base on pc, instead it is real-time, low cost ,miniaturized ,customized ,and high dependability. It also has a broad foreground , along with the fast development of hardware of embedded system .This intention of this topic is designing the embedded system, which is important for enhancing the understanding of embedded system. The research is highlighted in both design theory and applications of embedded system, which extended its developments. This paper is organized into six parts:1. This article essentially introduced the development of embedded system, its classification, applications in numerous areas, and its development orientation.2. The second chapter covers the general design of the embedded system, based on the elements of embedded system design. then it shows the devise ideology and methods in either hardware or software, and the demonstration of its accessibility.3. The third chapter gives out the hardware of the embedded system, including design, test and implementation of each module, as well as their interface circuitry.4. The forth chapter introduces the process and attentions of RTOS µC/OS-II, when explanted to the LPC2136 embedded controller hardware platform.5. It covers a in-dept analyzing in the real-time performance in μC/OS-II core, as well as the real time respond parameter in the very condition.6. In the future, we will expand the operation system based on RTOS, and derivations of each module.In a word, the article provides keen insight into the platform architecture of hardware and explants of the RTOS, in addition to affording an embedded platform for the subsequence developments.Key word: embedded system ARM RTOS µC/OS-II目录第一章绪论......................................................................... 错误!未定义书签。

nvic中断的工作原理和使用方法 -回复

nvic中断的工作原理和使用方法-回复NVIC(Nested Vectored Interrupt Controller)中断控制器是一种常见于嵌入式系统中的硬件模块,用于管理和分配系统中断。

在本文中,我们将详细介绍NVIC中断的工作原理和使用方法。

1. 中断的概念和作用:在嵌入式系统中,中断是一种重要的机制,用于处理来自外部设备或软件的异步事件。

中断可以让处理器立即暂停当前任务,转而处理更为紧急的事件,提高系统的响应能力和实时性。

NVIC中断控制器负责管理和分配中断,使系统能够有效地响应和处理中断事件。

2. NVIC中断控制器的组成:NVIC中断控制器由多个寄存器组成,其中包括以下几个重要的寄存器:- ISER(Interrupt Set Enable Register):用于设置或清除中断的使能位。

当某个中断使能位被设置时,表示该中断已经被使能,可以触发中断服务程序的执行。

- ICER(Interrupt Clear Enable Register):用于清除中断的使能位。

当某个中断使能位被清除时,表示该中断已经被禁止,不会触发中断服务程序的执行。

- ISPR(Interrupt Set Pending Register):用于设置中断的挂起位。

当某个中断挂起位被设置时,表示该中断已经被挂起,正在等待中断服务程序的执行。

- IPR(Interrupt Priority Register):用于设置中断的优先级。

不同中断的优先级不同,高优先级的中断会在低优先级中断之前得到响应和处理。

- IPSR(Interrupt Program Status Register):用于记录当前正在处理的中断号。

3. NVIC中断的工作原理:当外部设备或软件触发一个中断事件时,NVIC中断控制器会根据中断的优先级和使能状态来决定是否响应该中断。

若中断被使能且优先级高于当前正在处理的中断,NVIC中断控制器将触发中断,并根据中断号跳转到对应的中断服务程序(Interrupt Service Routine,ISR)。

ARM9系统的硬件设计

ARM9系统的硬件设计ARM9系统的硬件设计指的是基于ARM9内核的嵌入式系统的硬件组成和设计方法。

ARM9是英国ARM公司推出的第九代32位内核处理器,被广泛应用于移动设备、嵌入式系统、消费电子产品等领域。

下面将详细介绍ARM9系统的硬件设计内容。

一、ARM9系统硬件设计的基本原则1.系统性能和功耗平衡:硬件设计要充分考虑系统性能和功耗之间的平衡,尽量在不影响系统性能的情况下降低功耗。

2.硬件模块化设计:将整个系统划分为多个模块,每个模块负责特定的功能,便于维护和升级。

3.充分利用硬件资源:合理利用硬件资源,提高系统的性能和效率。

4.合理布局和连接:设计时应合理布局硬件组件和引脚连接,减少信号干扰和传输延迟。

5.异常处理:系统设计要考虑到异常情况的处理,保证系统的稳定性和可靠性。

二、ARM9系统硬件设计的基本组成1.处理器:ARM9内核的处理器是系统的核心部件,负责执行指令和控制系统运行。

2.存储器:包括RAM、ROM和闪存等,用于存储指令和数据,RAM用于存储工作数据,ROM和闪存用于存储软件和操作系统。

3.外设接口:包括串口、并口、USB接口等,用于与外部设备通信。

4.时钟和定时器:时钟提供系统的时序和时基,定时器用于定时和计数。

5.中断控制器:用于处理外部中断和异常,保证系统的正常运行。

6.显示控制器:用于控制和管理显示设备,如LCD显示屏。

7.输入输出设备:如触摸屏、键盘、鼠标等,用于用户与系统的交互。

8.电源管理:包括电源管理单元和电源管理软件,用于控制和管理系统的电源消耗。

三、ARM9系统硬件设计的关键技术1.PCB设计:根据系统需求和硬件组件的布局,设计合适的PCB板,保证信号传输的稳定和可靠。

2.时钟设计:根据系统需求设计合适的时钟方案,保证系统的协调和同步。

3.内存管理:根据系统的存储需求,选择适当的存储器类型和容量,合理划分存储区域。

4.性能优化:通过合理的硬件配置和系统参数调整,提高系统的运行速度和性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一定的灵活性。间接中断相对于向量中断具有更高的灵活性, 适用于更加复杂的情况。

!#$

按触发方式,中断分为电位触发中断和边沿触

电位触发方式用一段持续的高电位 (或 低 电 位 ) 表示中断

发中断

请求。这就要求中断请求信号要有足够长的保持时间, 要保持 到当前指令的最后一个机器周期,以保证 %&’ 采样时中断请 求有效。另一方面, 在收到 %&’ 的中断响应信号后, 中断设备 应将中断请求信号复位, 避免误操作。 边沿触发方式是以一个信号的上跳沿 (或 下 跳 沿 ) 表示中 断请求。 %&’ 应对中断请求进行锁存。为防止干扰信号触发中 断,有的边沿触发方式要求中断信号在跳变后维持一段保持 时间。 采用哪种中断触发方式主要取决于中断设备自身的特性。

$

引言

随着 %&’( 技术进入深亚微米时代,芯片集成度得到空前

部分不再由独立的通用中断控制芯片构成, 这就需要系统开发 者根据特定的中断类型设计专用的中断控制器逻辑, 应用于嵌 入系统中。该文将在对中断的类型特点进行介绍之后, 阐述中 断控制器的模块结构以及针对不同类型中断的设计方法及其 实现。该文的重点将着眼于高层次的设计。

的中断触发方式, 图 , 显示了不同中断的有效判别逻辑。针对

图! 中断控制器的模块结构

( 高有效) , 信号可直接经过非门 被 引 入 (1$ 电位触发中断 0=+$ 低有效) ; 针 对 边 沿 触 发 中 断 0=+! (上 升 沿 有 效 ) , 信号应被锁 ; 针 对 边 沿 触 发 且 需 要 保 持 的 中 断 0=+( 存器锁存 (1! 低 有 效 ) (上升沿并保持) , 信号被锁存后还再与信号本 身 做 与 (1( 低 有 效) 。 对边沿触发的中断来说, 被锁存的信号应当在适当的时候

图$

程序流程对中断的响应

基金项目: 国家自然科学基金 (编号: ; 国家 NXP 重点基础研究发展规划项目 (编号: W""XW"$W ) Y$NNC"P"B"P ) 作者简介: 刘建华, 清华大学计算机科学与技术系硕士研究生。

计算机工程与应用 !""!#"$ $!A

根据不同的触发方式、屏蔽方式和中断服务例程调用方 式, 中断可分为不同的类型。 针对不同的中断类型, 中断控制电 路也需要进行不同的设计。中断的具体分类如下:

!#!

中断

按屏蔽方式,中断分为可屏蔽中断和不可屏蔽

由于中断的发生是异步的, 主程序随时有可能被中断服务

(#!

中断标志寄存器模块的设计

中断标志寄存器通常由中断掩码 (-.*/ ) 、 中断允许标志

位和未处理中断标志位组成。当中断允许标志位为禁止中断 时, 所有可屏蔽中断都将被屏蔽。当中断允许标志位为允许中 断时, 各个中断根据自己的掩码标志决定是否被屏蔽。中断掩 码和中断允许标志位, 将被预编码模块作为编码的依据。未处 理中断标志表示了当前已经发生但尚未被 %&’ 处理的中断。 由于未处理中断标志是只读的, 因此中断标志寄存器在读 中断标 取和写入时的含义通常是不同的。以 01234 5"56 为例, 志寄存器的读写格式如图 ( 所示。 -7#6 、 -8#6 和 -6#6 为 可 屏 蔽中断 )*+7#6 、 )*+8#6 和 )*+6#6 的中断掩码。由于 )*+7#6 是 边沿触发,因此需要 )7#6 位对 )*+7#6 中断锁存器进行复位, 此信号是只写的。在读标志寄存器的时候, 未处理中断标志位 及中断允许标志位 (09 ) 将被读出。由于中断标 (0#76 、 08#6 、 06#6 ) 志未用满寄存器的全部 5 位, 在 01234 5"6" 中 , 中断标志和串 行数据 0 : ; 是共享同一寄存器的。 *0< 、 *;< 和 *;9 信 号 是 串 虽 行通讯使用的信 号 , -*9 是 中 断 掩 码 操 作 的 使 能 位 。 另 外 , 然中断允许位是可设置的, 但 01234 5"56 却没有采用对标 志 寄 存器直接写入的方法, 而是利用两条单独的指令对中断允许位 进行设置。

(!""! ) 文章编号 $""!FCPP$F "$F"$!AF"P

!"#$%& ’( )&*"++,-*$’& .’&*+’//"+ $& 012"33"3 45#*"1

6$, 7$8&9,8 :8&% ;,& <$8& 7$&$8& ;," =’&%>$

(R,37<0*,90 8: 28*3=0,< ’65,96, 79- Q,6G9848;. , Q/59;G=7 E95L,</50., S,5M59; $"""CB)

中断服务例程也是存放在内存中的一段代码, 中断服务例程的 启始地址也成为对中断分类的一个标准。 如果某个中断的服务 例程的启始地址是一个固定地址,则称这种中断为直接中断。 如果某中断发生后, %&’ 从总线读入一条转入服务例程的指令 (如 )*+ 指令) , 则称这种中断为向量中断 , 被读入的指令称为 中断向量。 如果服务例程的启始地址由某寄存器 (或寄存器组) 的值决定, 则称这种中断为间接中断。

例程打断。而当主程序在进行某些重要运算时, 中断服务例程 的插入将有可能改变某些临时寄存的数据, 造成主程序的运行 发生错误。 因此在主程序某段代码的运行过程中就可能需要屏 蔽中断, 通过设置屏蔽标志对中断暂时不做响应。能够被屏蔽 掉的中断称为可屏蔽中断。 而另一类中断是在任何时候都不可屏蔽的, 称为不可屏蔽 中断。 一个比较典型的例子是掉电中断, 当发生掉电时, 无论主 程序正在进行什么样的运算, 它都肯定无法正常运行下去。这 种情况下,急需进行的是一些掉电保护的操作。对这类中断,

的提高。不仅仅是单一的功能模块, 甚至是一个完整的系统都 可以被集成在单芯片中。这使得嵌入系统 ()*+,--,- ’./0,*) 具备了性能高、 体积小、 功耗低等特点, 嵌入系统的应用也因此 而迅速地发展起来。不同于传统设计方法, 嵌入系统的设计是 (13345670589 ’3,65:56 (90,;<70,- 25<6=50) 为基础的电路 以 1’(2 设计。 可编程逻辑器件在嵌入系统的设计过程中具有非常重要 的作用。可编程逻辑器件具有可快速修改电路逻辑的特点, 同 时良好的开发环境可以使设计者脱离繁复的底层设计。 这对缩 短嵌入系统的开发周期是至关重要的。 相对而言, 要求用于实现嵌入系统设计的集成电路具有较 高的集成度和较大的规模, 足以将整个嵌入系统装入单个芯片 单芯 中。 以 140,<7 公司的 1>)?!"@ 可编程逻辑器件系列为例, 片 的 规 模 可 达 $A" 万 逻 辑 门 、 B""@ 内 存 容 量 、 以 及 约 C"" 条 可 以 将 2>E 、 内存以及外围器件全部集成到芯片中。 (D 引 脚 , 另外, 与可编程逻辑器件相配合的集成开发环境, 为嵌入系统 的综合、 修改和调试提供了强大的支持。 在实际的嵌入系统应用中, 异步实时交互系统占了很大部 分, 这就要求系统对数据或控制信号的输入具有较高的响应速 度。而中断方式相对于查询方式具有响应速度快, 效率高的特 点。因此中断方式为多数嵌入系统所采用。而中断控制器也由 独立器件变为片上系统的一部分, 因此, 中断控制器的设计也 就成为嵌入系统设计的重要组成部分。 , 中断控制 由于嵌入系统多为片上系统 ( ’./0,*FD9F2G53 )

?2#*+8@*: R5::,<,90 :<8* ;,9,<74F3=<38/, /./0,*, ,*+,--,- /./0,* 07I,/ 89 /8*, ;88- :,70=<, , /=6G 7/ G5;G 590,;<70589 79- G5;G /3,65745T70589#(9 ,*+,--,- /./0,*, /./0,* -,/5;9,</ -8 980 =/, 7 /,37<70, ;,9,<74F3=<38/, 6G53 7/ 79 590,<U <=30589 6890<844,< 6G53 79. 489;,<; 0G,. *=/0 -,/5;9 79 73345670589F/3,65:56 590,<<=30589 6890<844,< 7/ 7 37<0 8: /./0,*# QG5/ 373,< 3<838/,/ 0G, *,0G8- 59 G5;GF4,L,4 -,/5;9 8: 79 ,*+,--,- /./0,* 590,<<=30589 6890<844,<#(0 5/ G,43:=4 08 0G, -,/5;9,< 8: 0G, ,*+,--,- /./0,*# A"5B’+3#: (90,<<=30589 , )*+,--,- /./0,*, V5;GF4,L,4 /.90G,/5/, ><8;<7**7+4, &8;56 R,L56,

在直接中断中, 跳转地址固定, 取指快, 适用于中断服务例 程单一简单的情况。如果在中断发生后, 还需要根据某些参数 决定使用哪个服务例程, 则可以采用向量中断, 向量中断具有

$!8 !""!#"$ 计算机工程与应用

被复位, 即系统复位或中断响应时, 锁存器应被清零。 需要说明 的是, 通常在系统复位时中断锁存器也应被清零, 因此中断锁 存 器 的 清 零 信 号 一 般 也 是 由 中 断 响 应 信 号 与 ,-. 复 位 信 号 “或” 运算后产生。 /)0)’ 进行