第9章(2) 中断系统和中断控制器8259A

8259A可编程中断控制器

ISR2上的1,一直要保持到该中断源的中断处理结束为止,当8259A收到中断结 束命令后,ISR2才被清0,表明连接在IR2上的外设的中断服务已经结束。 有两个以上的“1”,表明有中断嵌套。

设IR2引脚有中断请求,IRR2= 1

IR7引脚 IR6 IR5 IR4 IR3

CPU 响 应 IR2 中断,回送中 断应答信号; 8259 的 INTA 引 脚收到第一个 中断响应信号 , 使 ISR 某 位 ( 如 ISR2) 置 1 时 ,把IRR中某位 (如IRR2)清0

2)内部结构 *1 中断请求寄存器 IRR Interrupt Request Register 功能: 存放中断请求信号直到CPU响应中断为止。

IRR7

:

:

:

IRR0

IR7引脚

IR0引脚 或

IR7~IR0引脚上出现中断请求信号

上升边或高电平表示有中断请求,则相应的位置1。 80X86计算机系统设定的是上升边方式

*2中断屏蔽寄存器 IMR Interrupt Mask Register 功能: 用于屏蔽某IR0~IR7引脚上的中断请求信号,使之不能被传递给CPU。

某位为1,则屏蔽对应引脚上的中断请求;为0,允许。 IMR与IRR的各个位一一对应

例:IR0,IR3,IR7引脚上有中断请求信号,要求只屏蔽IR7引脚上的中断请求,则对屏蔽寄 存器送入屏蔽字10000000即可

IR2 IR1 IR0引脚

IRR7

IRR2

1 0

IRR0

IRR IMR

1

10

ISR

第二个中断响应信号,启动8259把选中的中断源的中断类型号 回送给CPU

*4 优先级分析器 PR Priority Resolver 功能:用于分析中断请求寄存器IRR中各位的优先级,对各个中断请求择优。 *择优对象:没有被屏蔽的IRi *择优时间:接收到第一个INTA信号时 *择优方式:由编程决定 *择优结果:找出优先级最高的中断源,送出中断类型号给CPU,并且使ISRi对应的位置1。 *5 逻辑控制 根据CPU对8259A设定的方式,产生8259A内部所需的控制信号,并且能够 发出INT信号和接收INTA信号。 *6 读写逻辑 *7 数据总线缓冲器:通过这一环节,可以使8259A的数据线直接与CPU的DB连接而不用增加 其它电路。 *8 级联缓存器/比较器(了解) 在多片8259A级联的情况下,用于存放和比较从8259A的级联选择代码。CPU响应中断 时,通过CS2~CS0对从8259A输出级联选择代码,选出发中断请求的从8259A;从8259A则通 过CS2~CS0接受来自主8259A的选择代码。 *9 初始化命令寄存器和操作字命令寄存器 两组可编程控制寄存器,用于设定或改变8259A的工作方式和控制方式。

8259A中断控制器实现

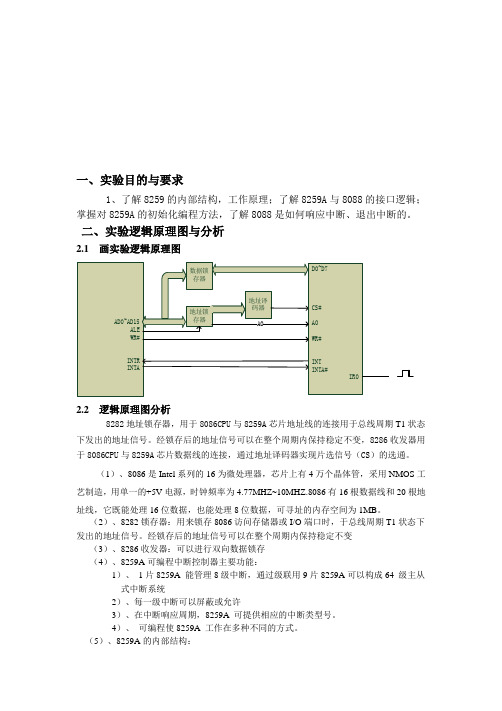

一、实验目的与要求1、了解8259的内部结构,工作原理;了解8259A 与8088的接口逻辑;掌握对8259A 的初始化编程方法,了解8088是如何响应中断、退出中断的。

二、实验逻辑原理图与分析 2.1 画实验逻辑原理图AD0~AD15ALEWR#INTR INTA数据锁存器地址锁存器地址译码器D0~D7CS#A0WR#INT INTA#IR0A02.2 逻辑原理图分析8282地址锁存器,用于8086CPU 与8259A 芯片地址线的连接用于总线周期T1状态下发出的地址信号。

经锁存后的地址信号可以在整个周期内保持稳定不变,8286收发器用于8086CPU 与8259A 芯片数据线的连接,通过地址译码器实现片选信号(CS )的选通。

(1)、8086是Intel 系列的16为微处理器,芯片上有4万个晶体管,采用NMOS 工艺制造,用单一的+5V 电源,时钟频率为4.77MHZ~10MHZ.8086有16根数据线和20根地址线,它既能处理16位数据,也能处理8位数据,可寻址的内存空间为1MB 。

(2)、8282锁存器:用来锁存8086访问存储器或I/O 端口时,于总线周期T1状态下发出的地址信号。

经锁存后的地址信号可以在整个周期内保持稳定不变 (3)、8286收发器:可以进行双向数据锁存 (4)、8259A 可编程中断控制器主要功能:1)、 1片8259A 能管理8级中断,通过级联用9片8259A 可以构成64 级主从 式中断系统2)、每一级中断可以屏蔽或允许3)、在中断响应周期,8259A 可提供相应的中断类型号。

4)、 可编程使8259A 工作在多种不同的方式。

(5)、8259A 的内部结构:1)、IRR:当IR0-IR7某一个引脚上出现有效中断请求时,IRR对应位被置12)、IMR:当IR0-IR7中需要屏蔽的,IMR对应位置13)、ISR:是一个8位寄存器,通过8位二进制数的值纪录当前正在处理的中断请求。

微机第九章8259

8259A的内部结构框图

(P 226 图9-1)

IRR(中断请求寄存器): 存放外部输入的中断请求信 号,IRi=1时,该寄存器的相应位置1;

ISR(中断服务寄存器): 记录正在处理中的中断请求;

IMR(中断屏蔽寄存器): 存放对各级中断请求的屏蔽信息 (由OCW1写入);

PR(优先级判别器): 用来识别各中断请求信号的优先级 别; 一般处理原则:允许高级打断低级,不允许低级打断高级, 也不允许同级中断互相打断. (注)

电平触发方式:高电平有效,但持续时间不能太长也不 能太短; 边沿触发方式:低电平到高电平的正跳变,最好用负脉 冲的后沿;

2.中断类型码的形成

在响应中断的第二个INTA信号有效期间8259A将中断类 型码通过数据总线传送给CPU。(P82)

初始化时设置

1 0 0 0 1 X X X D7 D6 D5 D4 D3 X X X

中断嵌套可以有多级,具体级数原则上不限, 只取决于堆栈深度。

三. 中断的优先级与中断嵌套

原主程序

1#中断 服务程序

2#中断 服务程序

3#中断 服务程序

响应

响应

响应

1#中断请求

2#中断请求 3#中断请求 返回 返回 返回

中断优先级3#>2#>1#

9.1 可编程中断控制器8259A

中断系统的功能:

1. 可解决高速运算CPU与低速外设信息交换之间的矛盾; 2. 用于响应突发事件;

(II)

郝新红

3#教学楼 102室,电话:4850

微机原理(II)

教材:“《微型计算机原理及应用》(第三版)郑学坚 周斌 编著” 清华大学出版社的后半部分 参考书: (1)《单片机原理与应用设计》张毅刚 、彭喜元 编著 电子工业出版社 2008.4

总结介绍8259中断控制器

8259中断控制器Overview前言8259A芯片是一个中断管理芯片,中断的来源除了来自于硬件自身的NMI中和来自于软件的INT n指令造成的软件中断之外,还有来自于外部硬件设备的中断,这些中断的可屏蔽的。

这些中断也都通过PIC(Programmable Interrupt Controller)进行控制,并传递给CPU。

一个8259A芯片最多可接收8个中断源,但由于可以将2个或多个8259A芯片进行级连(cascade),并且最多可以级链到9个,所以最多可以接64个中断源。

如今绝大多数的PC 都拥有2个8259A,这样最多可以接收15个中断源。

通过8259A可以对单个中断源进行屏蔽。

在一个8259A芯片上有如下几个内部的寄存器:1.Interrupt Mask Register(IMR)。

2.Interrupt Request Register(IRR)。

3.In Service Register(ISR)。

IMR被用作过滤被屏蔽的中断,IRR被用作暂时放置未被进一步处理的Interrupt,当一个Interrupt正在被CPU处理时,此中断被放置在ISR中。

除了这几个寄存器之外,8259A还有一个单元叫做Priority Resolver,当多个中断同时发生时,Priority Resolver根据它们的优先级,将最高优先级的优先传递给CPU。

工作原理当一个中断请求从IR0到IR7中的某根线到达IMR时,IMR首先判断IR是否被屏蔽,如果被屏蔽,则此中断请求被丢弃;否则,则将放入IRR中。

在此中断请求不能进行下一步处理之前,它一直被放置在IRR中。

一旦发现处理中断的时机已到,Priority Resolver将从所有被放置于IRR中的中断中挑选出一个优先级最高的中断,将其传递给CPU去处理。

IR号越低的中断优先级级别越高,比如IR0的优先级是最高的。

8259A通过发送一个INTR(Interrupt Request)信号给CPU,通知CPU有一个中断到达。

8259A介绍

(5)控制逻辑电路 控制逻辑电路根据CPU对8259A编程设定的工作方 式 管 理 8259A , 负 责 发 出 INTR 和 接 收 INTA# , 并 使 INTA#转化为内部所需的各种控制信号。 (6)读/写电路 读/写电路可接收CPU对8259A的初始化命令字ICW 和操作命令字OCW,并将其存入相应的端口寄存器, 来规定8259A的工作方式和控制模式;也可以向CPU提 供各端口寄存器的内容。 (7)数据总线缓冲器 连 接 系 统 总 线 和 8259A 的 内 部 总 线 , 用 于 传 输 8259A的控制字或状态字,以及中断类型号。 (8)级连缓冲/比较器 控制多片8259A的级连,扩展中断级。多片8259A 级连时,一片为主,其余为从。最多可9片级连,扩 展64级中断。

1.中断嵌套方式

(2)特殊全嵌套方式 和一般全嵌套方式基本相同,区别在于: 在特殊全嵌套方式下,处理某一中断时, 可实现对同级中断请求的响应。 系统中只有单片8259A时,通常用全嵌 套方式;而当8259A多片级连时,主片 必须采用特殊全嵌套方式,从片可采用 一般全嵌套方式。

一般全嵌套方式与特殊全嵌套方式的区别

8259A中断优先权的管理方式有固定优先权方式和自 动循环优先权方式两种。 (1)固定优先权方式 注: 特殊全嵌套仅用于多个8259A级连时的 在固定优先权方式中,IR7~IR0的中断优先权 主 8259A , 而 不 能 用 于 从 属 8259A 或 单 的级别是由系统确定的。 8259A系统。 它 们 由 高 到 低 的 优 先 级 顺 序 是 : IR0, IR1, IR2, …, IR7, 其中,IR0的优先级最高,IR7的优 先级最低。当有多个IRi请求时,优先权判决器(PR) 将它们与当前正在处理的中断源的优先权进行比较, 选出当前优先权最高的IRi,向CPU发出中断请求INT, 请求为其服务。

说明8259a中断控制器中的irr、isr和imr三个寄存器的功能

说明8259a中断控制器中的irr、isr和imr三个寄存器的功能8259A中断控制器是一种常用的外部设备,用于管理和分发系统中的中断请求。

它有三个重要的寄存器:IRR(中断请求寄存器)、ISR (中断服务寄存器)和IMR(中断屏蔽寄存器),这些寄存器在控制和处理中断时起到关键作用。

IRR寄存器(Interrupt Request Register)用于存储当前发生的中断请求。

每个位都对应一个中断源,当某个外部设备发出中断请求时,对应位会被置为1。

CPU可以通过读取IRR寄存器来检测当前的中断请求状态,以确定哪个中断源需要被处理。

ISR寄存器(Interrupt Service Register)用于记录正在被CPU处理的中断源。

当中断请求被CPU接受后,对应的中断源的位会被置为1,表示该中断正在被处理。

ISR寄存器的内容可以帮助CPU追踪当前正在处理的中断,以避免同时处理多个中断源。

IMR寄存器(Interrupt Mask Register)用于屏蔽中断请求。

每个位对应一个中断源,当对应位被置为1时,表示该中断源被屏蔽,即中断请求不会被接受。

通过设置IMR寄存器,CPU可以选择性地屏蔽或允许特定的中断源。

通过IRR、ISR和IMR这三个寄存器的配合使用,8259A中断控制器可以有效地管理和分发系统中的中断请求。

CPU可以通过读取IRR寄存器来检测中断请求,并根据IMR寄存器的设置来确定是否屏蔽某个中断源。

当CPU接受一个中断请求后,会将对应的中断源的位设置为1,并在ISR寄存器中记录下来,以便追踪和处理当前的中断。

当中断处理完成后,CPU会清除ISR寄存器中的相应位,表示中断已经处理完毕。

通过使用这些寄存器,8259A中断控制器可以实现多个中断源的优先级管理、中断请求的屏蔽和中断处理的跟踪。

这些功能对于保证系统可靠性和提高系统的响应能力非常重要。

8259A介绍

特殊屏蔽方式允许低优先 级中断请求中断正在服务 在有些场合中,希望一个中断服务程序能动态地改变系 的高优先级中断。

6.5.4 8259A工作过程

8259A进入工作状态的先决条件是必须按要求对其初始

化,使其处于准备就绪状态。当完成初始化后,8259A便 处于就绪状态,随时可接收外部的中断请求信号。 8259A对外部中断请求的响应和处理过程如下: (1) 当中断请求输入线IRQ0~IRQ7中有一条或多条变高 时,则中断请求寄存器IRR的相应位置“1”。 (2) 未被屏蔽的中断请求信号进入优先权判别器,优先级判 定电路选出优先级最高的中断请求,控制电路由INT引脚

(2)自动循环优先权方式

在自动循环优先权方式中,IR7~IR0优先权级别是可以 改变的。 其变化规律是:当某一个中断请求IRi服务结束后,该中 断的优先权自动降为最低,而紧跟其后的中断请求IR(i+1) 的优先权自动升为最高,IR7~IR0优先权级别按如下所示的 右循环方式改变。

假设在初始状态IR0有请求,CPU为其服务完毕,IR0优先权 自动降为最低,排在IR7之后,而其后的IR1的优先权升为最高, 其余依次类推。这种优先权管理方式,可以使8个中断请求都拥 有享受同等优先服务的权利。

初始最低优先级,由用户通过置位优先权命令

指定。

因不保留当前正在服务 3.中断结束方式

的中断的状态,所以不 当某一IRi中断被服务时,ISR中的相应位ISRi=1。 能用于中断嵌套方式。

当服务结束后,则必须清零该ISRi位。 (1)自动中断结束方式AEOI 此方式只适用于单片8259A系统中,且多个中断不会 嵌套。系统进入中断响应后,8259A在接收到CPU发来 的第二个INTA的信号时自动将ISR中的对应位清0。 (2)非自动中断结束方式EOI

第9章_1_1中断控制向量、DMA控制器

5. 中断服务寄存器 中断服务寄存器ISR 这是一个8位寄存器 位寄存器, 这是一个 位寄存器,用来记录正在处理中的中断请 当任何一级中断被响应, 求。当任何一级中断被响应,CPU正在执行它的中 正在执行它的中 断服务程序时, 寄存器中相应位置“ , 断服务程序时,ISR寄存器中相应位置“1”,一直 寄存器中相应位置 保持到该级中断处理过程结束为止。 保持到该级中断处理过程结束为止。多重中断情况 ISR寄存器中可有多位被同时置 1”。 寄存器中可有多位被同时置“ 下,ISR寄存器中可有多位被同时置“1”。 6. 中断屏蔽寄存器 中断屏蔽寄存器IMR 这是一个8位寄存器 位寄存器, 这是一个 位寄存器,用来存放对各级中断请求的屏 蔽信息。当该寄存器中某一位置“ 时 蔽信息。当该寄存器中某一位置“1”时,表示禁止 这一级中断请求进入系统,通过IMR寄存器可实现 这一级中断请求进入系统,通过 寄存器可实现 对各级中断的有选择的屏蔽。 对各级中断的有选择的屏蔽。

图9.19

图9.20

1. 数据总线缓冲存储器 这是8253与CPU之间的数据接口,它由 位双向三态 之间的数据接口, 这是 与 之间的数据接口 它由8位双向三态 缓冲存储器构成, 缓冲存储器构成,是CPU与8253之间交换信息的必 与 之间交换信息的必 经之路。 经之路。 2. 读/写控制电路 写控制电路 接收CPU送入的读 写控制信号,并完成对芯片内部 送入的读/写控制信号 接收 送入的读 写控制信号, 各功能部件的控制功能,因此,它实际上是8253芯 各功能部件的控制功能,因此,它实际上是 芯 片内部的控制器。可接收的控制信号如下: 片内部的控制器。可接收的控制信号如下: (1) A1A0——端口选择信号,由CPU输入。8253内部 端口选择信号, 输入。 端口选择信号 输入 内部 个独立的通道和一个控制字寄存器, 有3个独立的通道和一个控制字寄存器,它们构成 个独立的通道和一个控制字寄存器 8253芯片的 个端口,CPU可对 个通道进行读 写 芯片的4个端口 可对3个通道进行读 芯片的 个端口, 可对 个通道进行读/写 操作,对控制字寄存器进行写操作。 操作,对控制字寄存器进行写操作。这4个端口地 个端口地 址由最低2位地址码 位地址码A 来选择。 址由最低 位地址码 1A0来选择。