74LS系列集成电路引脚图

十进制可逆计数器74LS192引脚图管脚及功能表

十进制可逆计数器74LS192引脚图管脚及功

能表

2011年05月19日11:22 本站整理作者:本站用户评论(0)

关键字:

十进制可逆计数器74LS192引脚图管脚及功能表

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

图5-4 74LS192的引脚排列及逻辑符号

(a)引脚排列(b) 逻辑符号

图中:为置数端,为加计数端,为减计数端,为非同步进位输出端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:

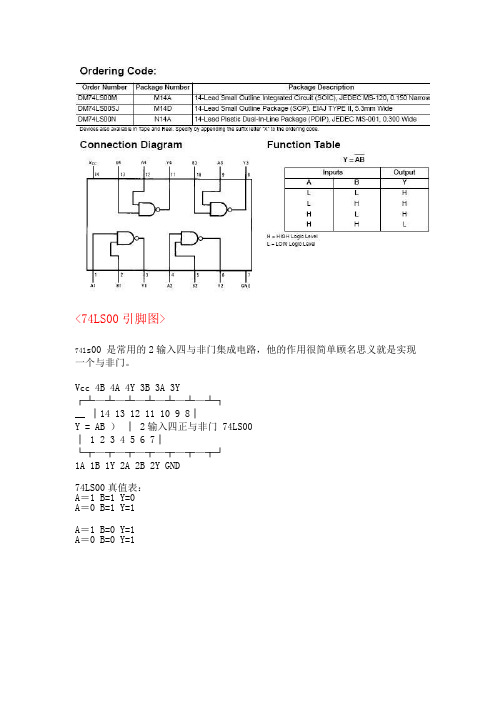

74ls00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y

┌┴—┴—┴—┴—┴—┴—┴┐

__ │14 13 12 11 10 9 8│

Y = AB )│ 2输入四正与非门 74LS00

│ 1 2 3 4 5 6 7│

└┬—┬—┬—┬—┬—┬—┬┘

1A 1B 1Y 2A 2B 2Y GND

<74LS00引脚图>

74LS00真值表:

A=1 B=1 Y=0

A=0 B=1 Y=1

A=1 B=0 Y=1

A=0 B=0 Y=1

表5-2 74LS192的功能表

[图]74LS20管脚图74LS27管脚图

74LS20管脚图74LS27管脚图

(5) 74LS20四输入双与非门,管脚图如附图1-31所示。

(6) 74LS27三输入三或非门,管脚图如附图1-32所示。

数字电路实验报告

数字电路实验报告姓名:张珂班级:10级8班学号:2010302540224实验一:组合逻辑电路分析一.实验用集成电路引脚图1.74LS00集成电路2.74LS20集成电路二、实验内容1、组合逻辑电路分析逻辑原理图如下:U1A 74LS00NU2B74LS00NU3C74LS00N X12.5 VJ1Key = Space J2Key = Space J3Key = Space J4Key = SpaceVCC5VGND图1.1组合逻辑电路分析电路图说明:ABCD 按逻辑开关“1”表示高电平,“0”表示低电平; 逻辑指示灯:灯亮表示“1”,灯不亮表示“0”。

真值表如下: A B C D Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1表1.1 组合逻辑电路分析真值表实验分析:由实验逻辑电路图可知:输出X1=AB CD =AB+CD ,同样,由真值表也能推出此方程,说明此逻辑电路具有与或功能。

2、密码锁问题:密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开;否则,报警信号为“1”,则接通警铃。

试分析下图中密码锁的密码ABCD 是什么? 密码锁逻辑原理图如下:U1A74LS00NU2B74LS00NU3C 74LS00NU4D 74LS00NU5D 74LS00NU6A74LS00N U7A74LS00NU8A74LS20D GNDVCC5VJ1Key = SpaceJ2Key = SpaceJ3Key = SpaceJ4Key = SpaceVCC5VX12.5 VX22.5 V图 2 密码锁电路分析实验真值表记录如下:实验真值表 A B CD X1 X2 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 0 1 1 0 1 1 0 1 1 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 0 1 1 11 10 1表1.2 密码锁电路分析真值表实验分析:由真值表(表1.2)可知:当ABCD 为1001时,灯X1亮,灯X2灭;其他情况下,灯X1灭,灯X2亮。

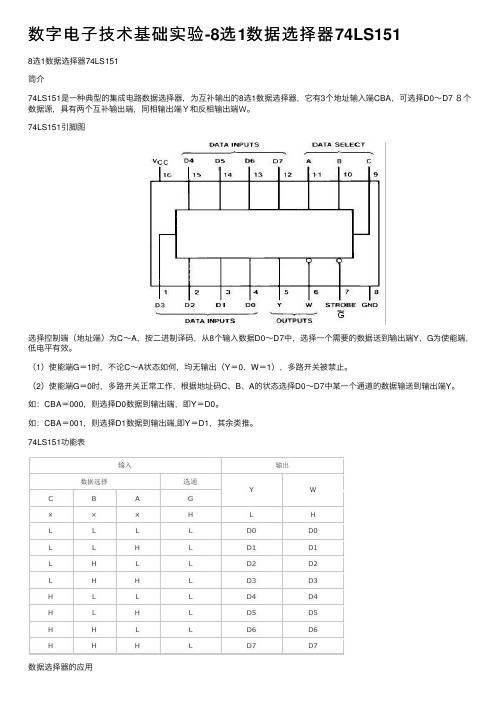

数字电子技术基础实验-8选1数据选择器74LS151

数字电⼦技术基础实验-8选1数据选择器74LS1518选1数据选择器74LS151简介74LS151是⼀种典型的集成电路数据选择器,为互补输出的8选1数据选择器,它有3个地址输⼊端CBA,可选择D0~D7 8个数据源,具有两个互补输出端,同相输出端Y和反相输出端W。

74LS151引脚图选择控制端(地址端)为C~A,按⼆进制译码,从8个输⼊数据D0~D7中,选择⼀个需要的数据送到输出端Y,G为使能端,低电平有效。

(1)使能端G=1时,不论C~A状态如何,均⽆输出(Y=0,W=1),多路开关被禁⽌。

(2)使能端G=0时,多路开关正常⼯作,根据地址码C、B、A的状态选择D0~D7中某⼀个通道的数据输送到输出端Y。

如:CBA=000,则选择D0数据到输出端,即Y=D0。

如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。

74LS151功能表数据选择器的应⽤数据选择器除实现有选择的传送数据外,还有其他⽤途,下⾯介绍⼏种典型应⽤。

(1)逻辑函数产⽣器从74LS151的逻辑图可以看出,当使能端G=0时,Y是C、B、A和输⼊数据D0~D7的与或函数。

式中mi是C、B、A构成的最⼩项。

显然。

当Di=1时,其对应的最⼩项mi在与或表达式中出现,当Di=0时,对应的最⼩项就不出现。

利⽤这⼀点,不难实现组合逻辑函数。

已知逻辑函数,利⽤数据选择器构成函数产⽣器的过程是,将函数变换成最⼩项表达式,根据最⼩项表达式确定各数据输⼊端的⼆元常量。

将数据选择器的地址信号C、B、A作为函数的输⼊变量,数据输⼊D0~D7,作为控制信号,控制各最⼩项在输出逻辑函数中是否出现,使能端G始终保持低电平,这样8选1数据选择器就成为⼀个3变量的函数产⽣器。

例1 试⽤8选1数据选择器74LS151产⽣逻辑函数解:把式变换成最⼩项表达式:显然D3、D5、D6、D7,都应该等于1,⽽式中没有出现的最⼩项m0,m1,m2,m4的控制变量D0、D1、D2、D4都应该等于0,由此可画出该逻辑函数产⽣器的逻辑图:、例2 试⽤与上例相同的8选1数据选择器产⽣从表中可以看出,凡使L值为1的那些最⼩项,其控制变量应该等于1,即D1、D2、D4、D7等于1(对应XYZ:001、010、100、111),其他控制变量均等于0。

电子技术 集成计数器74LS160

目录一参考资料························( 2 )二工作原理························( 7 )三引脚图························( 8 )四电路图························( 9 )一参考资料(一)74LS4874LS48的管脚排列如图(c)所示。

其真值表如表3所示。

该器件输入信号为BCD码,输出端为a、b、c、d、e、f、g共7线,另有3条控制线LE、RBI、BI/RBO。

LE端为测试端。

在BI端接高电平的条件下,当LE=0时,无论输入端A、B、C、D为何值,a~g输出全为高电平,使7段显示器件显示“8”字型,此功能用于测试器件。

RBI端为灭零输入端。

在LE=1,BI =1条件下,当输入A、B、C、D=0000时,输出a~g全为低电平,可使共阴LED显示器熄灭。

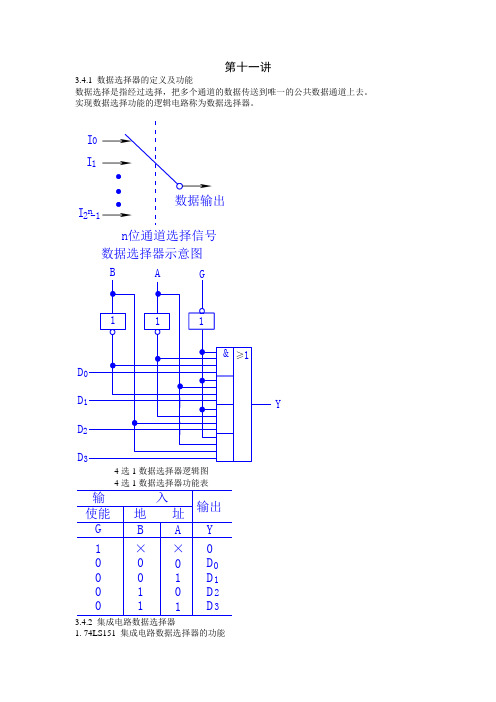

第十一讲74ls151

第十一讲3.4.1 数据选择器的定义及功能数据选择是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去。

实现数据选择功能的逻辑电路称为数据选择器。

4选1数据选择器逻辑图 4选1数据选择器功能表3.4.2 集成电路数据选择器1. 74LS151 集成电路数据选择器的功能→→→数据输出n位通道选择信号I I I 012n -1数据选择器示意图YBD D D D 输 入输出使能地 址G B A Y 100001100××01010D D D D 0123输出Y 的表达式为:74LS151的引脚图由1位数据选择器并联可组成多位数据选择器,2位8选1数据选择器的连接方法如图.输 入输 出选 择C B A 使 能G Y WH L L L L L L L L × × × L L L L L H L H L L H H H L L H L H H H L H H HL H D D D D D D D D D D D D D D D D 0122334455667710Y = m D i ii=0712345678910111213141516GND V CC 74LS151012345674LS151引脚图A B CD D D D D D D D Y W G 7可以把数据选择器的使能端作为地址选择输入,将两片74LS151连接成一个16选1的数据选择器,连接方法如图。

EN C A2.数据选择的应用 (1)逻辑函数产生器当使能端G=0时,Y 是C 、B 、A 和输入数据D0 -D7 的与或函数。

当D =1时,其对应的最小项m 在与或表达式中出现,否则,就不出现。

例: 试用8选1数据选择器74LS151产生逻辑函数。

D C B AYYY = m D i ii=07L=XYZ+XYZ+XY 原式=XYZ+XYZ+XYZ+XYZ=D m +D m +D m +D m 33556677D D D D 3567,都应该等于1,其它的D等于0。

74LS系列主要芯片引脚及参数

<74LS00引脚图>74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。

<74ls138功能表>74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

74ls192芯片

74ls192芯片74LS192是一种技术较老的逻辑门集成电路(IC),它是一种同步可编程计数器。

该芯片可以实现四位二进制计数,并且可以通过外部的控制信号来实现不同的计数模式和功能。

74LS192具有带锁存功能的四位二进制计数器。

它包含四个独立的计数器,每个计数器都可以通过控制端进行控制。

此外,它还有一个可编程的控制端,可以用来选择计数方向(向上计数或向下计数)以及计数模式(十进制模式、二进制模式等)。

该芯片的引脚图和引脚功能如下:1. CP0 - 输入引脚,用于时钟脉冲的输入。

2. CP1 - 输入引脚,用于时钟脉冲的输入。

3. MR - 输入引脚,用于复位计数器。

4. PC0 - 输入引脚,用于选择计数模式。

5. PC1 - 输入引脚,用于选择计数模式。

6. U/D - 输入引脚,用于选择计数方向。

7. A - 输出引脚,用于输出二进制位的最低位。

8. B - 输出引脚,用于输出二进制位的次低位。

9. C - 输出引脚,用于输出二进制位的次高位。

10. D - 输出引脚,用于输出二进制位的最高位。

11. QA - 输出引脚,用于输出BCD码的最低位。

12. QB - 输出引脚,用于输出BCD码的次低位。

13. QC - 输出引脚,用于输出BCD码的次高位。

14. QD - 输出引脚,用于输出BCD码的最高位。

15. Vcc - 正电源引脚。

16. GND - 接地引脚。

74LS192的工作原理如下:首先,需要将MR引脚置低,从而使计数器复位。

然后,通过CP0和CP1引脚输入时钟信号,控制计数器的计数速度。

U/D引脚用于选择计数方向,当U/D引脚为低电平时,计数器向上计数,当U/D引脚为高电平时,计数器向下计数。

PC0和PC1引脚用于选择计数模式。

当PC1引脚为低电平,PC0引脚为高电平时,计数器工作在二进制模式下。

当PC1引脚为高电平,PC0引脚为低电平时,计数器工作在十进制模式下。

其它的PC1和PC0的组合可以实现更多的计数模式。

74系列芯片引脚图

类别 电路简称 四位比较器 74LS85

A3 B3

数据输入 A2 B2 A1 B1

真值表 A0 B0

级联输入

输出

A>B A<B A=B A>B A<B A=B

A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3

GND 8

7744LLSS17124

16 Vcc 15 1CLR 14 2CLR 13 2CK 12 2K 11 2J 10 2PR 9 2Q

(a) JK 触发器 74112 引脚图

Y0 1

Y1 2

Y2 3 Y3 4 Y4 5 Y5 6 Y6 7 GND 8

7474LLSS7442

16 Vcc

15 A0 14 A1

13 A2 12 A3 11 Y9 10 Y8 9 Y7

图 3.2 74LS42 引脚图

74LS04

B1

C2

LT 3 BI/RBO 4

RBI 5 D6 A7

GND 8

747L4LSS7448

16 Vcc 15 f 14 g

13 a 12 b 11 c 10 d 9e

图 3.3 74LS48 引脚图

常用 74 系列 TTL 集成电路

真值表

时钟 CP J K

X

XX

X

XX

↓

00

↓

10

↓

01

↓

11

输出 清零(Q=0) 置 1(Q=1) 保持(Q=Qn)

Q=1 Q=0 翻转(Q=/Q)

电路引脚图

类别

电路简 称

74LS90引脚功能及真值表

74LS90引脚功能及真值表74LS90是一种常用于数字电路设计的集成电路,它被广泛应用于计数器和分频器等电路中。

在理解74LS90的使用方法之前,我们需要了解其引脚功能及对应的真值表。

74LS90引脚功能:引脚功能是指不同引脚在电路中所承担的具体功能和作用。

以下是74LS90的引脚功能及简要描述:引脚1(CPD):低电平置位,用于清零计数器。

引脚2(MR):同步清零或允许计数。

引脚3(CP0):第一个计数输入端。

引脚4(CP1):第二个计数输入端。

引脚5(CP2):第三个计数输入端。

引脚6(CP3):第四个计数输入端。

引脚7(QA):第一个输出位。

引脚8(QB):第二个输出位。

引脚9(QC):第三个输出位。

引脚10(QD):第四个输出位。

引脚11(GND):地线连接。

引脚12(VCC):电源连接。

真值表:真值表用于描述不同输入对应的输出结果。

在74LS90中,引脚3(CP0)、引脚4(CP1)、引脚5(CP2)和引脚6(CP3)作为计数输入端,通过输入不同的电平来实现计数功能。

以下是74LS90的真值表示例:| CP3 | CP2 | CP1 | CP0 | QA | QB | QC | QD ||-----|-----|-----|-----|----|----|----|----|| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 || 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 || 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 || 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 || 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 || 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 || 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 || 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 || 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 || 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 || 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 || 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | | 1 | 1 |。

74LS系列IC管脚图大全

74LS390 双十进制计数器

74LS624 压控振荡器

74LS625 压控振荡器

74LS626 压控振荡器

74LS627 压控振荡器

74LS628 压控振荡器

74LS629 压控振荡器

两片74LS283构成的8位加法器

74LS289 64位随机存取存储器

74LS289 64位随机存取存储器

74LS290异步2—5—10进制计数器

74LS290异步2—5—10进制计数器

74LS292 可编程分频器/数字定时器

74LS293 4位二进制计数器

74LS294 16位可编程模块

74LS374 八D触发器(三态同相)

74381

符号

A0 A1 A2 A3

B0 B1 B2 B3

C -1

S0 S1 S2

引脚排列

A 1 1 20 VCC

F0

B1

A2

F1

A0

B2

F2

B0

F3

S0

A3 B3

7 43 81

S1

C -1

S2

P

P

F0

G

G

F1

F3

GND 1 0 1 1 F 2

74LS381算术逻辑单元

74LS181 算术逻辑单元/功能发生器

74LS181 四位算术逻辑运算器

7 4 18 2

G 1 1 16 V cc

P1

P2

G0

G2

P0

C -1

G3

C0

P3

C1

P

G

G ND 8 9 C 2

74LS182先行进位发生器/超前进位产生器

VCC 2Ai 2Bi 2Ci-1 2Ci 2Si VCC2A 2B 2CIn 2COn+1 2F 74LS183 1COn+1 1A 1B 1CIn 1F GND 1Ai 1Bi 1Ci-1 1Ci 1Si 地