systemverilog标准手册

systemverilog 可综合 语法

systemverilog 可综合语法-概述说明以及解释1.引言1.1 概述SystemVerilog是一种硬件描述语言,其可综合语法用于描述硬件设计的行为和结构。

可综合语法是指在编写SystemVerilog代码时,能够被综合工具翻译成底层硬件电路,并最终映射到FPGA或ASIC等可编程器件上的语法规则和风格。

因此,可综合语法在硬件设计中起着至关重要的作用。

在硬件设计中,可综合语法使设计工程师能够通过代码描述硬件的功能和结构,包括处理器、逻辑电路、存储器等。

通过使用可综合语法,设计工程师可以更加灵活地实现各种功能和性能要求,同时也能提高设计的可维护性和可重用性。

SystemVerilog的可综合语法特点是其结构化的设计风格,丰富的数据类型和内置的高级语言功能。

与传统的硬件描述语言相比,SystemVerilog提供了更多的抽象层次和编程特性,可以更高效地完成复杂的硬件设计任务。

例如,SystemVerilog支持面向对象的设计方法,可以使用类和对象对设计进行建模和封装。

此外,SystemVerilog还提供了多种数据类型和运算符,使设计工程师可以更方便地处理各种数据和信号。

综上所述,可综合语法在SystemVerilog中具有重要的地位和作用。

通过使用可综合语法,设计工程师能够更加方便地描述和实现各种硬件功能,提高设计的效率和可靠性。

在今后的硬件设计中,可综合语法的应用将更加广泛,并且不断发展和完善,以满足不断变化的设计需求。

1.2 文章结构文章结构部分的内容可以包括以下内容:文章结构的目的是为了给读者提供清晰的导航和理解文章的逻辑框架。

通过合理的结构,读者可以更好地理解文章的目的和内容,并能够有序地阅读和理解整个文档。

本文的结构如下:第一部分是引言部分,用于介绍文章的背景和相关信息。

在引言部分,我们将概述SystemVerilog可综合语法的定义和作用,并介绍本文的结构和目的。

第二部分是正文部分,主要内容是关于SystemVerilog可综合语法的定义和特点。

Verilog硬件描述语言参考手册

Verilog 语言标准化的目的是将现存的通过 Verilog-XL 仿真器体现的 Verilog 语言标准化。 IEEE 的 Verilog 标准与事实上的标准有一些区别。因此,仿真器有可能不完全支持以下的一 些功能:

y 在UDP(用户自定义原语)和模块实例中使用数组(见Instantiation说明)。

编译

Verilog的原代码通常键入到计算机的一个或多个文本文件上。然后把这些文本文件交给 Verilog编译器或解释器处理,编译器或解释器就会创建用于仿真和综合必需的数据文件。 有时候,编译完了马上就能进行仿真,没有必要创建中间数据文件。

-----------------------------------------------------------------------------

1

在Verilog HDL 中,我们可通过高层模块调用低层和基本元件模块,再通过线路连接(即下 文中的NET)把这些具体的模块连接在一起,来描述一个极其复杂的数字逻辑电路的结ห้องสมุดไป่ตู้。 所谓基本元件模块就是各种逻辑门和用户定义的原语模块(即下文中的UDPs)。而所谓NET 实质上就是表示电路连线或总线的网络。端口连接列表用来把外部NET连接到模块的端口(即 引脚)上。寄存器可以作为输入信号连接到某个具体模块的输入口。NET和寄存器的值可取 逻辑值0,1,x(不确定)和 z(高阻)。除了逻辑值外,NET还需要有一个强度(Strength) 值。在开关级模型中,当NET的驱动器不止一个时,还需要使用强度值来表示。逻辑电路的 行为可以用Initial和Always 的结构和连续赋值语句,并结合设计层次树上各种层次的模块 直到最底层的模块(即UDP及门)来描述。

system verilog 标准

系统Verilog是一种硬件描述语言(HDL),用于描述数字电路。

它包含了Verilog的所有特性,并添加了一些新的特性。

这些新的特性包括在设计中引入了数据类型的定义,更好地支持设计的抽象,以及更自然地支持设计的层次式描述。

在本文中,我们将深入了解System Verilog标准。

1. 介绍System Verilog标准System Verilog是IEEE标准1800,最初是由Accellera组织进行开发的。

它于2005年发行,是Verilog HDL的扩展,它添加了许多新的特性,使得它更适合于硬件验证和设计。

2. System Verilog的特性System Verilog添加了许多新的特性,以提高Verilog HDL的功能。

其中一些主要特性包括:a. 对象导向编程:System Verilog引入了面向对象的编程范式,使得设计和验证更加抽象和灵活。

b. 增强了数据类型和操作:System Verilog引入了更多的数据类型和操作,更好地支持设计和验证的需求。

c. 增加了随机性:System Verilog引入了随机性,使得验证更加全面和高效。

3. System Verilog在硬件验证中的应用System Verilog的特性使得它在硬件验证中应用广泛。

它提供了丰富的验证方法和工具,包括:a. 事务级建模(TLM):System Verilog提供了TLM的支持,使得验证更加抽象和高效。

b. Constrained随机验证:System Verilog引入了constrained random的验证方法,使得验证更加全面和高效。

c. Coverage驱动验证:System Verilog提供了coverage驱动的验证方法,使得验证更加全面和高效。

4. System Verilog在硬件设计中的应用除了在硬件验证中应用广泛外,System Verilog在硬件设计中也有着广泛的应用。

SystemVerilog语法

11 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types -

User defined types

User defined types are same as found in C language or others. A type can be used before it is defined, provided it is first identified as a type by an empty typedef. Syntax

– can be accessed as pack1.d <= ‘b0;

– the whole struct can be resetted with pack1 <= ‘b0;

• unpacked struct (no “packed” keyword) allow only acces through the named fields (pack1.d <=‘b0);

New features

C type data types like int, typedef, struct, union, enum. Dynamic data types : struct, classes, dynamic queues, dynamic arrays.

New operators and built in methods.

• equivalent to a packed array subdivided into named fields:

– example: 48 bit packed array – can be accessed as pack1[15:0] <= ‘b0; – can access pack1[9:4] <= 15;

SystemVerilog语言简介3

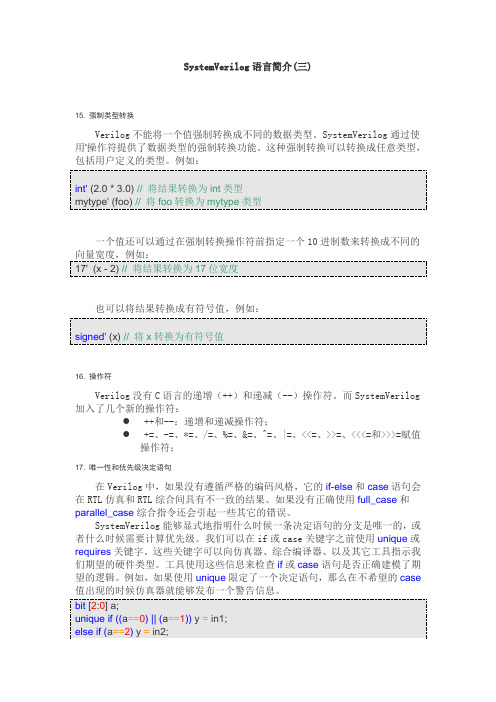

SystemVerilog语言简介(三)15. 强制类型转换Verilog不能将一个值强制转换成不同的数据类型。

SystemVerilog通过使用'操作符提供了数据类型的强制转换功能。

这种强制转换可以转换成任意类型,包括用户定义的类型。

例如:int' (2.0 * 3.0) // 将结果转换为int类型mytype' (foo) // 将foo转换为mytype类型一个值还可以通过在强制转换操作符前指定一个10进制数来转换成不同的向量宽度,例如:17'(x - 2) // 将结果转换为17位宽度也可以将结果转换成有符号值,例如:signed' (x) // 将x转换为有符号值16. 操作符Verilog没有C语言的递增(++)和递减(--)操作符。

而SystemVerilog 加入了几个新的操作符:●++和--:递增和递减操作符;●+=、-=、*=、/=、%=、&=、^=、|=、<<=、>>=、<<<=和>>>=赋值操作符;17. 唯一性和优先级决定语句在Verilog中,如果没有遵循严格的编码风格,它的if-else和case语句会在RTL仿真和RTL综合间具有不一致的结果。

如果没有正确使用full_case和parallel_case综合指令还会引起一些其它的错误。

SystemVerilog能够显式地指明什么时候一条决定语句的分支是唯一的,或者什么时候需要计算优先级。

我们可以在if或case关键字之前使用unique或requires关键字。

这些关键字可以向仿真器、综合编译器、以及其它工具指示我们期望的硬件类型。

工具使用这些信息来检查if或case语句是否正确建模了期望的逻辑。

例如,如果使用unique限定了一个决定语句,那么在不希望的case 值出现的时候仿真器就能够发布一个警告信息。

System Verilog Assertions应用指南,第八章

Isolating assertion errors early

Assertion based verification provides excellent potential for finding design bugs early in the verification cycle. The SVA language is defined to address ABV with powerful built-in constructs. Assertion failures are indicated to the user by default as required by the SystemVerilog 3.1a standard. It is not required to display the success of an assertion by default. The user can use the action block of an assertion to display successes. Since the number of successes can be numerous (since most assertions are evaluated on every clock edge), displaying every success by default can create huge log files depending on the number of assertions that are active during simulation, slowing down the simulation. A typical test configuration is shown in Figure 7-1. This is the same as Figure 0-2 shown in Chapter 0. Let's assume that a user executes this configuration and the simulation completes with a few assertion errors. The user should be absolutely confident that the error issued is a real design error. In other words, a user should be confident that his assertion code is correct and that the assertion failure is not a false condition. Debugging the entire design based on an assertion error is a tough task. If the error issued was due to bad assertion code, a user could waste a lot of time in the verification process. On the other hand, if there are no assertion failures during simulation, the verification engineer should be absolutely confident that the design works. If the assertion is not written accurately, it might not capture the intent of the design and hence, can miss a real error.

VMM for SystemVerilog中文版(前四章)

前言文章主要介绍《VMM for SystemVerilog》一书描述的如何利用SystemVerilog语言,采用验证方法学以及验证库开发出先进验证环境。

文章分为四部分,第一部分概述了用SystemVerilog语言验证复杂SoC的基本方法。

第二部分主要介绍使用先进验证技术进行RTL验证并定义一个能在项目之间进行验证单元重用的分层验证平台结构。

第三部分将涉及到系统级验证,包括SystemVerilog 与SystemC交互等方面。

当与一个合适方法相结合,SystemVerilog提供了建立一个完整RTL以及系统级(ESL)验证环境需要的所有结构及特性。

同时完全支持与System C或与一个以C为基础的软件测试环境交互。

第四部分讨论验证所采用的验证策略,VMM方法学,以及利用《VMM for SystemVerilog》中定义的标准库来支持方法学。

这些库涉及到文章中讨论的基本方法,XVC,XVC管理器,软件验证等方面。

采用《VMM for SystemVerilog》书中提供的方法学是应对目前复杂芯片而带来验证挑战的有用方法。

此书基于业界多年领先的Synopsys公司以及ARM公司专家,及其客户提供经验编写而成,因而对开发团队有益。

采用此方法学将提高验证效率,为一次投片成功提供更大可能。

此文章全面介绍关于用SystemVerilog验证复杂SoC。

更多书中信息可在中找到。

事实上业界已经认可VMM验证方法,此书日文版已经发行,与VMM相关书籍也已诞生,除Synopsys之外的几个EDA厂家也提供相关练习,甚至在California Extension Santa Cruz大学开展了VMM课程。

/提供了更多业界对VMM验证方法支持信息。

目录1 SystemVerilog验证方法学介绍 (4)1.1 验证面临挑战 (4)1.2 SystemVerilog验证技术 (4)1.3 产生带约束随机仿真 (4)1.4 覆盖率驱动验证 (5)1.5 断言 (6)1.6 小结 (8)2 SystemVerilog验证方法学:RTL (8)2.1 分层测试平台结构 (8)2.2 自顶向下和自底向上 (9)2.3 结果检查 (10)2.4 覆盖率驱动验证执行 (10)2.5 使用形式分析 (11)2.6 产生可重用验证IP (11)2.7 小结 (12)3 SystemVerilog验证方法学:ESL (12)3.1 系统级验证介绍 (12)3.2 可扩展的验证单元 (13)3.3 XVC管理器(XVC manager) (13)3.4 系统级验证环境 (14)3.5 事务级模型(Transaction-level models) (16)3.6 小结 (17)4 SystemVerilog验证方法学:采用VMM (17)4.1 采用验证方法学 (17)4.2 VMM提供四类库 (18)4.2.1 VMM标准库 (18)4.2.2 VMM Checker库 (19)4.2.3 XVC标准库 (20)4.2.4 软件测试架构 (21)4.3 小结 (21)结束语: (21)Figure 1 自动测试相对于直接测试有更高效率 (5)Figure 2 自动及人工验证技术运用在验证不同阶段 (6)Figure 3 断言是验证重要组成部分 (7)Figure 4 多层测试平台方便验证重用 (9)Figure 5 高层次测试平台单元更早验证事务级模型 (10)Figure 6 具有通用接口协议验证IP重用到新项目 (12)Figure 7 XVC结构分为两层:发生器和驱动器 (13)Figure 8 XVC 管理器控制并使测试平台中其他XVC协调工作 (14)Figure 9 系统确认环境必须高效度量系统执行 (16)Figure 10 vmm_env类定义一系列virtual methods用于执行测试用例 (18)Figure 11 VMM检查库扩展了OVL断言内容 (20)Figure 12 用XVC标准库和VMM标准库中类建立XVC (20)1 SystemVerilog验证方法学介绍芯片验证中虽然传统验证方法尽力保持技术更新步伐以适应设计尺寸以及复杂度的增加,但验证依然是当前SoC以及可重用IP模块设计中面临的最大挑战。

SystemVerilog 快速入门

SyestemVerilog的全面验证和设计

进行全面验证的环境 仿真 覆盖 断言 验证 形式化特性 测试平台 抓住设计意图

SystemVerilog

仿真检查 仿真检查

断言 自动测试平台

硬件辅助的验证 提高了验证的水平

硬件辅助验证 硬件辅助验证

与每个设计和 统一的断言扩展了验证方法的效率 验证工程师联 络

SystemVerilog 讲座

第一讲: SystemVerilog 基本知识

夏宇闻 神州龙芯集成电路设计公司 2008

Verilog HDL的发展历史

1984: Gateway Design Automation 推出 Verilog 初版 1989: Gateway 被Cadence Design Systems 公司收购 1990: Cadence 向业界公开 Verilog HDL 标准 1993: OVI 提升 the Verilog 标准,但没有被普遍接受 1995: IEEE 推出 Verilog HDL (IEEE 1364-1995)标准 2001: IEEE 推出 Verilog IEEE Std1364-2001 标准 2002: IEEE 推出 Verilog IEEE Std1364.1-2002 标准 2002: Accellera 对 SystemVerilog 3.0 进行标准化 – Accellera 是OVI & VHDL International (VI)合并后的 国际标准化组织 2003: Accellera 标准化后的SystemVerilog 3.1 2006: IEEE 推出带SystemVerilog 扩展的Verilog新标准

------------------------- SystemVerilog ------------------------------interfaces dynamic processes nested hierarchy 2-state modeling byte unrestricted ports packed arrays implicit port connections array assignments enhanced literals enhanced event control time values & units unique/priority case/if logic-specific processes root name space

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SystemVerilog标准手册

一、概述

SystemVerilog是一种硬件描述和验证语言,它结合了Verilog HDL

和VHDL的特性,并增添了许多新的功能和特性。

SystemVerilog的标准手册是SystemVerilog语言的权威参考资料,它详细说明了SystemVerilog的语法、语义和用法规范。

二、内容

1. 语言基础

SystemVerilog标准手册包含了SystemVerilog语言的基础知识,如数据类型、变量定义、控制结构、函数和任务等。

在这一部分,读者

可以了解到SystemVerilog的基本语法和语言特性,为后续的学习和应用打下坚实的基础。

2. 对象和类

SystemVerilog引入了面向对象的编程思想,允许用户定义自定义类型、类和对象。

SystemVerilog标准手册详细介绍了对象和类的定义、成员函数、继承和多态等相关内容,为用户提供了丰富的编程工具和

技巧。

3. 验证方法

SystemVerilog不仅可以用于硬件描述,还可以用于硬件验证。

SystemVerilog标准手册介绍了SystemVerilog的验证方法和工具,包括assertion、coverage、constrained randomization等内容,帮助用户编写高效且可靠的验证代码。

4. 高级特性

除了基本的语言特性外,SystemVerilog还提供了许多高级的功能和特性,如接口、多线程、并发控制等。

SystemVerilog标准手册深入介绍了这些高级特性的用法和原理,帮助用户更好地理解和应用SystemVerilog语言。

5. 应用实例

除了语法和特性的介绍外,SystemVerilog标准手册还提供了大量的实际应用示例,包括硬件描述、验证代码和仿真模型等。

这些应用实例可以帮助用户更直观地了解SystemVerilog语言的实际应用场景,加深对SystemVerilog的理解和掌握。

三、重要性

SystemVerilog标准手册是学习和使用SystemVerilog语言的重要参考资料。

它详细介绍了SystemVerilog语言的各个方面,为用户提供了全面、权威的学习和查询资源。

无论是初学者还是有经验的SystemVerilog用户,都可以从中受益匪浅。

四、结论

SystemVerilog标准手册是学习和应用SystemVerilog语言的不可或缺的权威指南,它详细介绍了SystemVerilog语言的各个方面,为用

户提供了全面、权威的学习和查询资源。

阅读和理解SystemVerilog

标准手册,将有助于用户更好地掌握和应用SystemVerilog语言,提

升硬件设计和验证的效率和质量。

SystemVerilog标准手册的深入研

究

SystemVerilog标准手册是学习和应用SystemVerilog语言的权威指南,它为用户提供了全面详尽的学习和查询资源。

在这个手册中,读

者可以深入了解SystemVerilog语言的各个方面,包括语言基础、对

象和类、验证方法、高级特性以及丰富的应用实例。

这些内容不仅可

以帮助初学者建立扎实的基础,还可以帮助有经验的用户深化对SystemVerilog语言的理解和掌握。

SystemVerilog标准手册详细介绍了SystemVerilog语言的基础知识,包括数据类型、变量定义、控制结构、函数和任务等。

通过学习这些

基础知识,用户可以对SystemVerilog语言有一个清晰的认识,为后续的学习和应用打下坚实的基础。

手册中还介绍了面向对象的编程思想,允许用户定义自定义类型、类和对象,为用户提供了丰富的编程

工具和技巧。

SystemVerilog标准手册介绍了SystemVerilog的验证方法和工具,包括assertion、coverage、constrained randomization等内容。

这些内容对于硬件验证非常重要,可以帮助用户编写高效且可靠的验

证代码,提升硬件设计和验证的效率和质量。

除了基本的语言特性和验证方法,SystemVerilog标准手册还深入介

绍了该语言的高级特性,如接口、多线程、并发控制等。

这些高级特

性在实际的硬件设计和验证中起着重要作用,了解和掌握这些高级特

性可以帮助用户更好地应用SystemVerilog语言,提升工作效率。

SystemVerilog标准手册提供了大量的实际应用示例,包括硬件描述、验证代码和仿真模型等。

这些实例可以帮助用户更直观地了解SystemVerilog语言的实际应用场景,加深对SystemVerilog的理解和掌握。

通过实际的应用示例,用户可以将理论知识转化为实际应用

能力,更好地应用SystemVerilog语言解决实际问题。

SystemVerilog标准手册是学习和应用SystemVerilog语言的不可或缺的权威指南。

通过阅读和理解这本手册,用户可以更好地掌握和应

用SystemVerilog语言,提升硬件设计和验证的效率和质量。

希望广大读者能够认真研读这本手册,不断提高自己的技术水平,为硬件设

计和验证领域的发展贡献自己的力量。