DRAM内存颗粒测试简介

DDR DDR2 DDR3简介

DDR \DDR2\DDR3简介DDR是一种继SDRAM后产生的内存技术,DDR,英文原意为“DoubleDataRate”,顾名思义,就是双数据传输模式。

之所以称其为“双”,也就意味着有“单”,我们日常所使用的SDR AM都是“单数据传输模式”,这种内存的特性是在一个内存时钟周期中,在一个方波上升沿时进行一次操作(读或写),而DDR则引用了一种新的设计,其在一个内存时钟周期中,在方波上升沿时进行一次操作,在方波的下降沿时也做一次操作,之所以在一个时钟周期中,DDR则可以完成SDRAM两个周期才能完成的任务,所以理论上同速率的DDR内存与SDR内存相比,性能要超出一倍,可以简单理解为100MHZ DDR=200MHZ SDR。

DDR内存不向后兼容SDRAMDDR内存采用184线结构,DDR内存不向后兼容SDRAM,要求专为DDR设计的主板与系统。

DDR-II内存将是现有DDR-I内存的换代产品,它们的工作时钟预计将为400MHz或更高(包括现代在内的多家内存商表示不会推出DDR-II 400的内存产品)。

从JEDEC组织者阐述的DDR-II标准来看,针对PC等市场的DDR-II内存将拥有400-、533、667MHz等不同的时钟频率。

高端的DDR-II内存将拥有800-、1000MHz两种频率。

DDR-II内存将采用200-、220-、240 -针脚的FBGA封装形式。

最初的DDR-II内存将采用0.13微米的生产工艺,内存颗粒的电压为1.8V,容量密度为512MB。

DDR-II将采用和DDR-I内存一样的指令,但是新技术将使D DR-II内存拥有4到8路脉冲的宽度。

DDR-II将融入CAS、OCD、ODT等新性能指标和中断指令。

DDR-II标准还提供了4位、8位512MB内存1KB的寻址设置,以及16位512MB内存2K B的寻址设置。

DDR-II内存标准还包括了4位预取数(pre-fetch of 4 bits)性能,DDR-I技术的预取数位只有2位。

RAM+Stress+Test(RST)内存测试软件说明

DDR测试软件简要说明书如以上的示范图:闪动的代表8颗粒的区域横着数0-7带表第一颗区域8-F代表第二颗区域,0-7带表第三颗区域,8-F代表第四颗区域依次带表8颗颗粒的内存条⒈DDR8位与16位的单面测法:注意:DDR的颗粒排列循序是1-2-3-4-5-6-7-8⑴.0-7(第1颗粒)区域如果出现乱码,代表这根DDR内存条的第一颗粒已经损坏⑵. 8-F(第2颗粒)区域如果出现乱码,代表这根DDR内存条的第二颗粒已经损坏⑶. 0-7(第3颗粒)区域如果出现乱码,代表这根DDR内存条的第三颗粒已经损坏⑷.8-F(第4颗粒)区域如果出现乱码,代表这根DDR内存条的第四颗粒已经损坏⑸. 0-7(第5颗粒)区域如果出现乱码,代表这根DDR内存条的第五颗粒已经损坏⑹. 8-F(第6颗粒)区域如果出现乱码,代表这根DDR内存条的第六颗粒已经损坏⑺. 0-7(第7颗粒)区域如果出现乱码,代表这根DDR内存条的第七颗粒已经损坏⑻. 8-F(第8颗粒)区域如果出现乱码,代表这根DDR内存条的第八颗粒已经损坏⒉如果你是128M的双面DDR内存,如以上显示界面图:1-16M ------------------------------------------------------------------------------------------------------------ 16-32M ------------------------------------------------------------------------------------------------------- 32-48M ------------------------------------------------------------------------------------------------------------48-64M------------------------------------------------------------------------------------------------------------- 从1M到64M的上面的4根虚线上出现乱码的话,代表这跟内存的的第一面的颗粒有问题(判断哪个颗粒的好坏按照以上的说明)64-80M ------------------------------------------------------------------------------------------------------------ 80-96M -------------------------------------------------------------------------------------------------------96-112M------------------------------------------------------------------------------------------------------------112-128M---------------------------------------------------------------------------------------------------------- 从64M到128M的上面的4根虚线上出现乱码的话,代表这跟内存的的第二面的颗粒有问题(判断哪个颗粒的好坏按照以上的说明)注意:在内存的PCB板上的两边标着1与92的代表第一面93与184的代表第二面,1-128M的8根虚线是用来区分两面区域的作用.⒊SD的8位与16位的单面测法:注意:SD的颗粒排列循序是8-4-7-3-6-2-5-1⑴.0-7(第1颗粒)区域如果出现乱码,代表这根DDR内存条的第8颗粒已经损坏⑵. 8-F(第2颗粒)区域如果出现乱码,代表这根DDR内存条的第4颗粒已经损坏⑶. 0-7(第3颗粒)区域如果出现乱码,代表这根DDR内存条的第7颗粒已经损坏⑷.8-F(第4颗粒)区域如果出现乱码,代表这根DDR内存条的第3颗粒已经损坏⑸. 0-7(第5颗粒)区域如果出现乱码,代表这根DDR内存条的第6颗粒已经损坏⑹. 8-F(第6颗粒)区域如果出现乱码,代表这根DDR内存条的第2颗粒已经损坏⑺. 0-7(第7颗粒)区域如果出现乱码,代表这根DDR内存条的第5颗粒已经损坏⑻. 8-F(第8颗粒)区域如果出现乱码,代表这根DDR内存条的第1颗粒已经损坏4.通过以上的说明SD的双面是跟DDR的是一样的但是颗粒的好坏判断要按照他们的排列循序来判断的.5.PCB板的短路或者虚焊的测法:在以8根虚线上都出现乱码代表这根内存的PCB板有问题.6.不点亮内存的测试方法:很多内存短路和颗粒损坏后都不能点亮,不点亮的可以用一根好的内存去带动他.必须SD的带SD的.DDR的带DDR的.内存软件会自动跳过好的那根去检测坏的那条.7.使用方法:直接把软盘插入软驱,在主板的CMOS里设置软驱起动,起动后本软件会自动引导到测试界面进行检测RAM Stress Test(RST)内存测试软件使用指南近日比较关注内存的检测问题,找到了名为“RAM Stress Test”的软件(简称“R. S. T.)。

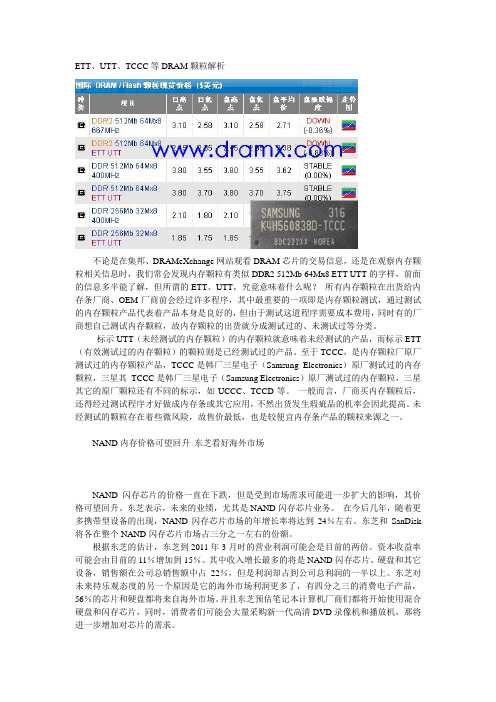

ETT、UTT、TCCC等DRAM颗粒解析

ETT、UTT、TCCC等DRAM颗粒解析不论是在集邦、DRAMeXchange网站观看DRAM芯片的交易信息,还是在观察内存颗粒相关信息时,我们常会发现内存颗粒有类似DDR2 512Mb 64Mx8 ETT UTT的字样,前面的信息多半能了解,但所谓的ETT、UTT,究竟意味着什么呢?所有内存颗粒在出货给内存条厂商、OEM厂商前会经过许多程序,其中最重要的一项即是内存颗粒测试,通过测试的内存颗粒产品代表着产品本身是良好的,但由于测试这道程序需要成本费用,同时有的厂商想自己测试内存颗粒,故内存颗粒的出货就分成测试过的、未测试过等分类。

标示UTT(未经测试的内存颗粒)的内存颗粒就意味着未经测试的产品,而标示ETT (有效测试过的内存颗粒)的颗粒则是已经测试过的产品。

至于TCCC,是内存颗粒厂原厂测试过的内存颗粒产品,TCCC是韩厂三星电子(Samsung Electronics)原厂测试过的内存颗粒,三星其TCCC是韩厂三星电子(Samsung Electronics)原厂测试过的内存颗粒,三星其它的原厂颗粒还有不同的标示,如UCCC、TCCD等。

一般而言,厂商买内存颗粒后,还得经过测试程序才好做成内存条或其它应用,不然出货发生瑕疵品的机率会因此提高。

未经测试的颗粒存在着些微风险,故售价最低,也是较便宜内存条产品的颗粒来源之一。

NAND内存价格可望回升东芝看好海外市场NAND闪存芯片的价格一直在下跌,但是受到市场需求可能进一步扩大的影响,其价格可望回升。

东芝表示,未来的业绩,尤其是NAND闪存芯片业务。

在今后几年,随着更多携带型设备的出现,NAND闪存芯片市场的年增长率将达到24%左右。

东芝和SanDisk 将各在整个NAND闪存芯片市场占三分之一左右的份额。

根据东芝的估计,东芝到2011年3月时的营业利润可能会是目前的两倍。

资本收益率可能会由目前的11%增加到15%。

其中收入增长最多的将是NAND闪存芯片、硬盘和其它设备,销售额在公司总销售额中占22%,但是利润却占到公司总利润的一半以上。

DDR测试及失效案例分享

Agenda• DRAM的测试方法和测试项目• DRAM失效案例分享DRAM的测试方法和测试项目内存测试法•内存厂了解记忆细胞排列结构,地址排列,漏电路径…...测试主要可分为-对记忆细胞单元透过特定背景数据排列,地址线(row address),地址线(column address)测试顺序,搭配内部电压调整进行不同漏电路径测试.-透过测试模式(test mode)调整内部讯号timing增加讯号的容限度-JEDEC定义功能及参数(AC/DC)测试-仿真系统开发random access测试方式高温(90℃)缺陷侦测& 工作电压边缘测试 (记录修补单元)针测卡电容修补低温性能测试&电容修补程序&修补后验证 (Advantest 5377)工厂晶圆产出测试晶圆产出高温性能测试 (Advantest 5377)晶圆测试流程低温(-10℃)缺陷侦测& 工作电压边缘测试 (记录修补单元)记忆单元修餔 验证修补位置及有效性晶圆测试项目介绍:测试站点 Test项目分类内容简述高温功能测试早夭不良品测试利用高温高工作电压测试条件,进行Wafer Burn-in,将制程可靠性风险之缺线提早筛选。

电容续航力测试测试高温Wafer Burn-in后电容续航力,剔除不良品。

内部电压优化透过设计预留fuse, 调整芯片电压至设计要求目标电容漏电流测试利用电容数组不同的排列方式及调整内部电压方式,侦测有漏电流的不良品,常见的有棋盘状排列。

电容保持能力测试利用static/dynamic pause及电容数组不同的排列方式来测试电容保持能力。

字符线开关测试利用字符线的频繁开关测试,来检测是否有制程缺陷在相邻字符线及相邻位线中。

数据传送测试缩短或调整电容数据传送到数据线之有效时间,将有前级数据传送问题之芯片刷出。

译码电路测试利用字符线与位线跳跃测试,将字符线或位线有译码问题的芯片刷出。

电流测试测试动态及静态电流值检测制程缺陷造成的漏电低温功能测试电容储存能力测试利用低温储存时间延长特性筛选电阻性漏电缺陷电容写入测试利用低温电子energy特性筛选数据写入困难cell放大器测试利用低温组件速度快特性调整内部放大器timing ,侦测cell讯号不良品。

DRAM原理详解

内存工作原理及发展历程RAM(Random Access Memory)随机存取存储器对于系统性能的影响是每个PC用户都非常清楚的,所以很多朋友趁着现在的内存价格很低纷纷扩容了内存,希望借此来得到更高的性能。

不过现在市场是多种内存类型并存的,SDRAM、DDR SDRAM、RDRAM等等,如果你使用的还是非常古老的系统,可能还需要EDO DRAM、FP DRAM(块页)等现在不是很常见的内存。

虽然RAM的类型非常的多,但是这些内存在实现的机理方面还是具有很多相同的地方,所以本文的将会分为几个部分进行介绍,第一部分主要介绍SRAM和异步DRAM(asynchronous DRAM),在以后的章节中会对于实现机理更加复杂的FP、EDO和SDRAM进行介绍,当然还会包括RDRAM和SGRAM等等。

对于其中同你的观点相悖的地方,欢迎大家一起进行技术方面的探讨。

存储原理:为了便于不同层次的读者都能基本的理解本文,所以我先来介绍一下很多用户都知道的东西。

RAM主要的作用就是存储代码和数据供CPU在需要的时候调用。

但是这些数据并不是像用袋子盛米那么简单,更像是图书馆中用有格子的书架存放书籍一样,不但要放进去还要能够在需要的时候准确的调用出来,虽然都是书但是每本书是不同的。

对于RAM等存储器来说也是一样的,虽然存储的都是代表0和1的代码,但是不同的组合就是不同的数据。

让我们重新回到书和书架上来,如果有一个书架上有10行和10列格子(每行和每列都有0-9的编号),有100本书要存放在里面,那么我们使用一个行的编号+一个列的编号就能确定某一本书的位置。

如果已知这本书的编号87,那么我们首先锁定第8行,然后找到第7列就能准确的找到这本书了。

在RAM存储器中也是利用了相似的原理。

现在让我们回到RAM存储器上,对于RAM存储器而言数据总线是用来传入数据或者传出数据的。

因为存储器中的存储空间是如果前面提到的存放图书的书架一样通过一定的规则定义的,所以我们可以通过这个规则来把数据存放到存储器上相应的位置,而进行这种定位的工作就要依靠地址总线来实现了。

内存器件介绍之RAM篇

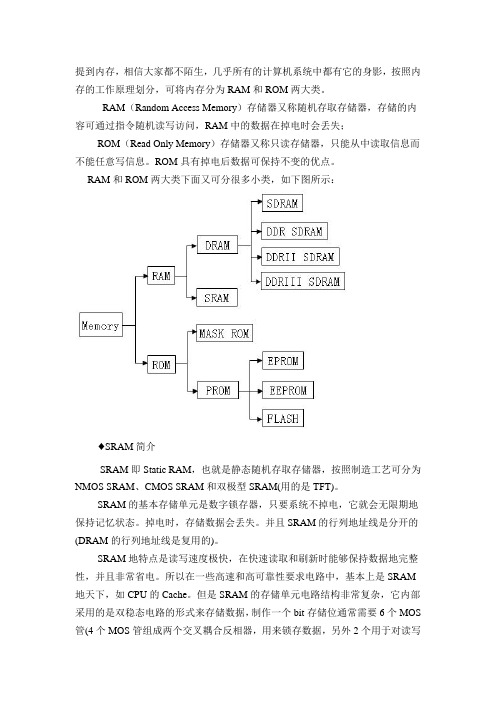

提到内存,相信大家都不陌生,几乎所有的计算机系统中都有它的身影,按照内存的工作原理划分,可将内存分为RAM和ROM两大类。

RAM(Random Access Memory)存储器又称随机存取存储器,存储的内容可通过指令随机读写访问,RAM中的数据在掉电时会丢失;ROM(Read Only Memory)存储器又称只读存储器,只能从中读取信息而不能任意写信息。

ROM具有掉电后数据可保持不变的优点。

RAM和ROM两大类下面又可分很多小类,如下图所示:♦SRAM简介SRAM即Static RAM,也就是静态随机存取存储器,按照制造工艺可分为NMOS SRAM、CMOS SRAM和双极型SRAM(用的是TFT)。

SRAM的基本存储单元是数字锁存器,只要系统不掉电,它就会无限期地保持记忆状态。

掉电时,存储数据会丢失。

并且SRAM的行列地址线是分开的(DRAM的行列地址线是复用的)。

SRAM地特点是读写速度极快,在快速读取和刷新时能够保持数据地完整性,并且非常省电。

所以在一些高速和高可靠性要求电路中,基本上是SRAM 地天下,如CPU的Cache。

但是SRAM的存储单元电路结构非常复杂,它内部采用的是双稳态电路的形式来存储数据,制作一个bit存储位通常需要6个MOS 管(4个MOS管组成两个交叉耦合反相器,用来锁存数据,另外2个用于对读写操作过程的控制)。

由于SRAM的复杂电路结构,使得成本要比DRAM高很多,而且其集成度低,很难做成大容量,一般只有几十KByte到几百KByte的容量,最大也就几MByte。

下图为6个NMOS构成的基本SRAM存储单元,Xi和Yj为字线;I/O为数据输入/输出端;R/W为读/写控制端。

当R/W=0时,进行写操作;当R/W=1时,进行读操作。

图中红色虚线框中的T1、T2、T3、T4、T5、T6六个NMOS管构成一个基本的存储单元。

T1、T3和T2、T4两个反相器交叉耦合构成触发器。

内存条颗粒和硬盘颗粒的区别

2.

内存条颗粒:内存条颗粒通常具有较小的存储容量。随着技术进步,内存颗粒的存储容量不断增加,但相对于硬盘颗粒仍然较小。内存条的主要目标是提供快速的读写速度,因此容量相对较小。

硬盘颗粒:硬盘颗粒的读写速度相对较慢。由于硬盘颗粒通常通过磁场来记录和检索数据,读写速度较内存条颗粒慢得多。这使得硬盘颗粒更适合存储大容量数据,例如媒体文件和档案。

4.

内存条颗粒:内存条颗粒的数据只在计算机开机时有效,并且在断电或关机后会丢失。此外,内存条颗粒上的数据不能轻易地移植到其他计算机上。

硬盘颗粒:硬盘颗粒上的数据是持久的,即使断电也不会丢失。此外,由于硬盘颗粒可以拆卸并连接到其他计算机上,数据可以轻松地在不同计算机之间进行迁移和共享。

5.

内存条颗粒:内,并且比较容易获得。

硬盘颗粒:硬盘颗粒的价格较内存条颗粒高。随着硬盘颗粒的容量增加,价格也会相应提高。此外,一些先进的存储技术(如固态硬盘)可能会进一步增加硬盘颗粒的成本。

结论

内存条颗粒和硬盘颗粒在计算机存储中扮演不同的角色。内存条颗粒提供快速的读写速度,但存储容量相对较小,并且数据在断电时丢失。相比之下,硬盘颗粒提供了更大的存储容量和持久性数据保存能力,但读写速度更低,并且相对更昂贵。了解这些区别有助于了解如何合理选择内存条和硬盘在不同计算机应用中的使用。

内存条颗粒和硬盘颗粒的区别

内存条颗粒和硬盘颗粒是计算机硬件中的两种重要元件。尽管它们在计算机系统中都扮演着存储数据的角色,但内存条颗粒和硬盘颗粒之间存在着一些显著的区别。本文将介绍内存条颗粒和硬盘颗粒的主要区别。

sdr,ddr1_2_3 ,gddr1_2_3_4_5 详细规格解释(下)

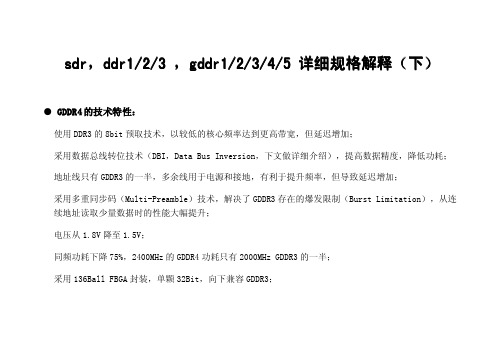

sdr,,ddr1/2/3,gddr1/2/3/4/5详细规格解释(下)sdr●GDDR4的技术特性:使用DDR3的8bit预取技术,以较低的核心频率达到更高带宽,但延迟增加;采用数据总线转位技术(DBI,Data Bus Inversion,下文做详细介绍),提高数据精度,降低功耗;地址线只有GDDR3的一半,多余线用于电源和接地,有利于提升频率,但导致延迟增加;采用多重同步码(Multi-Preamble)技术,解决了GDDR3存在的爆发限制(Burst Limitation),从连续地址读取少量数据时的性能大幅提升;电压从1.8V降至1.5V;同频功耗下降75%,2400MHz的GDDR4功耗只有2000MHz GDDR3的一半;采用136Ball FBGA封装,单颗32Bit,向下兼容GDDR3;GDDR4的确更好超,但性能提升有限由于采用了8bit预取技术,因此在相同频率下GDDR4的核心频率(即电容刷新频率)只有GDDR3的一半,理论上来讲GDDR4最高频率可达GDDR3的两倍。

但值得注意的是,虽然核心频率通过8bit预取技术减半,但GDDR4与GDDR3的I/O频率是完全相同的,因此GDDR4频率提升的瓶颈在于I/O 频率而不是核心频率。

由于制造工艺和技术水平的限制,虽然三星官方宣称早已生产出3GHz以上的GDDR4,但实际出货的GDDR4只有2GHz-2.5GHz,此后改进工艺的GDDR3也追平了这一频率。

在相同频率下,GDDR4比起GDDR3虽然功耗发热低,但延迟大性能稍弱,再加上成本高产量小,GDDR4遭受冷落并不意外。

●导致GDDR4失败的非技术方面原因GDDR3是NVIDIA和ATI参与JEDEC组织后共同制定的显存标准,而GDDR4在标准制定过程中双方产生了较大的分歧。

NVIDIA较为保守,认为应该保持DDR24bit预取技术不变,继续改进I/O控制器来提升频率;而ATI则比较激进,准备直接使用DDR38bit预取技术。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Multiple temperature tested (e.g. 88‟C, 25‟C, -10‟C) Long test time at low speed Patterns cover all cell arrays No Stressful condition High parallel test count, low cost Both MBT and TBT does NOT test DC (Ando Oven)

2.

Functional Test (Core Test)

3.

Speed Test

DC Test

VCC

DC Test Method: a) ISVM: I Source V Measure

VCC

b)

VSIM V Source I Measure

DC Test – Open Short

Purpose:

Socket issue Socket Pogo Pin defect

DC Test – Open Short

O/S Test Condition:

PMU

> 1.5V

Typical 0.65V < 0.2V Fail Open Pass Fail Short force 100uA force 0.65 V Measure sense 100uA Vdd=0

• Check connection between pins and test fixture

• Check if pin to pin is short in IC package • Check if pin to wafer pad has open in IC package • Check if protection diodes work on die • It is a quick electrical check to determine if it is safe to apply power • Also called Continuity Test

DC Test – Leakage

ILIH/ILIL: Input Leakage High/Low

• To verify input buffers offer a high resistance • No preconditioning pattern applied

ILOH/ILOL: Output Leakage High/Low

Failure Rate

BI

New product Mature product

Operation Time Infant Mortality Normal Life Worn out

Bath Curve

DRAM Burn-in (TBT)

TBT is for long time test patterns

• To verify tri-state output buffers offer a high resistance in off state • Test requires preconditioning pattern • Performed only on three-state outputs and bi-directional pins

DRAM Advantest Test

1.

DC Test

Open/Short test Leakage test IDD test Different parameter & Pattern for each function To check DRAM can operate functionally Timing test @ different speed grade

Backend

DRAM Burn-in (MBT)

MBT is to stress IC and screen out early failures

High Temperature Stress (125degC) High Voltage Stress Stressful Pattern

DC Test – Open Short

Failure Mode:

a) Wafer Problem

Defect of diode Wire touched

Core Circuit

Defective diode

b) Assembly Problem

Wire bonding Solder ball

c) Contact Problem

ISVM

Procedure

Other=0 Vss=0

•Ground all pins ( including VDD) •Using PMU force –100 uA, one pin at a time •Measure voltage •Fail open test if the voltage is less than –1.5 V •Fail short test if the voltage is greater than –0.2 V

IC Test Methodology

PPS Power Supply * DUT = Device Under Test

IC Tester

Driver

Input

DUT*

Comparator Output

Testing of a DUT: 1. To connect PPS, Driver, Comparator & GND. 2. To apply power to DUT. 3. To input data to DUT (Address, Control Command, Data) 4. To compare output with “expect value” and judge PASS/FAIL

•Apply VDDmax (2.0V) •Pre-condition all input pins to logic „0‟ (Low voltage) •Using PMU force VDDMAX to tested pin •Wait for 1 to 5 msec •Measure current of tested pin •Fail IIH test if the current is greater than +1.5 uA

Vss=0

DC Test – Output Leakage Low

Test Condition:

Introduction to DRAM Testing

--- DRAM inside team --- 2015.May

Agenda

Basis of Testing Typical DRAM Testing Flow Burn-in DC Test (Open/Short, Leakage, IDD) Functional Test & Test Pattern Speed Test

DC Test – Leakage

Purpose:

• Verify resistance of pin to VDD/VSS is high enough

• Verify resistance of pin to pins is high enough • Identify process problem in CMOS device

Core Test

Speed Test

• Speed & AC Timing Test • Full Speed (DDR3 @1600MHz and above), Advantest T5503 + 256DUT HiFix

• Marking Ball Scan Visual Inspection Baking Vacuum Pack

Test Condition:

PMU

Pass < –1.5 uA Fail 0V force “0” OFF VDDmax ILIL all input pins = 2.3V

-10nA

Measure ON

VLSI Core

“1”

Procedure

Vss=0

•Apply VDDmax (2.0V) •Pre-condition all input pins to logic „1‟ (high voltage) •Using PMU (Parametric Measure Unit) force Ground to tested pin •Wait for 1 to 5 msec •Measure current of tested pin •Fail IIL test if the current is less than –1.5 uA

DC Test – Open Short

O/S Test Condition:

PMU

> –0.2 V

Fail Short force -100uA force -0.65 V Measure sense -100uA Vdd=0

Typical -0.65V Pass <–1.5 V Fail Open

ISVMProcedureOther=0 Vss=0

•Ground all pins ( including VDD) •Using PMU force 100 uA, one pin at a time •Measure voltage •Fail open test if the voltage is greater than 1.5 V •Fail short test if the voltage is less than 0.2 V