Direct current voltage induced by microwave signal in a ferromagnetic wire

GS4157 4157B 低电压、2.8Ω双极性SPDT分析开关说明书

GS 4157/4157BLow-Voltage, 2.8Ω SPDT Analog SwitchGeneral DescriptionThe GS 4157/4157B is a high-bandwidth, fast single-pole double-throw (SPDT) CMOS switch. It can be used as an analog switch or as a low-delay bus switch. Specified over a wide operating power supply voltage range, 1.65V to 5.5V, the GS 4157/4157B has a maximum ON resistance of 5.1-ohms at 1.65V, 3.9-ohms at 2.3V & 2.85-ohms at 4.5V. Break-before-make switching prevents both switches being enabled simultaneously. This eliminates signal disruption during switching.The control input, S, tolerates input drive signals up to 5.5V, independent of supply voltage. GS 4157/4157B is an improved direct replacement for the FSA4157/NC7SB4157ApplicationsCell Phones PDAsPortable InstrumentationBattery Powered Communications Computer PeripheralsConnection Diagram(Top View)SC70-6 65S VCC 4AGND 3B0B121TDFN-6Features♦CMOS Technology for Bus and Analog Applications♦LowONResistance:***********♦Wide VCC Range: 1.65V to 5.5V ♦Rail-to-Rail Signal Range♦Control Input Overvoltage Tolerance: 5.5V min.♦High Off Isolation: 57dB at 10MHz♦54dB (10MHz) Crosstalk Rejection Reduces Signal Distortion♦Break-Before-Make Switching ♦High Bandwidth: 300 MHz♦Extended Industrial Temperature Range: –40°C to 85°C♦Improved Direct Replacement for NC7SB4157♦Packaging (Pb-free & Green available):Pin DescriptionLogic Function TableLogic Input (S)Function 0 B0 Connected to A 1B1 Connected to ANameDescription S Logic ControlVcc Positive Power Supply ACommon Output/Data Port B0 Data Port (Normally Closed) GND Ground B1Data PortABSOLUTE MAXIMUM RATINGS(1) RECOMMENDED OPERATING CONDITIONS(3)Supply Voltage V CC.........................................–0.5V to +7V DC Switch Voltage (V S)(2).…….......…..–0.5V to V CC +0.5V DC Input Voltage (V IN)(2).…..…….....….......–0.5V to +7.0V DC V CC or Ground Current (I CC/I GND)..................±100mA DC Output Current (V OUT) .......................................128mA Storage Temperature Range (T STG) ....... –65°C to +150°C Junction Temperature under Bias (T J) .......…............ 150°C Junction Lead Temperature (T L)(Soldering, 10 seconds) .................................... 260°C Power Dissipation (P D) @ +85°C .............................180mW Supply Voltage Operating (V CC)………………1.65V to 5.5V Control Input Voltage (V IN)………………………..0V to V CC Switch Input Voltage (V IN)…………………………0V to V CC Output Voltage (V OUT)…………………………….0V to V CC Operating Temperature (T A)………………...–40°C to +85°C Thermal Resistance (θJA)…………………………..350°C/WNote 1:A bsolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied.Note 2:The input and output negative voltage ratings may be exceeded if the input and output diode current ratings are observed.Note 3:Control input must be held HIGH or LOW; it must not float.I CC Quiescent Supply CurrentNote 4: Measured by voltage drop between A and B pins at the indicated current through the device. ON resistance is determined by the lower of the voltages on two ports (A or B)Note 5: Parameter is characterized but not tested in production.Note 6: DR ON = R ON max – R ON min. measured at identical V CC, temperature and voltage levels.Note 7: Flatness is defined as difference between maximum and minimum value of ON resistance over the specified range of conditions..Note 8: Guaranteed by design.CAPACITANCE(12)Parameter Description TestConditionsSupplyVoltageTemp (ºC) Min. Typ Max. UnitsC IN Control Input 2.3pF C IO-B For B Port,Switch OFFf= 1 MHz(12)V CC = 5.0V T A = 25°C 6.5C IOA-ON For A Port, Switch ON 18.5Disable TurnOFF Time: A to Bnt PLZ t PHZNote 6: Guaranteed by designNote 7: Guaranteed by design but not production tested. The device contributes no other propagation delay other thanthe RC delay of the switch ON resistance and the 50pF load capacitance, whne driven by an ideal voltage source with zero output impedance.Note 8: Off Isolation = 20 Log10 [ V A / V Bn ] and is measured in dB. Note 9: TA = 25°C, f = 1MHz. Capacitance is characterized but not tested in production.TEST CIRCUITS AND TIMING DIAGRAMSIS l=lln!:ill..::!VouTI100pF0 = (t.VOUT)(CL)Figure 4. Charge Injection TestveeFigure 5. Off IsolationVeeLogic Input ov or BJHFigure 7. Channel Off CapacitanceLogic Inputav 。

MIC4414 MIC4415低压MOSFET驱动器商品说明书

MIC4414/MIC4415 EvaluationBoard1.5A / 4.5V to 18VLow-Side MOSFET Driver Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • General DescriptionThe MIC4414 and MIC4415 are low-side MOSFETdrivers designed to switch an N-channel enhancementtype MOSFET in low-side switch applications. TheMIC4414 is a non-inverting driver and the MIC4415 isan inverting driver. These drivers feature short delaysand high peak current to produce precise edges andrapid rise and fall times.The MIC4414/15 are powered from a 4.5V to 18Vsupply and can sink and source peak currents up to1.5A, switching a 1000pF capacitor in 12ns. The on-state gate drive output voltage is approximately equalto the supply voltage (no internal regulators orclamps). High supply voltages, such as 10V, areappropriate for use with standard N-channelMOSFETs. Low supply voltages, such as 5V, areappropriate for use with many logic-level N-channelMOSFETs.In a low-side configuration, the driver can control aMOSFET that switches any voltage up to the rating ofthe MOSFET.Datasheets and support documentation can be foundon Micrel’s web site at: .RequirementsThe MIC4414/MIC4415 evaluation board requires onlya single power supply to power the driver and afunction generator or logic signal to drive the IN pin.PrecautionsThe MIC4414/MIC4415 evaluation board does nothave reverse polarity protection. Applying a negativevoltage to the VDD and GND terminals may damagethe device. The maximum VDD of the board is ratedat 20V. Exceeding 20V on the VDD could damage thedevice.Getting Started1. VDD SupplyConnect a supply to the VS and GND terminals,paying careful attention to the polarity and the supplyrange (4.5V < VDD < 18V). Monitor I DD with a currentmeter and VDD at VS and GND terminals withvoltmeter. Do not apply power until Step 4.2. Connect Function Generator to IN pinConnect the Function generator output to IN pin andGND.3. OUT SignalThe voltage on OUT pin can be monitored by either avoltmeter or with scope probe.4. Turn on the PowerTurn on the VDD supply and apply logic signal to INpin, and verify OUT signal. The on-state gate driveoutput voltage is approximately equal to the supplyvoltage (no internal regulators or clamps). Since theMIC4414 is a non-inverting driver so a logic highsignal on the IN pin makes the OUT signal high(typically VDD) and MIC4415 is an inverting driver sologic low signal on the IN pin makes the OUT signalhigh (typically VDD).The user has a flexibility of soldering a FET (Q1) orusing different values of capacitors to imitate the gatecapacitance (C3).Ordering InformationPart Number DescriptionMIC4414YFT EV MIC4414 Evaluation BoardMIC4415YFT EV MIC4415 Evaluation BoardMIC4414/MIC4415 Evaluation Board Typical CharacteristicsNote:1. MIC4414 ON IN =5V; OFF IN = 0V.2. MIC4415 ON IN =0V; OFF IN = 5V.Typical Characteristics (Continued)MIC4414/MIC4415 Evaluation Board SchematicFigure 1. MIC4414/MIC4415 Evaluation board schematicBill of MaterialsItem Part Number Manufacturer Description Qty C1 GRM188R71E104KA01D Murata (1)0.1µF/25V Ceramic Capacitor, X7R, Size 06031C2012X5R1E475K TDK (2)GRM21BR61E475KA12L Murata C2 08053D475KAT2A AVX (3) 4.7µF/25V Ceramic Capacitor, X5R, Size 08051C3, Q1Do not populate (DNP)U1MIC4414YFT MIC4415YFTMicrel, Inc.(4)1.5A/4.5V to 18V Low Side MOSFET Driver1Notes:1. Murata: .2. TDK: .3. AVX: 4.Micrel, Inc.: .Evaluation Board PCB LayoutMIC4414/MIC4415 Evaluation Board - Copper Layer 1 (Top)MIC4414/MIC4415Evaluation Board - Copper Layer 2 (Bottom)。

MAXIM MAX3397E 数据手册

General DescriptionThe MAX3397E ±15kV ESD-protected bidirectional level translator provides level shifting for data transfer in a multivoltage system. Externally applied voltages, V CC and V L , set the logic levels on either side of the device.A logic-low signal present on the V L side of the device appears as a logic-low signal on the V CC side of the device, and vice versa. The MAX3397E utilizes a trans-mission-gate-based design to allow data translation in either direction (V L ↔V CC ) on any single data line. The MAX3397E accepts V L from +1.2V to +5.5V and V CC from +1.65V to +5.5V, making the device ideal for data transfer between low-voltage ASI Cs/PLDs and higher voltage systems.The MAX3397E features a shutdown mode that reduces supply current to less than 1µA, thermal short-circuit pro-tection, and ±15kV ESD protection on the V CC side for greater protection in applications that route signals exter-nally. The MAX3397E operates at a guaranteed data rate of 8Mbps over the entire specified operating voltage range. Within specific voltage domains, higher data rates are possible. See the Timing Characteristics table.The MAX3397E is available in an 8-pin µDFN package and specified over the extended -40°C to +85°C oper-ating temperature range.ApplicationsCell Phones, MP3 Players Telecommunications EquipmentSPI™, MICROWIRE™, and I 2C Level Translation Portable POS Systems, Smart Card Readers Low-Cost Serial Interfaces, GPSFeatures♦Bidirectional Level Translation ♦Guaranteed Data Rate8Mbps (+1.2V ≤V L ≤V CC ≤+5.5V)16Mbps (+1.8V ≤V L ≤V CC ≤+3.3V)♦Extended ESD Protection on the I/O V CC Lines±15kV Human Body Model±15kV Air-Gap Discharge per IEC 61000-4-2±8kV Contact Discharge per IEC 61000-4-2♦Enable/Shutdown♦Ultra-Low 1µA Supply Current in Shutdown Mode ♦8-Pin µDFN PackageMAX3397EDual Bidirectional Low-LevelTranslator in µDFN________________________________________________________________Maxim Integrated Products1For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Typical Application Circuit appears at end of data sheet.SPI is a trademark of Motorola, Inc.MICROWIRE is a trademark of National Semiconductor Corp.+Denotes a lead-free package.Pin ConfigurationM A X 3397EDual Bidirectional Low-Level Translator in µDFN 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.(All voltages referenced to GND.)V CC , V L .....................................................................-0.3V to +6V I/O V CC_......................................................-0.3V to (V CC + 0.3V)I/O V L_..........................................................-0.3V to (V L + 0.3V)EN.............................................................................-0.3V to +6V Short-Circuit Duration I/O V L_, I/O V CC_to GND .......ContinuousContinuous Power Dissipation (T A = +70°C)8-Pin µDFN (derate 4.8mW/°C above +70°C)............381mW Operating Temperature Range ...........................-40°C to +85°C Storage Temperature Range.............................-65°C to +150°C Lead Temperature (soldering, 10s).................................+300°CELECTRICAL CHARACTERISTICSMAX3397EDual Bidirectional Low-LevelTranslator in µDFNELECTRICAL CHARACTERISTICS (continued)(V CC = +1.65V to +5.5V, V L = +1.2V to 5.5V, I/O V L_, and I/O V CC_are unconnected, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V = +3.3V, V = +1.8V, T = +25°C.) (Notes 1, 2)TIMING CHARACTERISTICSM A X 3397EDual Bidirectional Low-Level Translator in µDFN 4_______________________________________________________________________________________Note 1:All units are 100% production tested at T A = +25°C. Limits over the operating temperature range are guaranteed by designand not production tested.Note 2:For normal operation, ensure V L <(V CC + 0.3V).Note 3:When V CC is below V L by more than the tri-state threshold, the device turns off its pullup resistors and I/O_ enters tri-state.The device is not in shutdown.Note 4:To ensure maximum ESD protection, place a 1µF capacitor between V CC and GND. See the Typical Application Circuit .Note 5:10% of input to 90% of output.Note 6:90% of input to 10% of output.TIMING CHARACTERISTICS (continued)(V = +1.65V to +5.5V, V = +1.2V to +5.5V, R = 1M Ω, C = 15pF, driver output impedance ≤50Ω, I /O test signal of Typical Operating Characteristics(V CC = +3.3V, V L = +1.8V, R LOAD = 1M Ω, C LOAD = 15pF, T A = +25°C, data rate = 8Mbps, unless otherwise noted.)0100502001502503001.653.303.852.202.754.404.955.50V L SUPPLY CURRENT vs. V CC SUPPLY VOLTAGE(DRIVING ONE I/O V L_)M A X 3397E t o c 01V CC SUPPLY VOLTAGE (V)V L S U P P L Y C U R R E N T (μA )501501002002501.652.752.203.303.854.404.955.50V L SUPPLY CURRENT vs. V CC SUPPLY VOLTAGE(DRIVING ONE I/O V CC_)M A X 3397E t o c 02V CC SUPPLY VOLTAGE (V)V L S U P P L Y C U R R E N T (μA )03001002005004007006008001.21.92.63.3V CC SUPPLY CURRENT vs. V L SUPPLY VOLTAGE(DRIVING ONE I/O V L_)M A X 3397E t o c 03V L SUPPLY VOLTAGE (V)V C C S U P P L Y C U R R E N T (μA )MAX3397EDual Bidirectional Low-LevelTranslator in µDFN_______________________________________________________________________________________50100502001503002503501.21.92.63.3V CC SUPPLY CURRENT vs. V L SUPPLY VOLTAGE(DRIVING ONE I/O V CC_)M A X 3397E t o c 04V L SUPPLY VOLTAGE (V)V C C S U P P L Y C U R R E N T (μA )60402080100120140160180200-4010-15356085V L SUPPLY CURRENT vs. TEMPERATURE(DRIVING ONE I/O V L_)M A X 3397E t o c 05TEMPERATURE (°C)V L S U P P L Y C U R R E N T (μA )10050200150300250350-4010-15356085V L SUPPLY CURRENT vs. TEMPERATURE(DRIVING ONE I/O V CC_)M A X 3397E t o c 06TEMPERATURE (°C)V L S U P P L Y C U R R E N T (μA )04020806012010014002010304052515354550V L SUPPLY CURRENT vs. CAPACITIVE LOAD(DRIVING ONE I/O V L_)M A X 3397E t o c 07CAPACITIVE LOAD (pF)V L S U P P L Y C U R R E N T (μA )6004002008001000120002015510253035404550V CC SUPPLY CURRENT vs. CAPACITIVE LOAD(DRIVING ONE I/O V L_)M A X 3397E t o c 08CAPACITIVE LOAD (pF)V C C S U P P L Y C U R R E N T (μA )5101520252025101553035404550RISE/FALL TIME vs. CAPACITIVE LOAD(DRIVING ONE I/O V L_)CAPACITIVE LOAD (pF)R I S E /F A L L T I M E (n s )06428101202015510253035404550PROPAGATION DELAY vs. CAPACITIVE LOAD(DRIVING ONE I/O V L_)M A X 3397E t o c 10CAPACITIVE LOAD (pF)P R O P A G A T I O N D E L A Y (n s )642810122015510253035404550RISE/FALL TIME vs. CAPACITIVE LOAD(DRIVING ONE I/O V CC_)CAPACITIVE LOAD (pF)R I S E /F A L L T I M E (n s )214365798101015205253035454050PROPAGATION DELAY vs. CAPACITIVE LOAD(DRIVING ONE I/O V CC_)CAPACITIVE LOAD (pF)P R O P A G A T I O N D E L A Y (n s )M A X 3397E t o c 12M A X 3397EDual Bidirectional Low-Level Translator in µDFN 6_______________________________________________________________________________________Detailed DescriptionThe MAX3397E bidirectional, ESD-protected level translator provides the level shifting necessary to allow data transfer in a multivoltage system. Externally applied voltages, V CC and V L , set the logic levels on either side of the device. A logic-low signal present on the V L side of the device appears as a logic-low signal on the V CC side of the device, and vice versa. The device uses a transmission-gate-based design (see the Functional Diagram ) to allow data translation in either direction (V L ↔V CC ) on any single data line. The MAX3397E accepts V L from +1.2V to +5.5V and V CCfrom +1.65V to +5.5V, making the device ideal for data transfer between low-voltage ASI Cs/PLDs and higher voltage systems.The MAX3397E features a shutdown mode that reduces the supply current to less than 1µA, thermal short-circuit protection, and ±15kV ESD protection on the V CC side for greater protection in applications that route signals externally. The device operates at a guar-anteed data rate of 8Mbps over the entire specified operating voltage range. Within specific voltage domains, higher data rates are possible. See the Timing Characteristics table.Typical Operating Characteristics (continued)(V CC = +3.3V, V L = +1.8V, R LOAD = 1M Ω, C LOAD = 15pF, T A = +25°C, data rate = 8Mbps, unless otherwise noted.)RAIL-TO-RAIL DRIVING (DRIVING ONE I/O V L_)MAX3397E toc1320ns/divI/O V L_I/O V CC_1V/div1V/divEXITING SHUTDOWN MODEMAX3397E toc142μs/divI/O V CC_EN2V/divI/O V L_1V/div1V/divMAX3397EDual Bidirectional Low-LevelTranslator in µDFN_______________________________________________________________________________________7Level TranslationFor proper operation, ensure that +1.65V ≤V CC ≤+5.5V and +1.2V ≤V L ≤+5.5V. During power-up sequencing,V L ≥(V CC + 0.3V) does not damage the device. The speed-up circuitry limits the maximum data rate for the MAX3397E to 16Mbps. The maximum data rate also depends heavily on the load capacitance (see the Typical Operating Characteristics ), output impedance of the driver, and the operational voltage range (see the Timing Characteristics table).Rise-Time AcceleratorsThe MAX3397E has an internal rise-time accelerator,allowing operation up to 16Mbps. The rise-time accelera-tors are present on both sides of the device and act to speed up the rise time of the input and output of the device, regardless of the direction of the data. The trig-gering mechanism for these accelerators is both level and edge sensitive. To prevent false triggering of the rise-time accelerators, signal fall times of less than20ns/V are recommended for both the inputs and outputs of the device. Under less noisy conditions, longer signal fall times are acceptable. Note:To guarantee operation of the rise time, accelerators the maximum parasitic capacitance should be less than 200pF on the I/O lines.Shutdown ModeDrive EN low to place the MAX3397E in shutdown mode. Connect EN to V L or V CC (logic-high) for normal operation. Activating the shutdown mode disconnects the internal 10k Ωpullup resistors on the I /O V CC and I/O V L lines. This forces the I/O lines to a high-imped-ance state, and decreases the supply current to less than 1µA. The high-impedance I /O lines in shutdown mode allow for use in a multidrop network. The MAX3397E effectively has a diode from each I/O to the corresponding supply rail and GND. Therefore, when in shutdown mode, do not allow the voltage at I/O V L_to exceed (V L + 0.3V), or the voltage at I /O V CC_ to exceed (V CC + 0.3V).Figure 1a. Rail-to-Rail Driving I/O V L Figure 1b. Rail-to-Rail Driving I/O V CCM A X 3397EDual Bidirectional Low-Level Translator in µDFN 8_______________________________________________________________________________________Operation with One Supply DisconnectedCertain applications require sections of circuitry to be disconnected to save power. When V L is connected and V CC is disconnected or connected to ground, the device enters shutdown mode. In this mode, I/O V L can still be driven without damage to the device; however, data does not translate from I /O V L to I /O V CC . I f V CC falls more than 0.8V (typ) below V L , the device disconnects the pullup resistors at I /O V L and I /O V CC . To achieve the lowest possible supply current from V L when V CC is disconnected, it is recommended that the voltage at the V CC supply input be approximately equal to GND. Note:When V CC is disconnected or connected to ground, I/O V CC must not be driven more than V CC + 0.3V.When V CC is connected and V L is less than 0.7V (typ),the device enters shutdown mode. I n this mode, I /O V CC can still be driven without damage to the device;however, data does not translate from I/O V CC to I/O V L .Note: When V L is disconnected or connected to ground, I/O V L must not be driven more than V L + 0.3V.Thermal Short-Circuit ProtectionThermal-overload detection protects the MAX3397E from short-circuit fault conditions. I n the event of a short-circuit fault, when the junction temperature (T J )reaches +150°C, a thermal sensor signals the shut-down mode logic to force the device into shutdown mode. When the T J has cooled to +140°C, normal operation resumes.±15kV ESD ProtectionAs with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electro-static discharges encountered during handling and assembly. The I /O V CC lines have extra protection against static electricity. Maxim’s engineers have developed state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown mode, and powered down. After an ESD event, Maxim’s E versions keep working withoutFigure 1c. Open-Drain Driving I/O V L Figure 1d. Open-Drain Driving I/O V CCMAX3397EDual Bidirectional Low-LevelTranslator in µDFN_______________________________________________________________________________________9latchup, whereas competing products can latch and must be powered down to remove latchup. ESD protec-tion can be tested in various ways. The I/O V CC lines of the MAX3397E are characterized for protection to the following limits:1)±15kV using the Human Body Model2)±8kV using the Contact Discharge method specifiedby IEC 61000-4-23)±15kV using the Air-Gap Discharge method specifiedby IEC 61000-4-2ESD Test ConditionsESD performance depends on a variety of conditions.Contact Maxim for a reliability report that documents test setup, test methodology, and test results.Human Body ModelFigure 2a shows the Human Body Model, and Figure 2b shows the current waveform it generates when dis-charged into a low-impedance state. This model con-sists of a 100pF capacitor charged to the ESD voltage of interest that is then discharged into the test device through a 1.5k Ωresistor.IEC 61000-4-2The I EC 61000-4-2 standard covers ESD testing and performance of finished equipment; it does not specifi-cally refer to integrated circuits. The MAX3397E helpsFigure 2b. Human Body Current WaveformFigure 2a. Human Body ESD Test ModelM A X 3397EDual Bidirectional Low-Level Translator in µDFN10______________________________________________________________________________________to design equipment that meets Level 4 of IEC 61000-4-2 without the need for additional ESD-protection com-ponents.The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in I EC 61000-4-2 because series resistance is lower in the I EC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is gener-ally lower than that measured using the Human Body Model. Figure 3a shows the IEC 61000-4-2 model, and Figure 3b shows the current waveform for the ±8kV,IEC 61000-4-2, Level 4, ESD contact-discharge test.The Air-Gap test involves approaching the device with a charged probe. The contact-discharge method connects the probe to the device before the probe is energized.Machine ModelThe Machine Model for ESD tests all pins using a 200pF storage capacitor and zero discharge resis-tance. Its objective is to emulate the stress caused by contact that occurs with handling and assembly during manufacturing. Of course, all pins require this protec-tion during manufacturing, not just inputs and outputs.Therefore, after PCB assembly, the Machine Model is less relevant to I/O ports.Applications InformationPower-Supply DecouplingTo reduce ripple and the chance of transmitting incorrect data, bypass V L and V CC to ground with a 0.1µF capaci-tor (see the Typical Application Circuit ). To ensure full ±15kV ESD protection, bypass V CC to ground with a 1µF capacitor. Place all capacitors as close as possible to the power-supply inputs.I 2C Level TranslationThe MAX3397E level-shifts the data present on the I/O lines between +1.2V and +5.5V, making them ideal for level translation between a low-voltage ASI C and an I 2C device. A typical application involves interfacing a low-voltage microprocessor to a 3V or 5V D/A convert-er, such as the MAX517.Push-Pull vs. Open-Drain DrivingThe MAX3397E can be driven in a push-pull configura-tion and include internal 10k Ωresistors that pull up I/O V L_and I /O V CC_to their respective power supplies,allowing operation of the I /O lines with open-drain devices. See the Timing Characteristics table for maxi-mum data rates when using open-drain drivers.Chip InformationPROCESS: BiCMOSFigure 3b. IEC 61000-4-2 ESD Generator Current Waveform Figure 3a. IEC 61000-4-2 ESD Test ModelMAX3397EDual Bidirectional Low-LevelTranslator in µDFN______________________________________________________________________________________11Typical Application CircuitM A X 3397EDual Bidirectional Low-Level Translator in µDFN 12______________________________________________________________________________________Package Information(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)MAX3397EDual Bidirectional Low-LevelTranslator in µDFNMaxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________13©2007 Maxim Integrated Productsis a registered trademark of Maxim Integrated Products, Inc.Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

LC-残像

短路 0

短路过程:

在给液晶盒两端施加一段时间的直流电压以后,将液晶盒的充电端用导线连接 接地。这时PI层仍然保持其电势差的状态,所以短路时跟液晶层施加了如图的 电场,从而使得液晶层中的离子开始按照新建电场运动。

0

开路

0

0

3,理论模型 V 充电

短路

断路过程: 在短暂的短路过程以后,液晶层的内电场,使得液晶中未被吸附的离子反向运 动,使得液晶的内电场慢慢减弱,由于PI的离子解吸附比液晶中的离子运动要 难很多,所以前一阶段主要是液晶中离子运动,而后一阶段主要跟PI中的离子 有关。当液晶层两端的电势差相等,即内电场消失时,VRDC值达到最大,随 着时间的变长,PI中的正负离子会解吸附一部分,异性相消,使得液晶层中的 电势进一步降低,PI层的电势差也有一定的降低,VRDC减小,在稳定以后, 随着PI与离子吸附与解吸附关系的稳定,VRDC的值也趋于稳定。

开路

T

t

t

RDC 2V0 (e PI e ) LC

其中

PI RPICPI PIPI

LC RLCCLC LCLC

Residual Image

基本概念: 残影是指长时间点亮一个画面,切换画面之后前一个画面不会立刻消失而是慢慢不见的现象。

产生机制: 通常是在同一画面显示太久的情况下,液晶内的极性成分吸附在上下玻璃两端形成内建电场,画面切换之后这些离子没有 立刻释放出来,使得液晶分子没有立刻转到应转的角度所造成。另外一种情况则是因为画素电极设计不良,使得液晶分子 在状态切换时排列错乱,这种情况之下也有可能看到残影。

测试过程:R-DC测量是施加直流电压在液晶盒一段时间,再短路液晶盒,再将液晶盒开路后的测得残留电压值。

测试原理:

阿尔达尼奥Nano RP2040 Connect产品参考手册说明书

1 The board

6

1.1 Application examples

6

1.2 Accessories

6

1.3 Related products

6

2 Ratings

6

2.1 Recommended operating conditions

6

2.2 Power consumption

7

3 Functional overview

13

4.4 Sample Sketches

13

4.5 Online resources

13

4.6 Board Recovery

13

5 Connector Pinouts

14

5.1 J1 Micro USB

14

5.2 JP1

14

5.3 JP2

14

5.4 RP2040 SWD Pad

15

5.5 Nina W102 SWD Pad

2 / 19

Arduino® Nano RP2040 Connect / Rev. 01 - 14/05/2021

Arduino® Nano RP2040 Connect

Microchip® ATECC608A Crypto Cryptographic Co-Processor with Secure Hardware-Based Key Storage I2C, SWI Hardware Support for Symmetric Algorithms: SHA-256 & HMAC Hash including off-chip context save/restore AES-128: Encrypt/Decrypt, Galois Field Multiply for GCM

电源电压转换:什么是DCDC转换器

电源电压转换:什么是DC/DC转换器2009-04-10 14:28DC/DC转换器为转变输入电压后有效输出固定电压的电压转换器。

DC/DC转换器分为三类:升压型DC/DC转换器、降压型DC/DC转换器以及升降压型DC/DC转换器。

根据需求可采用三类控制。

PWM控制型效率高并具有良好的输出电压纹波和噪声。

PFM控制型即使长时间使用,尤其小负载时具有耗电小的优点。

PWM/PFM转换型小负载时实行PFM控制,且在重负载时自动转换到PWM控制。

目前DC-DC转换器广泛应用于手机、MP3、数码相机、便携式媒体播放器等产品中。

什么是DC(Direct Current)呢?它表示的是直流电源,诸如干电池或车载电池之类。

家庭用的100V电源是交流电源(AC)。

若通过一个转换器能将一个直流电压(3.0V)转换成其他的直流电压(1.5V或5.0V),我们称这个转换器为DC/DC转换器,或称之为开关电源或开关调整器。

A: DC/DC转换器一般由控制芯片,电感线圈,二极管,三极管,电容器构成。

在讨论DC/DC 转换器的性能时,如果单单针对控制芯片,是不能判断其优劣的。

其外围电路的元器件特性,和基板的布线方式等,能改变电源电路的性能,因此,应进行综合判断。

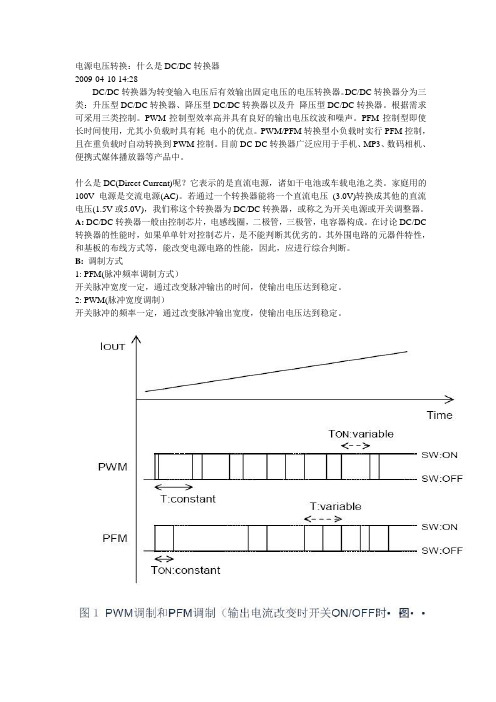

B:调制方式1: PFM(脉冲频率调制方式)开关脉冲宽度一定,通过改变脉冲输出的时间,使输出电压达到稳定。

2: PWM(脉冲宽度调制)开关脉冲的频率一定,通过改变脉冲输出宽度,使输出电压达到稳定。

C:通常情况下,采用PFM和PWM这两种不同调制方式的DC/DC转换器的性能不同点如下。

** PWM的频率,PFM的占空比的选择方法。

* PWM调制方式在选用较高频率的情况下(如:500KHz)(1)小负载时,效率很低。

(2)输出电压的纹波较小。

在选用较低频率的情况下(如:100KHz)(1)小负载时,效率较高。

(2)输出电压的纹波较大。

因此,在小负载或待机时间较长的情况下,选用100KHz的频率,转换电路的效率较高,但若考虑输出电压的纹波问题,若选用500KHz的频率,纹波电压会较小。

MIC23150 2A 4MHz 轻量级加载模式降压电源参考手册说明书

MIC23150 Evaluation Board4MHz 2A Buck Regulator withHyperLight Load™HyperLight Load is a trademark of Micrel, Inc. MLF is a registered trademark of Amkor Technology.Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • General DescriptionThe MIC23150 is a 2A 4MHz switching regulator featuring HyperLight Load™ mode. The MIC23150 is highly efficient throughout the entire output current range, drawing just 23µA of quiescent current in operation. The tiny 2mm x2mm MLF ®package, in combination with the 4MHz switching frequency, enables a compact sub-1mm height solution with only three external components. The MIC23150 provides accurate output voltage regulation under the most demanding conditions and responds extremely quickly to a load transient with exceptionally small output voltage ripple.Factoring in the output current, the internal circuitry of the MIC23150 automatically selects between two modes of operation for optimum efficiency. Under light load conditions, the MIC23150 goes into HyperLight Load™mode. HyperLight Load™ uses a Pulse-Frequency Modulation (PFM) control scheme that controls the off time at light load. This proprietary architecture reduces the amount of switching needed at light load, thereby increasing operating efficiency. The MIC23150 attains up to 87% efficiency at 1mA output load. As the load current increases beyond approximately 100mA, the device operates using the Pulse-Width Modulation (PWM) method for up to 93% efficiency at higher load. The two modes of operation ensure the highest efficiency across the entire load range.The MIC23150 operates from an input voltage range of 2.7V to 5.5V and features internal power MOSFETs that deliver up to 2A of output current. This step-down regulator provides an output voltage accuracy of +/-2.5% across the junction temperature range of -40ºC to +125ºC. The MIC23150 is available in fixed output versions supporting an output voltage as low as 1.0V.RequirementsThe MIC23150 evaluation board requires an input power source that is able to deliver greater than 2A at 2.7V to the MIC23150. The output load can either be an active (electronic) or passive (resistive) load.Getting Started1. Connect an external supply to the V IN (J1)terminal . Apply the desired input voltage to V IN (J1) and ground (J2) terminals of the evaluation board, paying careful attention to polarity and supply voltage (2.7V ≤ V IN ≤ 5.5V). An ammeter may be placed between the input supply and the V IN (J1) terminal. Be sure to monitor the supply voltage at the V IN (J1) terminal, since the ammeter and/or power lead resistance can reduce the voltage supplied to the device.2. Connect a load to the V OUT (J3) and groundterminal (J4). The load can be either passive (resistive) or active (electronic load). An ammeter may be placed between the load and the output terminal. Ensure the output voltage is monitored at the V OUT (J3) terminal.3. Enable the MIC23150. The MIC23150 evaluationboard has a pull-up resistor to V IN . To disable the device, apply a voltage below 0.5V to the EN (J5)terminal. In the absence of the pull-up resistor, the device is enabled by applying a voltage greater than 1.2V to the EN (J5) terminal. The enable pin must be either pulled high or low for proper operation. Removing the pull-up resistor and leaving the pin floating will cause the regulator to operate in an unknown state.Output VoltageThe MIC23150 evaluation board is available with the following output voltage options listed below:Ordering InformationPart Number Description(2)MIC23150-CYMT EV (1) 1.0V Fixed Output Evaluation Board MIC23150-4YMT EV(1)1.2V Fixed Output Evaluation Board MIC23150-GYMT EV 1.8V Fixed Output Evaluation Board MIC23150-SYMT EV3.3V Fixed Output Evaluation BoardNote:1. Contact Micrel Marketing2. Other voltage options available on request. Contact Micrel.HyperLight Load™ ModeMIC23150 uses a minimum on and off time proprietary control loop (patented by Micrel). When the output voltage falls below the regulation threshold, the error comparator begins a switching cycle that turns the PMOS on and keeps it on for the duration of the minimum-on-time. This increases the output voltage. If the output voltage is over the regulation threshold, then the error comparator turns the PMOS off for a minimum-off-time until the output drops below the threshold. The NMOS acts as an ideal rectifier that conducts when the PMOS is off. Using a NMOS switch instead of a diode allows for lower voltage drop across the switching device when it is on. The asynchronous switching combination between the PMOS and the NMOS allows the control loop to work in discontinuous mode for light load operations. In discontinuous mode, the MIC23150 works in pulse frequency modulation (PFM) to regulate the output. As the output current increases, the off-time decreases, thus provides more energy to the output. This switching scheme improves the efficiency of MIC23150 during light load currents by only switching when it is needed. As the load current increases, the MIC23150 goes into continuous conduction mode (CCM) and switches at a frequency centered at 4MHz. The equation to calculate the load when the MIC23150 goes into continuous conduction mode may be approximated by the following formula:˜˜¯ˆÁÁËÊ¥¥->f L D V V I OUT IN LOAD 2)(As shown in the previous equation, the load at which MIC23150 transitions from HyperLight Load™ mode to PWM mode is a function of the input voltage (V IN ), output voltage (V OUT ), duty cycle (D), inductance (L) and frequency (f). As shown in Figure 1, as the Output Current increases, the switching frequency also increases until theMIC23150 goes from HyperLight Load TMmode to PWM mode at approximately 120mA. The MIC23150 will switch at a relatively constant frequency around 4MHz once the output current is over 120mA.Figure 1. SW Frequency vs. Output CurrentMIC23150 Typical Application CircuitBill of MaterialsItem Part Number Manufacturer Description Qty. C1, C2C1608X5R0J475K TDK(1) 4.7µF Ceramic Capacitor, 6.3V, X5R, Size 06032 R1CRCW06031002K0FKEA Vishay(2)10kΩ, 1%, Size 06031 VLS3010T-1R0N1R9TDK(1)1µH, 1.9A, 60mΩ, L3.0mm x W3.0mm x H1.0mm1 L1VLS4012T-1R0N1R6TDK(1)1µH, 2.8A, 50mΩ, L4.0mm x W4.0mm x H1.2mmDO2010-102ML Coilcraft(3)1µH, 1.8A, 162mΩ, L2.0mm x W2.0mm x H1.0mm U1MIC23150-xYMT Micrel, Inc.(4)4MHz 2A Buck Regulator with HyperLight Load™ Mode1 Notes:1. TDK: .2. Vishay: .3. Coilcraft: .4. Micrel, Inc.: .PCB Layout RecommendationsTop LayerBottom Layer。

IR3621MTRPBF资料

IR3621 & (PbF)Data Sheet No.PD60231 revAIR3621 & (PbF)IR3621 & (PbF)ELECTRICAL SPECIFICATIONSUnless otherwise specified, these specifications apply over Vcc=12V, VcH1=VcH2=V CL =12V and 0°C<T j <125°C.PARAMETERSYMBOL TEST CONDITIONMIN TYP MAX UNITSOutput Voltage Accuracy Feedback VoltageAccuracyUVLO SectionUVLO Threshold - Vcc UVLO Hysteresis - VccUVLO Threshold - VcH1,2UVLO Hysteresis - VcH1,2Supply Current Section Vcc Dynamic Supply Current VcH1 & VcH2 Dynamic Current V CL Dynamic Supply Current Vcc Static Supply Current VcH1/VcH2 Static Current V CL Static Supply Current MLPQTSSOPSupply Ramping UpSupply Ramp Up and Down Supply Ramping UpSupply Ramp Up and Down Freq=300kHz, C L =1500pF Freq=300kHz, C L =1500pF Freq=300kHz, C L =1500pFSS=0V SS=0V SS=0V 0.8010.751015151066V %%%%%%V V V V mA mA mA mA mA mA V Fb1 , V Fb2UVLO V CC UVLO V C H1,2Dyn I CC Dyn I CH Dyn I CL I CCQI CHQI CLQ-1-1.35 -2.5-1.35-1.65-3.04.73.5+1+1.35+1.35+1.35+1.65+1.655.34.0152525151010280.9V REF 0.1-0.110001.25300µA V V V µA µmho µmho µA mV V kHz V %ns %kHz ns V VSS IB SD PG FB1,2L PG (Voltage)I FB1,2g m1g m2I (E/A)1,2V OS(ERR)VP2Freq V RAMP Dmin Puls(ctrl)Dmax Sync(Fs)Sync(puls)Sync(H)Sync(L)220.8V REF 1400140060-40.425515086.52002350.250.95V REF0.5-0.525002500140+4Vcc-234512000.6Soft-Start / SD SectionCharge CurrentShutdown ThresholdPower Good SectionV SENS1,2 Lower Trip PointPGood Output Low VoltageError Amp SectionFb Voltage Input Bias CurrentTransconductance 1Transconductance 2Error Amp Source/Sink CurrentInput Offset Voltage for E/A1,2VP2 Voltage RangeOscillator SectionFrequencyRamp AmplitudeMin Duty CycleMin Pulse WidthMax Duty CycleSynch Frequency RangeSynch Pulse DurationSynch High Level ThresholdSynch Low Level ThresholdSS=0V V SENS1,2 Ramping Down I SINK =2mA SS=3V Fb 1,2 to V REF Note2Rt (SET) to 30.9K Note2Fb=1V F SW =300kHz, Note2Fb=0.6V, F SW =200kHz 20% above free running freq Note1: Cold temperature performance is guaranteed via correlation using statistical quality control. Not 100% tested in production.Tj=25°C-40°C <T j < 125°C 0°C <T j < 125°C 0°C <T j < 125°C -40°C <T j < 125°CTj=25°CIR3621 & (PbF)IR3621 & (PbF)PIN DESCRIPTIONS 12345,236,227,218209,1910,1811,1712,1613,15142425262728Power Good pin. Low when any of the outputs fall 10% below the set voltages. Supply voltage for the internal blocks of the IC. The Vcc slew rate should be <0.1V/us.Output of the internal LDO. Connect a 1.0uF capacitor from this pin to ground. Connecting a resistor from this pin to ground sets the oscillator frequency. Sense pins for OVP and PGood. For current share tie these pins together. Inverting inputs to the error amplifiers. In current sharing mode, Fb1 is con-nected to a resistor divider to set the output voltage and Fb2 is connected to programming resistor to achieve current sharing. In independent 2-channel mode, these pins work as feedback inputs for each channel.Compensation pins for the error amplifiers.These pins provide user programmable soft-start function for each outputs. Connect external capacitors from these pins to ground to set the start up time for each output. These outputs can be shutdown independently by pulling the respective pins below 0.3V. During shutdown both MOSFETs will be turned off. For current share mode SS2 must be floating.A resistor from these pins to switching point will set current limit threshold. Supply voltage for the high side output drivers. These are connected to voltages that must be typically 6V higher than their bus voltages. A 0.1µF high fre-quency capacitor must be connected from these pins to PGND to provide peak drive current capability.Output drivers for the high side power MOSFETs. Note3These pins serve as the separate grounds for MOSFET drivers and should be connected to the system’s ground plane.Output drivers for the synchronous power MOSFETs.Supply voltage for the low side output drivers.The internal oscillator can be synchronized to an external clock via this pin. When pulled High, it puts the device current limit into a hiccup mode. When pulled Low, the output latches off, after an overcurrent event.Non-inverting input to the second error amplifier. In the current sharing mode, it is connected to the programming resistor to achieve current sharing. In inde-pendent 2-channel mode it is connected to V REF pin when Fb2 is connected to the resistor divider to set the output voltage.Reference Voltage. The drive capability of this pin is about 2µA.Analog ground for internal reference and control circuitry.TSSOP MLPQ PIN SYMBOL PIN DESCRIPTION2930311 2,22 3,21 4,20519 6,18 7,17 8,16 10,14 11,13122324262728 9,15,25.32PGoodVccV OUT3RtV SEN2, V SEN1Fb2,Fb1 Comp2, Comp1 SS2 / SDSS1 / SD OCSet2,OCSet1 VcH2, VcH1 HDrv2, HDrv1 PGnd2, PGnd1 LDrv2, LDrv1V CLSyncHiccupV P2V REFGndN/CNote3: The negative voltage at these pins may cause instability for the gate drive circuits. T o prevent this, a low forward voltage drop diode (Schottky) is required between these pins and power ground.No ConnectIR3621 & (PbF)IR3621 & (PbF)Figure 5 - 30A Current Sharing using Inductor sensing(5A/Div)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)For higher efficiency, low ESR capacitors are recom-mended.Choose two Poscap from Sanyo 16TPB47M (16V, 47µF ,70m Ω ) with a maximum allowable ripple current of 1.4A for inputs of each channel.Inductor SelectionThe inductor is selected based on operating frequency,transient performance and allowable output voltage ripple.Low inductor values result in faster response to step load (high ∆i/∆t) and smaller size but will cause larger output ripple due to increased inductor ripple current. As a rule of thumb, select an inductor that produces a ripple current of 10-40% of full load DC.For the buck converter, the inductor value for desired operating ripple current can be determined using the fol-lowing relation:V IN - V OUT = L × ; ∆t = D × ; D =1f SV OUT V IN ∆i ∆t L = (V IN - V OUT )× ---(7)V OUTV IN ×∆i ×f SWhere:V IN = Maximum Input Voltage V OUT = Output Voltage∆i = Inductor Ripple Current f S = Switching Frequency ∆t = Turn On Time D = Duty CycleWhere:∆V O = Output Voltage Ripple ∆i = Inductor Ripple Current∆V O = 3% of V O will result to ESR (2.5V) =16.6m Ω and ESR (1.8V) =16m ΩESR ≤ ---(8)∆V O∆I OThe Sanyo TPC series, Poscap capacitor is a good choice.The 6TPC330M, 330µF, 6.3V has an ESR 40m Ω. Se-lecting three of these capacitors in parallel for 2.5V out-put, results to an ESR of ≅ 13.3m Ω which achieves our low ESR goal. And selecting three of these capacitors in parallel for 1.8V output, results in an ESR of ≅ 13.3m Ωwhich achieves our low ESR goal.The capacitors value must be high enough to absorb the inductor's ripple current.Power MOSFET SelectionThe IR3621 uses four N-Channel MOSFETs. The selec-tion criteria to meet power transfer requirements is based on maximum drain-source voltage (V DSS ), gate-source drive voltage (V GS ), maximum output current, On-resis-tance R DS(ON) and thermal management.The both control and synchronous MOSFETs must have a maximum operating voltage (V DSS ) that exceeds the maximum input voltage (V IN ).Input Capacitor SelectionThe 1800 out of phase will reduce the RMS value of the ripple current seen by input capacitors. This reduces numbers of input capacitors. The input capacitors must be selected that can handle both the maximum ripple RMS at highest ambient temperature as well as the maximum input voltage. The RMS value of current ripple for duty cycles under 50% is expressed by: For ∆i (2.5V) = 45%(I O(2.5V) ), then the output inductor will be:L 4 = 1.1µHFor ∆i (1.8V) = 35%(I O(1.8V) ), then the output inductor will be:L 3 = 1.1µH Panasonic provides a range of inductors in different val-ues and low profile for large currents.Output Capacitor SelectionThe criteria to select the output capacitor is normally based on the value of the Effective Series Resistance (ESR). In general, the output capacitor must have low enough ESR to meet output ripple and load transient requirements, yet have high enough ESR to satisfy sta-bility requirements. The ESR of the output capacitor is calculated by the following relationship: I RMS = (I 12D 1(1-D 1)+I 22D 2(1-D 2)-2I 1I 2D 1D 2) --- (6)Where:I RMS is the RMS value of the input capacitor current D 1 and D 2 are the duty cycle for each output I 1 and I 2 are the current for each output For this application the I RMS =4.8A(ESL, Equivalent Series Inductance is neglected)Choose ETQP6F1R1BFA (1.1µH, 16A, 2.2m Ω) both for L 3 and L 4.For 2-phase application, equation (7) can be used for calculating the inductors value. In such case the induc-tor ripple current is usually chosen to be between 10-40% of maximum phase current.The gate drive requirement is almost the same for both MOSFETs. Logic-level transistors can be used and cau-tion should be taken with devices at very low Vvent undesired turn-on of the complementary MOSFET which results in a shoot-through.IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)TYPICAL OPERATING WAVEFORMSTest Conditions:V IN=12V, V OUT1=2.5V, I OUT1=0-10A, V OUT2=1.8V, I OUT2=0-10A, Fs=400kHz, T A=Room Temp, No Air Flow Unless otherwise specified.Figure 21 - Start up waveforms for 2.5V output Ch1: Vin, Ch2: Vout3, Ch3: SS1, Ch4:Vo1 (2.5V)Figure 22 - Start up waveforms for 1.8V output Ch1: Vin, Ch2: Vout3, Ch3: SS2, Ch4:Vo2 (1.8V)Figure 23 - Start up waveforms Ch1: Vin, Ch2: Vout3, Ch3: VrefFigure 24 - Vo1, Vo2 and PGoodCh1: Vin, Ch2: Vo1, Ch3: Vo2, Ch4: PGoodIR3621 & (PbF)TYPICAL OPERATING WAVEFORMSTest Conditions:V IN =12V, V OUT1=2.5V, I OUT1=0-10A, V OUT2=1.8V, I OUT2=0-10A, Fs=400kHz, Ta=Room Temp, No Air FlowUnless otherwise specified.Figure 25 - 2.5V outputCh1: Vin, Ch2: SS1, Ch3: Vo1, Ch4: PGoodFigure 26 - 1.8V outputCh1: Vin, Ch2: SS2, Ch3: Vo2, Ch4: PGoodFigure 27 - Gate waveforms with 180oout of phaseCh1: Hdrv1, Ch2: Hdrv2Figure 28 - 2.5V WaveformsCh1: Hdrv1, Ch2: Ldrv1, Ch3: Lx1, Ch4: Inductor CurrentIR3621 & (PbF)Figure 29 - 2.5V WaveformsCh1: Hdrv2, Ch2: Ldrv2, Ch3: Lx2, Ch4: Inductor Current Figure 30 - 1.8V output shortedCh1: Vo1, Ch2: SS2, Ch3: Inductor CurrentFigure 31 - 2.5V output shortedCh1: Vo2, Ch2: SS1, Ch3: Inductor CurrentFigure 32 - Prebias Start upCh1: SS1, Ch2: Vo1, Ch3: SS2, Ch4:Vo2TYPICAL OPERATING WAVEFORMSTest Conditions:V IN =12V, V OUT1=2.5V, I OUT1=0-10A, V OUT2=1.8V, I OUT2=0-10A, Fs=400kHz, Ta=Room Temp, No Air Flow Unless otherwise specified.IR3621 & (PbF)Figure 33 - SS1 pin shorted to GndCh1: SS1, Ch2: Hdrv1, Ch3: Ldrv1, Ch4:Vo2Figure 34 - SS2 pin shorted to GndCh1: SS2, Ch2: Hdrv2, Ch3: Ldrv2, Ch4:Vo1Figure 35 - External Synchronization Ch1: External Clock, Ch2: Hdrv1, Ch3: Hdrv2TYPICAL OPERATING WAVEFORMSTest Conditions:V IN =12V, V OUT1=2.5V, I OUT1=0-10A, V OUT2=1.8V, I OUT2=0-10A, Fs=400kHz, Ta=Room Temp, No Air Flow Unless otherwise specified.IR3621 & (PbF)TYPICAL OPERATING WAVEFORMSTest Conditions:V IN =12V, V OUT1=2.5V, I OUT1=0-10A, V OUT2=1.8V, I OUT2=0-10A, Fs=400kHz, Ta=Room Temp, No Air FlowUnless otherwise specified.Figure 36 - Load Transient Respons for Vo1(Io=0 to 10A)Ch1: Vo1, Ch4:Io1Figure 37 - Load Transient Respons for Vo1(Io=10 to 0A)Ch1: Vo1, Ch4: Io1Figure 39 - Load Transient Respons for Vo2(Io=10 to 0A)Ch1: Vo2, Ch4: Io2Figure 38 - Load Transient Respons for Vo2(Io=0 to 10A)Ch1: Vo2, Ch4: Io2IR3621 & (PbF)IR3621 & (PbF)IR3621 & (PbF)。

TI UC1715-SP 互补型开关驱动器说明书

W PACKAGEUC1715-SP ZHCSAU7–MAY2013互补型开关场效应晶体管(FET)驱动器查询样品:UC1715-SP特性•单输入(脉宽调制(PWM)和晶体管-晶体管逻辑电路(TTL)兼容)•高电流功率FET驱动器,1A拉电流/2A灌电流•辅助输出FET驱动器,0.5A拉电流/1A灌电流•电源与独立可编程辅助输出间的时间延迟范围50ns至700ns•针对每个输出可单独配置时间延迟或真正零电压运行•开关频率达到1MHz•典型值为50ns的传播延迟•ENBL引脚激活220μA睡眠模式•睡眠模式中电源输出低电平有效•同步整流器驱动器说明UC1715是一款被设计成为互补型开关提供驱动波形的高速驱动器。

互补型开关配置通常用于同步整流电路和有源钳位/复位电路,它可提供零电压切换。

为了便捷软开关转换,这个驱动器提供两个输出波形间的独立可编程延迟。

此延迟引脚还具有真正零电压感测功能,这个功能可在采用零电压时实现相应开关的立即激活。

这个器件的运行需要一个PWM类型输入,而且此器件可与常见的PWM控制器对接。

ORDERING INFORMATION(1)T J PACKAGE ORDERABLE PART NUMBER TOP-SIDE MARKING –55°C to125°C CFP(W)5962-0052102VFA5962-0052102VFA(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIweb site at .Please be aware that an important notice concerning availability,standard warranty,and use in critical applications ofTexas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.UC1715-SPZHCSAU7–DEVICE INFORMATIONPIN FUNCTIONSPINI/O DESCRIPTIONNAME NO.1,7,8,N/C9,10,-N/C pins are not bonded out.External connections will not affect device functionality.12,13The V CC input range is from7V to20V.This pin should be bypassed with a capacitor to GND consistent with V CC2Ipeak load current demands.The PWR output waits for the T1delay after the INPUT’s rising edge before switching on,but switches offimmediately at INPUT’s falling edge(neglecting propagation delays).This output is capable of sourcing1-A PWR3Oand sinking2-A of peak gate drive current.PWR output includes a passive,self-biased circuit which holds thispin active low,when ENBL≥0.8V regardless of VCC’s voltage.This is the reference pin for all input voltages and the return point for all device currents.It carries the full GND4,5-peak sinking current from the outputs.Any tendency for the outputs to ring below GND voltage must bedamped or clamped such that GND remains the most negative potential.The AUX switches immediately at INPUT’s rising edge but waits through the T2delay after INPUT’s falling AUX6edge before switching.AUX is capable of sourcing0.5-A and sinking1-A of drive current.During sleep mode, AUX is inactive with a high impedance.This pin functions in the same way as T1but controls the time delay between PWR turn-off and activation ofthe AUX switch.The resistor on this pin sets the charging current on internal timing capacitors to provide independent timecontrol.The nominal voltage level at this pin is3V and the current is internally limited to1mA.The total delay T211from INPUT to output includes a propagation delay in addition to the programmable timer but since thepropagation delays are approximately equal,the relative time delay between the two outputs can be assumedto be solely a function of the programmed delays.The relationship of the time delay vs.RT is shown in theTypical Characteristics curves.The input switches at TTL logic levels(approximately1.4V)but the allowable range is from0V to20V,allowing direct connection to most common IC PWM controller outputs.The rising edge immediately switchesthe AUX output,and initiates a timing delay,T1,before switching on the PWR output.Similarly,the INPUTfalling edge immediately turns off the PWR output and initiates a timing delay,T2,before switching the AUX INPUT14Ioutput.It should be noted that if the input signal comes from a controller with FET drive capability,this signal providesanother option.INPUT and PWR provide a delay only at the leading edge while INPUT and AUX provide thedelay at the trailing edge.A resistor to ground programs the time delay between AUX switch turn-off and PWR turn-on.The resistor on this pin sets the charging current on internal timing capacitors to provide independent timecontrol.The nominal voltage level at this pin is3V and the current is internally limited to1mA.The total delay T115from INPUT to output includes a propagation delay in addition to the programmable timer but since thepropagation delays are approximately equal,the relative time delay between the two outputs can be assumedto be solely a function of the programmed delays.The relationship of the time delay vs.RT is shown in theTypical Characteristics curves.The ENBL input switches at TTL logic levels(approximately1.2V),and its input range is from0V to20V. ENBL16I The ENBL input will place the device into sleep mode when it is a logical low.The current into VCC during the sleep mode is typically220μA.INPUTT1T2 ENBLAUXPWRVCCGND UC1715-SP ZHCSAU7–MAY2013BLOCK DIAGRAMABSOLUTE MAXIMUM RATINGS(1)(2)over operating free-air temperature range(unless otherwise noted)V CC Supply voltage20VContinuous-100mA Power driverPeak(3)-1AI OHContinuous-100mA Auxiliary driverPeak(3)-500mAContinuous100mA Power driverPeak(3)2AI OLContinuous100mA Auxiliary driverPeak(3)1AV I Input voltage range(INPUT,ENBL)–0.3V to20VT J Maximum operating junction temperature150°CT stg Storage temperature range–65°C to150°CT lead Maximum lead temperature(soldering,10seconds)300°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)All voltages are with respect to ground.Currents are positive into,negative out of the specified terminal.(3)RMS drive current on any pin to be restricted to672mA.UC1715-SPZHCSAU7–THERMAL INFORMATIONUC1715-SPTHERMAL METRIC(1)W UNITS16PINSθJA Junction-to-ambient thermal resistance(2)72.9θJC Junction-to-case thermal resistance(3)8.25°C/WθJB Junction-to-board thermal resistance(4)43.4(1)有关传统和新的热度量的更多信息,请参阅IC封装热度量应用报告,SPRA953。

dq轴电压与直流侧电压关系

dq轴电压与直流侧电压关系直流(Direct Current,简称DC)电压是指电流方向不变的电压信号。

它是通过在一个电源中产生直流电流,并在电路中保持恒定的电压。

在直流电压源的引导下,产生出的电流在电路中向一个方向流动。

与直流电流相对,交流(Alternating Current,简称AC)电压是指电流方向周期性变化的电压信号。

交流电压是由发电机、变压器等电源产生的,其电流按照一定的频率无规律地在正负方向之间来回变化。

在工程实践中,有时需要将交流电压转化为直流电压以供电路中的某些元器件使用。

为此,我们需要使用交流与直流之间的电力转换方式。

其中,一种常用的转换方式是使用电力电子器件实现直流电压的获取和整流。

使用电力电子器件来实现直流电压的获取,其中最常见的方式是使用直流电压源与交流电源相连接,通过电器设备将交流电源经过整流、滤波和调整电压等处理步骤得到直流电压。

电力电子器件常用的有整流二极管、整流桥、磁阻器、电容器等。

对于由直流电压源提供的直流电压,其电压幅值是恒定的,不随时间变化。

而对于由交流电压源产生的交流电压,其幅值大小和信号的频率有关。

在实际应用中,为了满足电路的需要,可能需要对直流电压进行调节或变换。

这时,可以使用变压器、稳压二极管、开关电源等电器设备对直流电压进行调整。

变压器是一种常用的电力转换设备,在电路中用来改变电压的大小。

它通过改变绕组的匝数比例来改变输入和输出的电压。

变压器能够使电压升高或降低,但频率不会变化。

稳压二极管也是一种常用的电子设备,可以将输入的直流电压稳定在一定的范围内。

开关电源是一种将交流电转换成直流电的高效率电源。

它通过开关电子器件的转换来实现电能的转化和调整。

开关电源可以根据需要,通过控制开关器件的开合来调整输出电压的大小。

总之,在电路中,直流电压与直流电源、交流电压与交流电源之间存在一定的关系。

直流电压可以通过交流电压转换而来,而交流电压也可以通过相应的设备转换成直流电压。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。