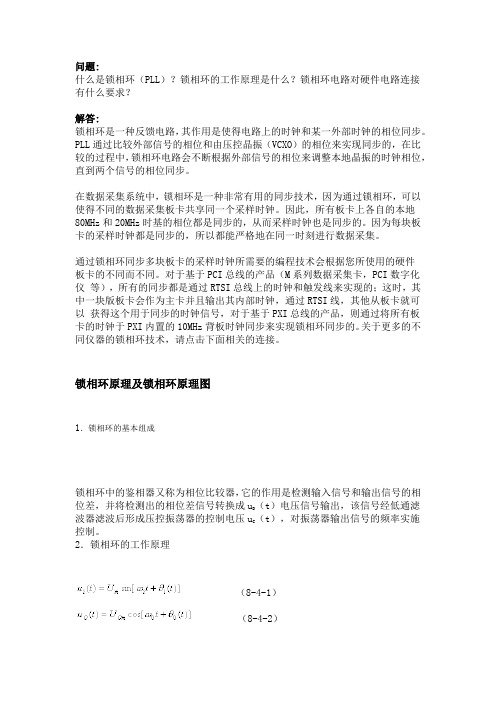

过零比较和锁相环相位比较器电路原理图如图

锁相环原理及锁相环原理图

问题:什么是锁相环(PLL)?锁相环的工作原理是什么?锁相环电路对硬件电路连接有什么要求?解答:锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。

PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。

因此,所有板卡上各自的本地80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。

因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。

通过锁相环同步多块板卡的采样时钟所需要的编程技术会根据您所使用的硬件板卡的不同而不同。

对于基于PCI总线的产品(M系列数据采集卡,PCI数字化仪等),所有的同步都是通过RTSI总线上的时钟和触发线来实现的;这时,其中一块版板卡会作为主卡并且输出其内部时钟,通过RTSI线,其他从板卡就可以获得这个用于同步的时钟信号,对于基于PXI总线的产品,则通过将所有板卡的时钟于PXI内置的10MHz背板时钟同步来实现锁相环同步的。

关于更多的不同仪器的锁相环技术,请点击下面相关的连接。

锁相环原理及锁相环原理图1.锁相环的基本组成锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相(t)电压信号输出,该信号经低通滤位差,并将检测出的相位差信号转换成uD波器滤波后形成压控振荡器的控制电压u(t),对振荡器输出信号的频率实施C控制。

2.锁相环的工作原理(8-4-1)(8-4-2)0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D 为:C (t )。

即u C (t )为:(8-4-3)i 为输入信号的瞬时振荡角频率,θi (t )和θO (t )分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即 (8-4-4)d 为(8-4-5)(8-4-6)c (t )为恒定值。

过零比较和锁相环相位比较器电路原理图如图

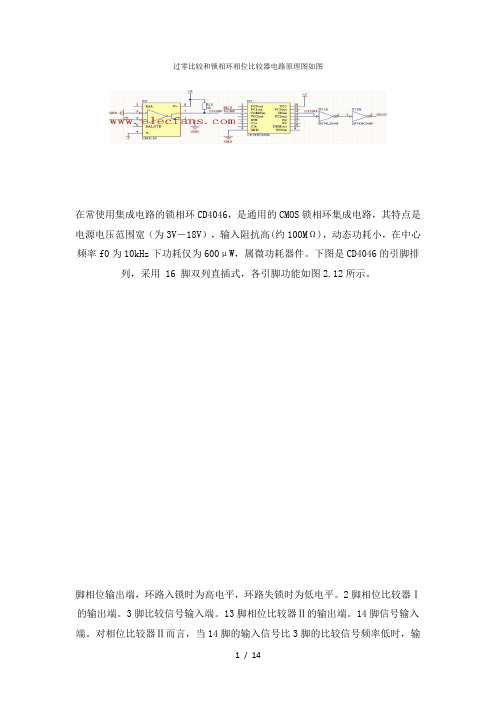

过零比较和锁相环相位比较器电路原理图如图过零比较和锁相环相位比较器电路原理图如图现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V,18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

下图是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如图2.12所示。

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。

2脚相位比较器?的输出端。

3脚比较信号输入端。

13脚相位比较器?的输出端。

14脚信号输入端。

对相位比较器?而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器?输出的为正脉冲,当相位超前时则输出为负脉冲。

在这两种情况下,从1脚都有与上述正、负脉冲宽度clearly, for maintenance management. 4. install (1) all sorts of switches, socketsand other equipment should be installed firmly, position accurate, when installing rocker panel, switches, switch should be consistent, generally up to "close" down to "off" switch should cut off the line. Switches the elevation and location of the socket should conform to the drawings, the same interior height difference should not be greater than 5mm. (2) liquid level automatic control device used in a variety of angle brackets, there should be galvanized. (3) fixed lamp hanging boxes are plastic with rotary table round table. (4) light bulb capacity of 100W or less, available resin lamp, 100W and the tide sealed lamps, porcelain lamps. (5) the wiring inside the lamp shall not be less than 0.4mm2 wires. (6) the chandelier with a weight of more than 3kg, the embedded hook-bolts, install lighting in the brick or concrete structures, should use expansion bolts or plastic tube, ban the use of wooden wedges instead. (7) the ceiling mounted light fixtures, border of the shade should cover Panel joints and snapped the ceiling panel, determine the size lamp open position, strictly according to the drawings. (8) the lamps arranged orderly, symmetrical when installing the vertical and horizontal center lines should be on the same line, deviation is less than 5mm. (9) the emergency lighting installation: according to the design and specifications to determine location of evacuation lighting, signs should相同的负脉冲产生。

过零比较和锁相环相位比较器电路原理图如图

过零比较和锁相环相位比较器电路原理图如图在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

下图是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如图2.12所示。

脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。

在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。

从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。

而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。

上述波形如图2.13所示。

由此可见,从1脚输出信号是负脉冲还是固定高电平就可以判断两个输入信号的情况了。

2.13 比较器输出波形图电压比较器可以看作是放大倍数接近“无穷大”的运算放大器。

电压比较器的功能:比较两个电压的大小(用输出电压的高或低电平,表示两个输入电压的大小关系):当”+”输入端电压高于”-”输入端时,电压比较器输出为高电平;当”+”输入端电压低于”-”输入端时,电压比较器输出为低电平;电压比较器的作用:它可用作模拟电路和数字电路的接口,还可以用作波形产生和变换电路等。

利用简单电压比较器可将正弦波变为同频率的方波或矩形波。

简单的电压比较器结构简单,灵敏度高,但是抗干扰能力差,因此我们就要对它进行改进。

改进后的电压比较器有:滞回比较器和窗口比较器。

运放,是通过反馈回路和输入回路的确定“运算参数”,比如放大倍数,反馈量可以是输出的电流或电压的部分或全部。

(完整word版)锁相环的基本原理和模型

1.锁相环的基本原理和模型在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。

一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。

图1-1 基本锁相环结构鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。

PLL 的每个部分都是非线性的,但是这样不便于分析设计。

因此可以用近似的线性特性来表示PLL 的控制模型。

鉴相器传递函数为:)(Xo Xi Kd Vd -=压控振荡器可以等效为一个积分环节,因此其传递函数为:SKo 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。

综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下:Ss F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,)()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。

2.鉴相器的实现方法鉴相器的目的是要尽可能的得到准确的相位误差信息。

可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。

一般也可以使用乘法鉴相器。

通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。

在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。

同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。

过零比较器

一、过零比较器过零比较器,顾名思义,其阈值电压U T=0V。

电路如图(a)所示,集成运放工作在开环状态,其输出电压为+U OM或-U OM。

当输入电压u I<0V时,U O=+U OM;当输入电压u I>0V 时,U O=-U OM。

因此,电压传输特性如图(b)所示。

为了限制集成运放的差模输入电压,保护其输入级,可加二极管限幅电路,如右图所示。

★两只稳压管稳压值不同在实用电路中为了满足负载的需要,常在集成运放的输出端加稳压管限幅电路,从而获得合适的U OH和U OL,如图(725)(a)所示。

图中R为限流电阻,两只稳压管的稳定电压均应小于集成运放的最大输出电压U OM。

设稳压管D Z1的稳定电压为U Z1,稳压管D Z2的稳定电压为U Z2,U Z1和U Z2的正向导通电压均为U D。

当u I<0时,由于集成运放的输出电压u/O=+U OM,D Z1使工作在稳压状态,D Z2工作在正向导通状态,所以输出电压u O=U OH=(U Z1+U D)当u I>0时,由于集成运放的输出电压u/O=-U OM,D Z2使工作在稳压状态,D Z1工作在正向导通状态,所以输出电压u O=U OL=-(U Z2+U D)★两只稳压管稳压值相同若要求,U Z1=U Z2则可以采用两只特性相同而又制作在一起的稳压管,其符号如图(b)所示,稳定电压标为±U Z。

当u I<0时,u O=U OH=U Z;当u I>0时,u O=U OL=-U Z。

★稳压管接在反馈通路中限幅电路的稳压管还可跨接在集成运放的输出端和反相输入端之间,成运放必然工作在开环状态,输出电压不是+U OM,就是-U OM。

这样,必将导致稳压管击穿而工作在稳压状态,D Z构成负反馈通路,使反相输入端为“虚地”,限流电阻上的电流i R等于稳压管的电流i Z,输出电压u O=±U Z。

电路优点:◆由于集成运放的净输入电压和净输入电流均近似为零,从而保护了输入级;◆由于集成运放并没有工作到非线性区,因而在输入电压过零时,其内部的晶体管不需要从截止区逐渐进入饱和区,或从饱和区逐渐进入截止区,所以提高了输出电压的变化速度。

锁相环的基本原理和模型

1.锁相环的基本原理和模型在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。

一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。

图1-1 基本锁相环结构鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。

PLL 的每个部分都是非线性的,但是这样不便于分析设计。

因此可以用近似的线性特性来表示PLL 的控制模型。

鉴相器传递函数为:)(Xo Xi Kd Vd -=压控振荡器可以等效为一个积分环节,因此其传递函数为:SKo 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。

综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下:S s F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,)()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。

2.鉴相器的实现方法鉴相器的目的是要尽可能的得到准确的相位误差信息。

可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。

一般也可以使用乘法鉴相器。

通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。

在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。

同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。

电压比较器(过零比较器)

输特性曲线 2、 反向滞回比较器 (1)连接图 2(a)所示实验电路,接通直流电源,测出 Uo 由高电平变为低电 平时的阈值 (2)同上,测出 Uo 由低电平变为高电平时的阈值 (3)将信号发生器接入 Ui,并使之输出频率为 500Hz,电压有效值为 1V 的正 弦波信号,用示波器观察比较器的输入 Ui 与输出 Uo 波形并记录 3、 同向滞回比较器 (1)连接图 3 所示实验电路,参照反向滞回比较器的测试方法自拟实验步骤及 方法 (2)将实验结果与反向滞回比较器的理论分析结果进行比较,分析误差产生原 因

(4)改变信号发生器的输出电压 Ui 幅值,通过观察示波器 Uo 变化可知电压传 输曲线如下图所示

3

当 Ui<0 时,由于集成运放的输出电压 Uo ' =+Uom,使稳压管 D2 工作在稳压 状态(两只稳压管的稳定电压均小于集成运放的最大输出电压 Uom) ,所以输出 电压 Uo=Uz;当 Ui>0 时,由于集成运放的输出电压 Uo ' =-Uom,使稳压管 D1 工作在稳压状态,所以输出电压 Uo=-Uz。 电路图中所选的稳压管的稳压电压为 6.2V,但实际测出的电压输出值 6.91V 略大于此值。当 Ui<0 时,稳压管 D2 工作在稳压状态,稳压管 D1 工作在正向导 通状态,所以使输出电压 Uo=Uz+UD(UD 为稳压管的正向导通电压) ,因而实际 测量值略高于稳压管的稳压值。 2、 反向滞回比较器 (1)连接图 2(a)所示实验电路,接通直流电源,测出 Uo 由高电平变为低电 平时的阈值 实验结果:UTH1 =625mV 仿真结果:UTH1=619.004mV 理论结果:UTH1 =R2Uz /(R2+R3)=564mV 将实验结果、仿真结果与理论结果的对比如下表所示 实验结果 仿真结果 理论结果 阈值 UTH1 625mV 619.004mV 564mV 与理论值的误差 10.8% 9.8% 0 (2)测出 Uo 由低电平变为高电平时的阈值 实验结果:UTH2= 660mV 仿真结果:UTH2= 672.934mV 理论结果:UTH2 = R2Uz /(R2+R3)= 564mV 将实验结果、仿真结果与理论结果的对比如下表所示 实验结果 仿真结果 理论结果 660mV 672.034mV 564mV 阈值 UTH2 与理论值的误差 17.0% 19.2% 0 (3)将信号发生器接入 Ui,并使之输出频率为 500Hz,电压有效值为 1V 的正 弦波信号,用示波器观察比较器的输入 Ui 与输出 Uo 波形如下

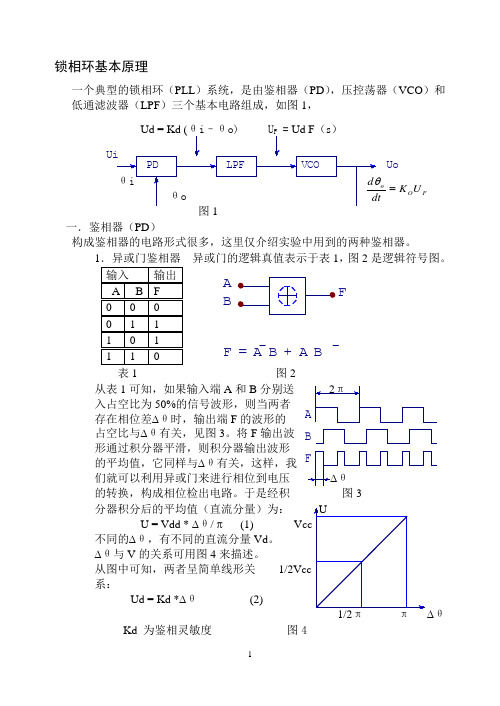

锁相环基本原理

锁相环基本原理一个典型的锁相环(PLL )系统,是由鉴相器(PD ),压控荡器(VCO )和低通滤波器(LPF )三个基本电路组成,如图1,Ud = Kd (θi –θo) U F = Ud F (s )θi θo图1一.鉴相器(PD )构成鉴相器的电路形式很多,这里仅介绍实验中用到的两种鉴相器。

异或门的逻辑真值表示于表1,图2是逻辑符号图。

表1 图2从表1可知,如果输入端A 和B 分别送 2π 入占空比为50%的信号波形,则当两者存在相位差∆θ时,输出端F 的波形的 占空比与∆θ有关,见图3。

将F 输出波 形通过积分器平滑,则积分器输出波形 的平均值,它同样与∆θ有关,这样,我 们就可以利用异或门来进行相位到电压 ∆θ 的转换,构成相位检出电路。

于是经积 图3 分器积分后的平均值(直流分量)为: UU = Vdd * ∆θ/ π (1) Vcc不同的∆θ,有不同的直流分量Vd 。

∆θ与V 的关系可用图4来描述。

从图中可知,两者呈简单线形关 1/2Vcc 系:Ud = Kd *∆θ (2)1/2π π ∆θ Kd 为鉴相灵敏度 图4FO oU K dtd =θVP D L PF V CO U iU o VA B F__F = A B + A B F B A2. 边沿触发鉴相器 前已述及,异或门相位比较器在使用时要求两个作比较的信号必须是占空比为50%的波形,这就给应用带来了一些不便。

而边沿触发鉴相器是通过比较两输入信号的上跳边沿(或下跳边沿)来对信号进行鉴相,对输入信号的占空比不作要求。

二. 压控振荡器(VCO )压控振荡器是振荡频率ω0受控制电压U F (t )控制的振荡器,即是一种电压——频率变换器。

VCO 的特性可以用瞬时频率ω0(t )与控制电压U F (t )之间的关系曲线来表示。

未加控制电压时(但不能认为就是控制直流电压为0,因控制端电压应是直流电压和控制电压的叠加),VCO 的振荡频率,称为自由振荡频率ωom ,或中心频率,在VCO 线性控制范围内,其瞬时角频率可表示为: ωo (t )= ωom + K 0 U F (t )式中,K 0——VCO 控制特性曲线的斜率,常称为VCO 的控制灵敏度,或称压控灵敏度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

过零比较和锁相环相位比较器电路原理图如图现在常使用集成电路的锁相环CD4046,是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

下图是CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如图2.12所示。

1脚相位输出端,环路入锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。

在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。

从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。

而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。

上述波形如图2.13所示。

由此可见,从1脚输出信号是负脉冲还是固定高电平就可以判断两个输入信号的情况了。

图2.13 比较器输出波形图电压比较器可以看作是放大倍数接近“无穷大”的运算放大器。

电压比较器的功能:比较两个电压的大小(用输出电压的高或低电平,表示两个输入电压的大小关系):当”+”输入端电压高于”-”输入端时,电压比较器输出为高电平;当”+”输入端电压低于”-”输入端时,电压比较器输出为低电平;电压比较器的作用:它可用作模拟电路和数字电路的接口,还可以用作波形产生和变换电路等。

利用简单电压比较器可将正弦波变为同频率的方波或矩形波。

简单的电压比较器结构简单,灵敏度高,但是抗干扰能力差,因此我们就要对它进行改进。

改进后的电压比较器有:滞回比较器和窗口比较器。

运放,是通过反馈回路和输入回路的确定“运算参数”,比如放大倍数,反馈量可以是输出的电流或电压的部分或全部。

而比较器则不需要反馈,直接比较两个输入端的量,如果同相输入大于反相,则输出高电平,否则输出低电平。

电压比较器输入是线性量,而输出是开关(高低电平)量。

一般应用中,有时也可以用线性运算放大器,在不加负反馈的情况下,构成电压比较器来使用。

可用作电压比较器的芯片:所有的运算放大器。

常见的有LM324 LM358 uA741 TL081\2\3\4 OP07 OP27,这些都可以做成电压比较器(不加负反馈)。

LM339、LM393是专业的电压比较器,切换速度快,延迟时间小,可用在专门的电压比较场合,其实它们也是一种运算放大器。

关于比较器滞回的讨论需要从“滞回”的定义开始, 与许多其它技术术语一样, “滞回”源于希腊语, 含义是“延迟”或“滞后”, 或阻碍前一状态的变化。

工程中, 常用滞回描述非对称操作, 比如, 从A到B和从B 到A是互不相同。

在磁现象、非可塑性形变以及比较器电路中都存在滞回。

绝大多数比较器中都设计带有滞回电路, 通常滞回电压为5mV到10mV。

内部滞回电路可以避免由于输入端的寄生反馈所造成的比较器输出振荡。

但是内部滞回电路虽然可以使比较器免于自激振荡, 却很容易被外部振幅较大的噪声淹没。

这种情况下需要增加外部滞回, 以提高系统的抗干扰性能。

首先, 看一下比较器的传输特性。

图1所示是内部没有滞回电路的理想比较器的传输特性, 图2所示为实际比较器的传输特性。

从图2可以看出, 实际电压比较器的输出是在输入电压(VIN)增大到2mV时才开始改变。

图1. 理想比较器的传输特性图2. 实际比较器的传输特性运算放大器在开环状态下可以用作比较器, 但是一旦输入信号中有少量的噪声或干扰, 都将会在两个不同的输出状态之间产生不期望的频繁跳变(图3)。

用带有内部滞回电路的比较器代替开环运算放大器能够抑制输出的频繁跳变和振荡。

或在比较器的正反馈电路中增加外部滞回电路, 正反馈的作用是确保输出在一个状态到另一个状态之间快速变化, 使比较器的输出的模糊状态时间达到可以忽略的水平, 如果在正反馈中加入滞回电路可减缓这种频繁跳变。

图3. 无滞回电路时比较器输出的模糊状态和频繁跳变举个例子, 考虑图4所示简单电路, 其传输特性如图5所示。

比较器的反相输入电压从0开始线性变化, 由分压电阻R1、R2构成正反馈。

当输入电压从1点开始增加(图6), 在输入电压超过同相阈值VTH+ = VCCR2/(R1 + R2)之前, 输出将一直保持为VCC。

在阈值点, 输出电压迅速从VCC跳变为VSS, 因为, 此时反相端输入电压大于同相端的输入电压。

输出保持为低电平, 直到输入经过新的阈值点5 , VTH- = VSSR2/(R1 + R2)。

在5点, 输出电压迅速跳变回VCC, 因为这时同相输入电压高于反相输入电压。

图4. 具有滞回的简单电路图5. 图4电路的传输特性图6. 图4电路的输入/输出电压波形图4所示电路中的输出电压VOUT与输入电压VIN的对应关系表明, 输入电压至少变化2VTH时, 输出电压才会变化。

因此, 它不同于图3的响应情况(放大器无滞回), 即对任何小于2VTH的噪声或干扰都不会导致输出的迅速变化。

在实际应用中, 正、负电压的阈值可以通过选择适合的反馈网络设置。

其它设置可以通过增加不同阈值电压的滞回电路获得。

图7电路使用了两个MOSFET和一个电阻网络调节正负极性的阈值。

与图4所示比较器不同, 电阻反馈网络没有加载到负载环路, 图8给出了输入信号变化时的输出响应。

图7. 通过外部MOSFET和电阻构成滞回电路图8. 图7电路的输入/输出电压波形比较器内部的输出配置不同, 所要求的外部滞回电路也不同。

例如, 具有内部上拉电阻的比较器, 可以在输出端和同相输入端直接加入正反馈电阻。

输入分压网络作用在比较器的同相输入端, 反相输入电压为一固定的参考电平(如图9)。

图9. 在带有上拉电阻的比较器中加滞回电路如上所述, 具有内部滞回的比较器提供两个门限:一个用于检测输入上升电压(VTHR),一个用于检测输入下降电压(VTHF), 对应于图8的VTH1和VTH2。

两个门限的差值为滞回带(VHB)。

当比较器的输入电压相等时, 滞回电路会使一个输入迅速跨越另一输入, 从而使比较器避开产生振荡的区域。

图10所示为比较器反相输入端电压固定, 同相输入端电压变化时的工作过程, 交换两个输入可以得到相似波形, 但是输出电压极性相反。

图10. 图9电路的输入/输出电压波形根据输出电压的两个极限值(两个电源摆幅), 可以很容易地计算反馈分压网络的电阻值。

内部有4mV滞回和输出端配有上拉电阻的比较器-- 如Maxim公司的MAX9015、MAX9017和MAX9019等。

这些比较器设计用于电压摆幅为VCC和0V的单电源系统。

可以按照以下步骤, 根据给定的电源电压、电压滞回(VHB)和基准电压(VREF), 选择并计算需要的元件:第1步选择R3, 在触发点流经R3的电流为(VREF - VOUT)/R3。

考虑到输出的两种可能状态, R3由如下两式求得:R3 = VREF/IR3和R3 = (VCC - VREF)/IR3.取计算结果中的较小阻值, 例如, VCC = 5V, IR3 = 0.2µA, 使用MAX9117比较器(VREF = 1.24V), 则计算结果为6.2M和19M, 选则R3为6.2M。

第2步选择滞回电压(VHB)。

在本例中, 选择滞回电压为50mV。

第3步R1可按下式计算。

对于这个例子, R1的值为:第4步输入VIN上升门限(VTHR)的选择, 例如:在该门限点, 当输入电压VIN超过阈值时, 比较器输出由低电平变到高电平。

本例中, 选择VTHR = 3V。

第5步计算R2, R2可按下式计算:本例中, R2的标准值为44.2k。

第6步按如下步骤验证电压和滞回电压:VIN上升门限= 2.992V, 等于VREF乘以R1, 除以R1、R2和R3并联后的阻值。

VIN下降门限= 2.942V。

因此, 滞回电压= VTHR - VTHF = 50mV.最后, 开漏结构的比较器内部滞回电压为4mV (MAX9016、MAX9018、MAX9020), 需要外接上拉电阻, 如图11所示。

外加滞回可以通过正反馈产生, 但是计算公式与上拉输出的情况稍有不同。

图11. 在输出为开漏结构的比较器中加滞回电路按如下步骤计算电阻值:第1步选择R3, 在IN_+端的漏电流小于2nA, 所以通过R3的电流至少为0.2µA, 以减小漏电流引起的误差。

R3可由R3 = VREF/IR3或R3 = [(VCC - VREF)/IR3] - R4两式求得, 取其较小值。

例如, 使用MAX9118 (VREF=1.24V), VCC = 5V, IR3 = 0.2μA, R4 = 1M, 计算结果为6.2M和18M, 则R3选6.2M。

第2步选择需要的滞回电压(VHB)。

第3步选择R1, R1可按下式计算:在此例中, R1为:第4步选择VIN上升门限(VTHR), 如下式:在该门限点, 当输入电压VIN超过阈值时, 比较器输出由低电平变到高电平。

本例中, 选择VTHR = 3V。

第5步计算R2, 如下式:本例中, R2的标准值为49.9k。

第6步按如下步骤验证触发电压和滞回电压:单限比较器电路图1b为其传输特性。

图3为某仪器中过热检测保护电路。

它用单电源供电,1/4LM339的反相输入端加一个固定的参考电压,它的值取决于R1于R2。

U R=R2/(R1+R2)*U CC。

同相端的电压就等于热敏元件Rt的电压降。

当机内温度为设定值以下时,“+”端电压大于“-”端电压,Uo为高电位。

当温度上升为设定值以上时,“-”端电压大于“+”端,比较器反转,Uo输出为零电位,使保护电路动作,调节R1的值可以改变门限电压,既设定温度值的大小。

图3迟滞比较器图1不难看出,当输出状态一旦转换后,只要在跳变电压值附近的干扰不超过ΔU之值,输出电压的值就将是稳定的。

但随之而来的是分辨率降低。

因为对迟滞比较器来说,它不能分辨差别小于ΔU的两个输入电压值。

迟滞比较器加有正反馈可以加快比较器的响应速度,这是它的一个优点。

除此之外,由于迟滞比较器加的正反馈很强,远比电路中的寄生耦合强得多,故迟滞比较器还可免除由于电路寄生耦合而产生的自激振荡。

图2图3为某电磁炉电路中电网过电压检测电路部分。

电网电压正常时,1/4LM339的U4<2.8V,U5=2.8V,输出开路,过电压保护电路不工作,作为正反馈的射极跟随器BG1是导通的。

当电网电压大于242V 时,U4>2.8V,比较器翻转,输出为0V,BG1截止,U5的电压就完全决定于R1与R2的分压值,为2.7V,促使U4更大于U5,这就使翻转后的状态极为稳定,避免了过压点附近由于电网电压很小的波动而引起的不稳定的现象。