实验6(2) 计数器及应用

实验6-集成计数器

&

G 10 G 17

& 1K

G3

G7 &

& G 18

1

FF 3 & 1J

C1 R

Q3

D3 G4 &

&

G 11 G 19

& 1K

CT P CT T

& 74160

G 20

CO

实验原理

芯片的应用:用74160组成任意模值计数器:

集成计数器可以加适当反馈电路后构成任意模值M计数器。 任意模值M计数器设计原理: 设:计数器的最大计数模值为M,若要得到一个模值为N(<M) 的计数器,则只要在M进制计数器的顺序计数过程中,设 法跳过(M-N)个状态,只在N个状态循环计数,就可以得 到计数模值不大于M的任意模值计数器。 通常中规模集成计数器都有清零、置数等多个控制端,因此 实现任意M计数的基本方法有两种:清零法和置数法。

实验原理

用74160组成任意模值计数器:

② .置数法:置数法和置零法不同,由于置数操作可以在任意

状态下进行,因此计数器不一定从全0状态开始计数。它 可以通过预置功能使计数器从某个预置状态Si开始计数, 计满N个状态后产生置数信号,使计数器进入预置状态Si, 然后再重复前面过程。 同步预置:置数(/LD)有效信号从Si+N-1状态译出,等下一 个CP到来时,才将预置数置入计数器,计数器在Si、 Si+1、┈Si+N-1共N个状态中循环。 异步预置:置数(/LD)有效信号从Si+N状态译出,当Si+N状 态一出现,置数信号立即就将预置数置入计数器,它不 受CP控制,所以Si+N状态只在极短的瞬间出现。稳定状 态中不包含Si+ N。

实验六基于Multisim8的简易数字频率计仿真

闸门

门控

B 放大 整形

S2

1000Tx

1Tx

10Tx 100Tx

÷10

÷10

计数锁存译码 显示系统

÷10

四、实验参考电路

(1)控制时序产生电路

图4.8.5 是由秒脉冲发生器(可由晶体振荡器和 多级分频器组成)和可重触发单稳态74LS123 组成

的控制时序产生电路。秒脉冲发生器产生脉冲宽度 为的定时脉冲,74LS123单稳态电路产生锁存和清 零脉冲。(仿真软件Multisim 8的元件库中,没有 74LS123单稳态电路,可用555定时器组成单稳态 电路)。 5V

4. 闸门电路

闸门电路由与门组成,该电路有两个输入端和一 个输出端,输入端的一端,接门控信号,另一端接 整形后的被测方波信号。闸门是否开通,受门控信 号的控制,当门控信号为高电平“1”时,闸门开启; 而门控信号为低电平“0”时,闸门关闭。显然,只 有在闸门开启的时间内,被测信号才能通过闸门进 入计数器,计数器计数时间就是闸门开启时间。可 见,门控信号的宽度一定时,闸门的输出值正比于 被测信号的频率,通过计数显示系统把闸门的输出 结果显示出来,就可以得到被测信号的频率。

5. 电子计数器测量周期

当被测信号频率比较低时,用测量周期的方法来 测量频率比直接测量频率有更高的准确度和分辨率, 且便于测量过程自动化。该测量方法在许多科学技 术领域中都得到普遍使用。图4.8.4是用电子计数器 测量信号周期的原理方框图。

晶振

Tx

时基 分频

1µs

S1 Tc

10µs 1ms 100µs Tx1

①可控制的计数、锁存、译码显示系统; ②石英晶体振荡器及分频系统(可用Multisim 8中

的函数发生器替代);

实验六 综合实验(8253+(8259+LED))

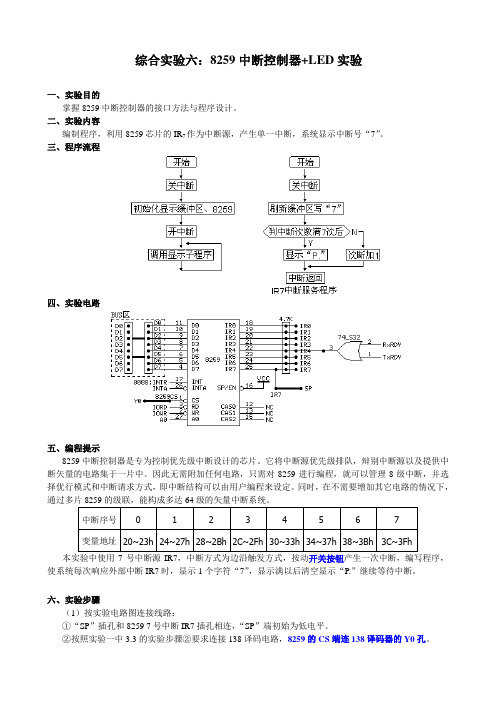

综合实验六:8259中断控制器+LED实验一、实验目的掌握8259中断控制器的接口方法与程序设计。

二、实验内容编制程序,利用8259芯片的IR7作为中断源,产生单一中断,系统显示中断号“7”。

三、程序流程四、实验电路五、编程提示8259中断控制器是专为控制优先级中断设计的芯片。

它将中断源优先级排队,辩别中断源以及提供中断矢量的电路集于一片中。

因此无需附加任何电路,只需对8259进行编程,就可以管理8级中断,并选择优行模式和中断请求方式,即中断结构可以由用户编程来设定。

同时,在不需要增加其它电路的情况下,通过多片8259的级联,能构成多达64级的矢量中断系统。

中断序号0 1 2 3 4 5 6 7变量地址20~23h 24~27h 28~2Bh 2C~2Fh 30~33h 34~37h 38~3Bh 3C~3Fh 本实验中使用7号中断源IR7,中断方式为边沿触发方式,按动开关按钮产生一次中断,编写程序,使系统每次响应外部中断IR7时,显示1个字符“7”,显示满以后清空显示“P.”继续等待中断。

六、实验步骤(1)按实验电路图连接线路:①“SP”插孔和8259 7号中断IR7插孔相连,“SP”端初始为低电平。

②按照实验一中3.3的实验步骤②要求连接138译码电路,8259的CS端连138译码器的Y0孔。

③将8259的单元总线接口D0~D7,用8芯排线或8芯扁平线与数据总线单元D0~D7任一接口相连。

(2)运行实验程序在系统处于命令提示符“P.”状态下(数码显示管显示“P.”),输入3400,按EXEC键显示“P.”。

(3)按动开关按钮,LED数码管从最高位开始依次显示“7”,显示满六位后,最高位显示“P.”继续等待中断。

七、实验程序ZXK EQU 0FFDCHZWK EQU 0FFDDHPort0 EQU 0FFE0HPort1 EQU 0FFE1HCODE SEGMENTASSUME CS:CODE,DS:CODE,ES:CODEORG 3400HH8: JMP P8259LED DB 0C0H,0F9H,0A4H,0B0H,99H,92H,82H,0F8H,80H,90HDB 88H,83H,0C6H,0A1H,86H,8EH,0FFH,0CH,0DEH,0F3HBUF DB ?,?,?,?,?,?P8259: CLICALL WP ;初始化显示“P.”MOV AX,OFFSET INT8259MOV BX,003CHMOV [BX],AXMOV BX,003EHMOV AX,0000HMOV [BX],AXCALL FOR8259mov si,0000hSTICON8: CALL DISJMP CON8;------------------------------------INT8259:cliMOV BX,OFFSET BUFMOV BYTE PTR [BX+SI],07HINC SICMP SI,0007HJZ X59XX59: MOV AL,20HMOV DX,Port0OUT DX,ALmov cx,0050hxxx59: push cxcall dispop cxloop xxx59mov cx,3438hpush cxSTIIRETX59: MOV SI,0000HCALL WPJMP XX59;============================== FOR8259:MOV AL,13HMOV DX,Port0OUT DX,ALMOV AL,08HMOV DX,Port1OUT DX,ALMOV AL,09HOUT DX,ALMOV AL,7FH ;IRQ7OUT DX,ALRET;---------------------------WP: MOV BUF,11H ;初始化显示“P.” MOV BUF+1,10HMOV BUF+2,10HMOV BUF+3,10HMOV BUF+4,10HMOV BUF+5,10HRET;-------------------------------- DIS: MOV CL,20HMOV BX,OFFSET BUFDIS1: MOV AL,[BX]PUSH BXMOV BX,OFFSET LEDXLATPOP BXMOV DX,ZXKOUT DX,ALMOV AL,CLMOV DX,ZWKOUT DX,ALPUSH CXMOV CX,0100HDELAY: LOOP $POP CXCMP CL,01HINC BXSHR CL,1JMP DIS1EXIT: MOV AL,00HMOV DX,ZWKOUT DX,ALRET;--------------------------CODE ENDSEND H8八、扩展练习编制程序,利用8259芯片的IR i作为中断源,产生单一中断,系统显示中断号“i”。

实验六 集成计数器的应用讲课教案

图7-4 74193内部逻辑图

本实验中用到的器件还有7475,它是一个四位的锁存器,管脚图如图7-5所示。 其中D1~D4为数据输入端;G12、G34为锁存控制端,当控制端信号无效时, 数据传送至输出端,控制信号有效时,实现锁存,输出保持不变;Q1~Q4为 数据输出端。

3、利用7490、7475、7448和数码管,搭建一个十进制计数、锁存、译码 、显示电路,验证7448的灭零输入功能和7475的锁存功能,并记录数码 管的显示状态。

4、考虑一下如何用计数器实现分频,用7490完成对TTL方波的二分频和 十分频,并用示波器观察8421码和5421码两种码制的分频效果有什么不 同。

此课件下载可自行编辑修改,仅供参考! 感谢您的支持,我们努力做得更好!谢谢

实验内容:

TTL方波:将波形设置为方波,峰峰值设置为5V,直流偏置设置为2.5V

1、7490为异步计数器,可以用5421和8421两种码制来实现十进制计数, 请用两种码制实现7490的十进制计数,用TTL方波作为计数脉冲,并作出 状态表。

2、计数器7490有两个异步清零控制端R1和R2,试用7490构成六进制( 8421码)和七进制(5421码)计数器,验证起功能并画出连接图。不使 用其他器件,还能构成哪些进制的计数器。

图7-1 7490管脚图

图7-2 7490内部逻辑图

本实验中使用的另外一种计数器为74193,它是一个可预置同步十六 进制加减计数器,管脚图如图7-3所示,内时钟脉冲输入端,分别为向上和向下 计数;DATAA~DATAD为并行数据输入端口;CLEAR为异步清零信号 端;LOAD为置位端,将并行输入端口的数据传送到输出端; BORROW为借位端;CARRY为进位端;QA~QD为计数输出端口。

实验三 计数器及其应用

实验三计数器及其应用

计数器是一种能够在一定条件下,按照一定规律对数字进行计数的设备。

计数器能够进行简单的数学计算,也可以进行复杂的计数任务。

计数器的种类很多,最常见的是二进制计数器、BCD(二进制编码十进制)计数器、同步计数器和异步计数器等。

应用领域非常广泛,例如在电子钟、计时器、计步器、计量仪表、频率计等电子设备中都有广泛的使用。

同时,在数字系统中,计数器也是一个非常重要的组成部分。

在数字处理器芯片、数字信号处理器、编码器/解码器以及FPGA等数字系统中,都需要用到计数器。

此外,在编写程序时,计数器也是一个非常有用的工具。

我们可以使用计数器来计算循环次数、分析代码执行时间等。

总之,计数器是一个非常重要的工具,具有广泛的应用领域。

对于电子工程师和编程人员来说,熟练掌握计数器的原理、种类和应用是非常重要的。

数电集成电路多种计数器综合应用实验的结论及思考

数电集成电路多种计数器综合应用实验的结论及思考一、引言数电集成电路是现代电子技术的重要组成部分,而计数器则是其中的重要组件之一。

本文将介绍数电集成电路中多种计数器的综合应用实验,并探讨其结论及思考。

二、实验内容1. 实验目的本次实验旨在了解多种计数器的基本工作原理,掌握计数器的设计方法及应用技巧,提高对数字电路设计的理解和应用能力。

2. 实验器材本次实验所需器材如下:- 74LS160 BCD decade counter- 74LS161 synchronous 4-bit binary counter- 74LS163 synchronous 4-bit binary counter- 74LS191 synchronous up/down counter- 数字示波器- 函数发生器- 杜邦线等3. 实验步骤及结果(1)BCD decade counter计数器实验将BCD decade counter连接至数字示波器和函数发生器,并设置函数发生器输出一个方波信号。

观察数字示波器上产生的波形,并记录数据。

结果:当函数发生器输出一个频率为1kHz,占空比为50%的方波信号时,数字示波器上显示出一个周期为10ms,频率为100Hz的正弦波信号。

(2)Synchronous 4-bit binary counter计数器实验将Synchronous 4-bit binary counter连接至数字示波器和函数发生器,并设置函数发生器输出一个方波信号。

观察数字示波器上产生的波形,并记录数据。

结果:当函数发生器输出一个频率为1kHz,占空比为50%的方波信号时,数字示波器上显示出一个周期为16ms,频率为62.5Hz的正弦波信号。

(3)Synchronous 4-bit binary counter计数器实验将Synchronous 4-bit binary counter连接至数字示波器和函数发生器,并设置函数发生器输出一个方波信号。

数字电路 实验 计数器及其应用 实验报告

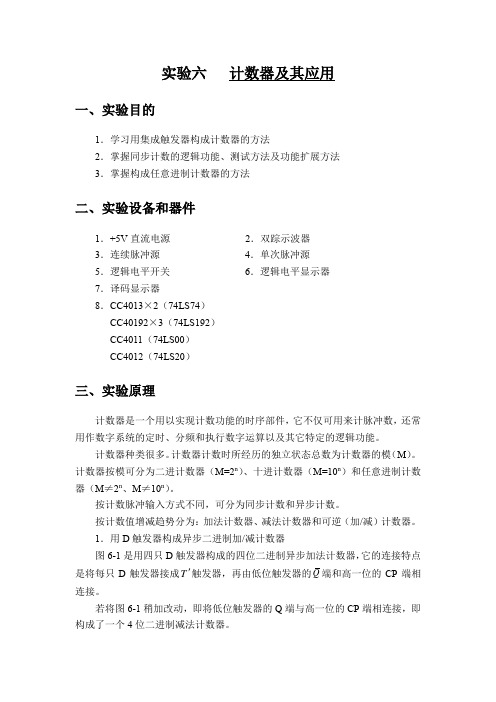

实验六计数器及其应用一、实验目的1.学习用集成触发器构成计数器的方法2.掌握同步计数的逻辑功能、测试方法及功能扩展方法3.掌握构成任意进制计数器的方法二、实验设备和器件1.+5V直流电源2.双踪示波器3.连续脉冲源4.单次脉冲源5.逻辑电平开关6.逻辑电平显示器7.译码显示器8.CC4013×2(74LS74)CC40192×3(74LS192)CC4011(74LS00)CC4012(74LS20)三、实验原理计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

计数器计数时所经历的独立状态总数为计数器的模(M)。

计数器按模可分为二进计数器(M=2n)、十进计数器(M=10n)和任意进制计数器(M≠2n、M≠10n)。

按计数脉冲输入方式不同,可分为同步计数和异步计数。

按计数值增减趋势分为:加法计数器、减法计数器和可逆(加/减)计数器。

1.用D触发器构成异步二进制加/减计数器图6-1是用四只D触发器构成的四位二进制异步加法计数器,它的连接特点是将每只D触发器接成T 触发器,再由低位触发器的Q端和高一位的CP端相连接。

若将图6-1稍加改动,即将低位触发器的Q端与高一位的CP端相连接,即构成了一个4位二进制减法计数器。

2.中规模十进制计数器、十六进制计数器(1)CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能。

当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3置入计数器。

当CR为低电平,LD为高电平时,执行计数功能。

执行加计数时,减计数端CP D接高电平,计数脉冲由CP U输入;在计数脉冲上升沿进行8421码十进制加法计数。

执行减计数时,加计数端CP U接高电平,计数脉冲由减计数端CP D 输入,表6-2为8421码十进制加、减计数器的状态转换表。

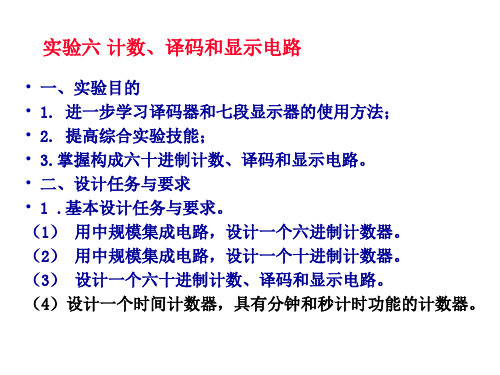

实验_六计数、译码和显示电路(Y)

十进制计数器 CT74LS160(162)与二进制计数器 74LS161(163) 比较

Q0

Q1

Q2

Q3

Q0

Q1

Q2

Q3

CP

CTT CTT CTP CT74LS161 CO CTP CT74LS160 CO CT74LS163 CT74LS162 (162)与 CR LD D0 D1 D2 D3 D3 CP CR LD D0 D1 D2CT74LS160 CT74LS161(163)有何不同? CR LD

0 1 2 3 4 5 6 7 8 9 10

也可取 D3 D2 D1 D0 = 0011 LD = CO CO = Q3 Q0

方案 2:用 “160” 的后七个状态 0011 ~ 1001实现七进制计数。

取 D3 D2 D1 D0 = 0011 ,LD = CO

1 CP

CTT Q0 Q1 Q2 Q3 CTP CT74LS160 CO

00 0 0

01 0

Z

11 0 0

10 1

Q3 Q2 Q1

n +1 n +1 n +1

= Q 2n

= Q 1n = Q 3n

即:

Q3n+1(010)=1, Q3n+1(101)=0

Q2n+1(010)=0 , Q2n+1(101)=1 Q1n+1(010)=1 , Q1n+1(101)=0

010 101

Z = Q 3n Q 2n 自启动失败, 改变 Q1:

Q1

n +1

n n = Q3n + Q2 Q1

010

101

这样:Q1n+1(010)=1, Q1n+1(101)=1 明显的, 能够自启动

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4 / 9'.

.

发电路实现。CP 脉冲采用实验箱中的连续可调脉冲源,不用单独设计,S∕P 和 Clean 均为轻触按键。

5V

R1

R2

10kΩ 10kΩ

译码

译码

S∕ P

Clean

CP

74LS190

74LS190

脉

(2)

(1)

冲

开始∕ 暂停 控制 电路

▁▁ 0 PL U/D

CP

冲

Q0~Q3

Q0~Q3

模式切换、置数控制电路

图 6-5 倒计时计数器

如图 6-5 所示,按键 S 为倒计时数设置键,M 为模式切换键,S 和 M 键通过模 式切换、置数控制电路实现倒计时数的设定和倒计时功能的切换,C 为清零键,在 任意时刻都能实现对计数结果进行清零。

5 / 9'.

教案编写日期 年月日

教学内容与教学过程

提示与补充

一、 实验前准备实验所用仪器、实验报告、板书实验内容 二、 组织实验课堂

1. 根据实验人数合理分组 2. 学生签名(签到表轮流签名) 3.讲解本次实验方法、要求 三、实验指导 主要讲解实验目的、实验原理、实验步骤及其实验的注意事项等;

1 / 9'.

.

1 (a)复位脉冲反馈法

1 (b)置位脉冲反馈法

图 6-3 复位脉冲反馈法

当 CP 端连续输入 6 脉冲后,D4D3D2D1=0110,其中 D2D3 接到一个与非门的两 输入端,与非门的输出端与清零端 MR'相连,此时与非门输出为 0,计数器产生 清零动作,所有输出端全为零,计数又从零开始。当 CP 端输入的脉冲数少于 6 个 时,与非门的量输入端至少有一个为零,与非门输出均为 1,计数器不产生清零动 作。

图 6-4 数字秒表原理框图 2. 用 74LS190 设计一个倒计时计数器,要求倒计时数值能在 0-99 之间任意设定。

5V

R1

R2

10kΩ 10kΩ

R3 10kΩ

译码

译码

S

M

C

74LS190

(2)

CP

▁R7C4LS19(10)

P0

P0

P1 P2 P3

P1 P2 P3

Hale Waihona Puke CP 脉▁ 0 PL

▁ U/D

.

课题

计数器及其应用

需 2 课时

教学 目的 要求

1.掌握中规模常用集成电路计数器的逻辑功能测试及使用方法; 2.掌握任意进制计数器的设计方法和原理; 3.掌握中规模常用计数器芯片的应用。

教学 重点

理解掌握中规模常用集成电路计数器的逻辑功能测试及使用方法;

教学 难点

掌握任意进制计数器的设计方法和原理;

3)按计数脉冲引入方式不同分为: 同步计数器:在同一计数脉冲(CP)的作用下,计数器中的触发器同时改 变状态。

缺点是计数位数越多电路越复杂,优点是工作频率较高; 异步计数器:在同一计数脉冲(CP)的作用下,计数器中的触发器状态改 变不是同

时发生。优点是电路结构简单,缺点作频率较低,容易产生竞争-冒险现象。 (一)基本实验任务

3. 任意进制计数器设计 1)复位脉冲反馈法:通过给清零端加一个触发电平,强制输出端输出全为零。

如图 6-3(a)图所示,为复位脉冲反馈法构成的六进制计数器。

3 / 9'.

.

74LS161D

0 3 P0 0 4 P1 0 5 P2 0 6 P3

Q0 14 Q1 13

Q2 12 Q3 11

D1 D2 D3 D4

1. 74LS161 逻辑功能测试 74LS161 是四位二进制同步计数器,具有计数、预置、保持、清除功能。

2 / 9'.

.

(a)引脚排列

(b)逻辑符号

图 6-1 74LS161 引脚排列及逻辑符号

74LS161 引脚功能说明: MR':清零端,低电平有效; CP:计数脉冲输入端; P0~P3:并行数据输入端; TC:计数进位端; Q0~Q3:数据输出端; PE':预置数使能端,低电平有效; CET、CEP 计数使能端,高电平有效;

.

设计要求:电路上电后,初始状态为倒计时数设置状态,按下 S 键可实现置数, 倒计时数能在 0-99 之间任意设定;电路由置数模式切换至倒计时模式后,计数器 开始自动倒计时,直到 00 时,计数停止。模式状态提示分别用两只不同颜色的 LED 灯来表示(例如绿灯亮红灯灭表示置数模式,绿灯灭红灯亮表示倒计时)。

四、实验原理

1.所谓计数器就是对输入的脉冲进行“数数”的时序逻辑电路。计数器不仅可用来 计数,还可用来实现分频、定时、产生节拍脉冲、序列脉冲等。 2.计数器分类:

1)按进制分为二进制计数器和非二进制计数器两大类。最常用的十进制计数 器属于非二进制计数器。

2)按计数方法可分为:加法计数器(计数值随计数脉冲的输人而递增);减法 计数器(计数值随计数脉冲的输人而递减);可逆计数器(具有加法和减法计数功 能的计数器)

74LS161D

0 3 P0 0 4 P1 0 5 P2 0 6 P3

Q0 14 Q1 13

Q2 12 Q3 11

D1 D2 D3 D4

1

7 CEP

TC 15

D5

1

7 CEP

TC 15

D5

10 CET

10 CET

1 ~MR 9 ~PE 1

~MR 9 ~PE

CP

2 CP

CP

2 CP

接单脉冲插孔

接单脉冲插孔

五、实验预习

1.熟悉 74LS161 和 74LS190 芯片引脚排列及引脚功能。 2.预习任意进制计数器的设计方法及原理。 3.利用 Multisim 仿真软件对基本任务进行仿真测试,并画出基本任务第 3 项 中两种反馈脉冲法对应的实验接线电路,设计出相应的实验测试数据用表格。 4.任选一项扩展任务,并利用 Multisim 仿真软件进行电路设计和仿真调试, 直至电路功能完全正常为止,画出仿真电路图(电路图使用模块化画法,即实现某

2)置位脉冲反馈法:将计数器的数据输入端全置零,通过给预置数端加一个 触发电平,将数据输入端的数置入计数器,这样迫使计数器重新从零计数。置位脉 冲反馈法如图 6-3(b)图所示,与非门的输出端改接到计数器的置位端 PE',当计 数到 0110 时,与非门输出由 1 跳变为 0,计数器在此低电平作用下产生置位动作, 将并行数据输入端的 0000 送至输出端,使得输出全被置为 0,计数又从零开始。

(二)扩展任务 1. 用 74LS161 设计一个数字秒表(0~99S),要求具有启动、暂停和清零功能。

数字秒表电路原理框图如图 6-4 所示。 设计要求:

电路上电时显示“00”,只有当 S∕P(开始∕暂停)键按下后,秒表开始计数, 第二次按下 S∕P 键,计数暂停,再次按下 S∕P 键时,秒表接着第一次计数结果继 续计数;任何时候按下 Clean 键,都能实现清零。