逻辑门电路课件.共48页文档

合集下载

逻辑门电路说课课件知识讲解共44页

逻辑门电路说课课件知识讲 解

26、机遇对于有准备的头脑有特别的 亲和力 。 27、自信是人格的核心。

28、目标的坚定是性格中最必要的力 量泉源 之一, 也是成 功的利 器之一 。没有 它,天 才也会 在矛盾 无定的 迷径中 ,徒劳 无功。- -查士 德斐尔 爵士。 29、困难就是机遇。--温斯顿.丘吉 尔。 30、我奋斗,所以我快乐。--格林斯 潘。 Nhomakorabea谢谢

11、越是没有本领的就越加自命不凡。——邓拓 12、越是无能的人,越喜欢挑剔别人的错儿。——爱尔兰 13、知人者智,自知者明。胜人者有力,自胜者强。——老子 14、意志坚强的人能把世界放在手中像泥块一样任意揉捏。——歌德 15、最具挑战性的挑战莫过于提升自我。——迈克尔·F·斯特利

26、机遇对于有准备的头脑有特别的 亲和力 。 27、自信是人格的核心。

28、目标的坚定是性格中最必要的力 量泉源 之一, 也是成 功的利 器之一 。没有 它,天 才也会 在矛盾 无定的 迷径中 ,徒劳 无功。- -查士 德斐尔 爵士。 29、困难就是机遇。--温斯顿.丘吉 尔。 30、我奋斗,所以我快乐。--格林斯 潘。 Nhomakorabea谢谢

11、越是没有本领的就越加自命不凡。——邓拓 12、越是无能的人,越喜欢挑剔别人的错儿。——爱尔兰 13、知人者智,自知者明。胜人者有力,自胜者强。——老子 14、意志坚强的人能把世界放在手中像泥块一样任意揉捏。——歌德 15、最具挑战性的挑战莫过于提升自我。——迈克尔·F·斯特利

逻辑门电路课件

Rp(min)

VDD VOL(max) I OL(max) I IL(total)

… …

+V DD IOL(max) RP

0

IIL(total)

k

IIL

1

n

m

1

当VO=VOH

为使得高电平不低于规定的VIH的 最小值,则Rp的选择不能过大。 Rp的最大值Rp(max) :

I0Z(total)

+V DD RP

50%

10%

t

f

90%

50% 10%

tr

4. 功耗

静态功耗:指的是当电路没有状态转换时的功耗,即门电路空 载时电源总电流ID与电源电压VDD的乘积。

动态功耗:指的是电路在输出状态转换时的功耗, 对于TTL门电路来说,静态功是主要的。 CMOS电路的静态功耗非常低,CMOS门电路有动态功耗

5. 延时功耗积 是速度功耗综合性的指标.延时功耗积,用符号DP表示。 几种CMOS系列非门的DP见下页。

D2

CN

TN

(3) vI < vDF D2导通, D1截止 vG = vDF

当输入电压不在正常电压范围时,二极管导通,限制了电容两端电 压的增加,保护了输入电路。

RS和MOS管的栅极电容组成积分网络,使输入信号的过冲电压延 迟且衰减后到栅极。

(2)CMOS逻辑门的缓冲电路

输入、输出端加了反相器作为缓冲电路,所以电路的逻 辑功能也发生了变化。增加了缓冲器后的逻辑功能为与非 功能

6.8 25.84

C、I=2V~3V

TN导通,TP导通

vO vI

2. 传输门的应用

(1) 传输门组成的异或门

B=0

A

《逻辑门电路 》课件

能:输入全为1时输出 为0,其他情况输出为1

符号表示:通常用"NAND"表 示

真值表:列出所有输入和输出 组合的真值表

应用:常用于实现逻辑运算, 如与、或、非等

逻辑功能:输入全为1时输出为0,其他情况输出为1 符号表示:输入端A、B,输出端Y 真值表:列出所有输入输出组合及其对应的输出值 应用:用于实现逻辑运算、控制电路等

实现逻辑运算:与、或、非等 基本逻辑运算

控制信号:控制电路的通断、 开关等

数据处理:处理二进制数据, 实现数据传输、存储等

构建复杂电路:通过组合逻辑 门电路,构建更复杂的电路系 统

PART THREE

功能:实现逻辑与 运算

输入:两个输入信 号

输出:一个输出信 号

真值表:当两个输 入信号均为1时, 输出为1;否则输 出为0。

低功耗技术的挑 战与机遇

低功耗技术的未 来展望

人工智能:逻辑门电路是实现人工智能的关键技术之一,未来将在智能机器人、智能语音识别等领域发挥重要作 用。

物联网:逻辑门电路是实现物联网的关键技术之一,未来将在智能家居、智能交通等领域发挥重要作用。

量子计算:逻辑门电路是实现量子计算的关键技术之一,未来将在量子通信、量子加密等领域发挥重要作用。

生物科技:逻辑门电路是实现生物科技的关键技术之一,未来将在基因编辑、生物制药等领域发挥重要作用。

汇报人:

小型化趋势:随着半导 体技术的发展,逻辑门 电路的尺寸越来越小, 提高了集成度和性能

技术挑战:如何实现 更高集成度和更小尺 寸的逻辑门电路,同 时保证性能和可靠性

应用前景:随着物联 网、人工智能等新兴 技术的发展,逻辑门 电路的集成化和小型 化将更加重要。

低功耗技术在逻 辑门电路中的应 用

符号表示:通常用"NAND"表 示

真值表:列出所有输入和输出 组合的真值表

应用:常用于实现逻辑运算, 如与、或、非等

逻辑功能:输入全为1时输出为0,其他情况输出为1 符号表示:输入端A、B,输出端Y 真值表:列出所有输入输出组合及其对应的输出值 应用:用于实现逻辑运算、控制电路等

实现逻辑运算:与、或、非等 基本逻辑运算

控制信号:控制电路的通断、 开关等

数据处理:处理二进制数据, 实现数据传输、存储等

构建复杂电路:通过组合逻辑 门电路,构建更复杂的电路系 统

PART THREE

功能:实现逻辑与 运算

输入:两个输入信 号

输出:一个输出信 号

真值表:当两个输 入信号均为1时, 输出为1;否则输 出为0。

低功耗技术的挑 战与机遇

低功耗技术的未 来展望

人工智能:逻辑门电路是实现人工智能的关键技术之一,未来将在智能机器人、智能语音识别等领域发挥重要作 用。

物联网:逻辑门电路是实现物联网的关键技术之一,未来将在智能家居、智能交通等领域发挥重要作用。

量子计算:逻辑门电路是实现量子计算的关键技术之一,未来将在量子通信、量子加密等领域发挥重要作用。

生物科技:逻辑门电路是实现生物科技的关键技术之一,未来将在基因编辑、生物制药等领域发挥重要作用。

汇报人:

小型化趋势:随着半导 体技术的发展,逻辑门 电路的尺寸越来越小, 提高了集成度和性能

技术挑战:如何实现 更高集成度和更小尺 寸的逻辑门电路,同 时保证性能和可靠性

应用前景:随着物联 网、人工智能等新兴 技术的发展,逻辑门 电路的集成化和小型 化将更加重要。

低功耗技术在逻 辑门电路中的应 用

逻辑门电路授课课件

2. MOS管的开关特性

3.1.4 CMOS反相器

1.电路结构

CMOS逻辑门电路是由N沟道MOSFET和P沟

υI

道MOSFET互补而成。

2.工作原理

(设VDD>(VTN + |VTP|),且VTN = |VTP|) (1)当υi=0V时,TN截止,TP导通。输出υO≈VDD。 (2)当υi=VDD时,TN导通,TP截止,输出υO≈0V。

传输延迟时间 tpd/ns(CL=15pF)

75 10 13 2.9

功耗 (mW) 1(1MHz) 1.5 (1MHz) 1 (1MHz) 0.0003~7.5

延时功耗积 (pJ) 75 15 13

0.00087~22

3.1.9 NMOS门电路(略)

3.2 TTL逻辑门

3.2.1 BJT的开关特性

⑴ 扇入数:一个门电路输入端接入同类门电路的最大数目,取决于门电 路的输入端的个数。

⑵ 扇出数:一个门电路输出端能带同类门电路的最大数目,它表示带负 载的能力。

驱动门的所带负载分为灌电流负载和拉电流负载两种情况:

① 带灌电流负载

② 带拉电流负载

如NOH= NOL则取两者的最小值为门的扇出系数。

各类数字集成电路主要性能参数的比较

3.1.5 CMOS逻辑门电路

1.CMOS与非门

两个并联的P沟道和两个串联的N沟道增强型MOS管组成。

VDD

TP1

TP2

(1)当A、B中只要一个为低时,就会使与 之相连的NMOS管截止,PMOS管导

通,输出为高;

L

(2)当A、B全为高时,两串联的NMOS

B TN2

管导通,两并联的PMOS管截止,输 出为低。

VDD

3.1.4 CMOS反相器

1.电路结构

CMOS逻辑门电路是由N沟道MOSFET和P沟

υI

道MOSFET互补而成。

2.工作原理

(设VDD>(VTN + |VTP|),且VTN = |VTP|) (1)当υi=0V时,TN截止,TP导通。输出υO≈VDD。 (2)当υi=VDD时,TN导通,TP截止,输出υO≈0V。

传输延迟时间 tpd/ns(CL=15pF)

75 10 13 2.9

功耗 (mW) 1(1MHz) 1.5 (1MHz) 1 (1MHz) 0.0003~7.5

延时功耗积 (pJ) 75 15 13

0.00087~22

3.1.9 NMOS门电路(略)

3.2 TTL逻辑门

3.2.1 BJT的开关特性

⑴ 扇入数:一个门电路输入端接入同类门电路的最大数目,取决于门电 路的输入端的个数。

⑵ 扇出数:一个门电路输出端能带同类门电路的最大数目,它表示带负 载的能力。

驱动门的所带负载分为灌电流负载和拉电流负载两种情况:

① 带灌电流负载

② 带拉电流负载

如NOH= NOL则取两者的最小值为门的扇出系数。

各类数字集成电路主要性能参数的比较

3.1.5 CMOS逻辑门电路

1.CMOS与非门

两个并联的P沟道和两个串联的N沟道增强型MOS管组成。

VDD

TP1

TP2

(1)当A、B中只要一个为低时,就会使与 之相连的NMOS管截止,PMOS管导

通,输出为高;

L

(2)当A、B全为高时,两串联的NMOS

B TN2

管导通,两并联的PMOS管截止,输 出为低。

VDD

数字逻辑电路大全PPT课件(2024版)

第6页/共48页

Rb1 4kΩ

Rc 2 1.6kΩ

Vc 2

1

+VCC( +5V) Rc4 130Ω

3

T2 4

1

3

A

31

2T2

D Vo

B

T1

C

Ve 2

1

3

2T 3

Re2

1kΩ

输入级

中间级

输出级

第7页/共48页

2.TTL与非门的逻辑关系

(1)输入全为高电平3.6V时。

T2、T3导通,VB1=0.7×3=2.1(V ),

列。 6 . 74AS 系 列 —— 为 先 进 肖 特 基 系

列, 它是74S系列的后继产品。 7.74ALS系列——为先进低 功耗肖特基系列, 是74LS系列的后继产品。

第30页/共48页

2.3

一、 NMOS门电路 1.NMOS非门

MOS逻辑门电路

VDD (+12V)

VDD (+12V)

VDD (+12V)

0.4V

高 电 平 噪 声 容 限 第1V5页NH/共=48V页OH ( min ) - VON = 2.4V-2.0V =

四、TTL与非门的带负载能力

1.输入低电平电流IIL与输入高电平电流IIH (1)输入低电平电流IIL——是指当门电路的输入端

接低电平时,从门电路输入端流出的电流。

& Vo G0

呈 现 高 阻 , 称 为 高 阻 态 , 或 禁 止 态+V。CC

Rc2

Rc4

Rb1

Vc2 1

3

T2 4

A

&

B

L

EN

《逻辑门电路》课件

与非门(NAND Gate)

与门的输出信号取反。

逻辑门的符号和真值表

符号

每种逻辑门都有其独特的图形符号,用以表示其 功能。

真值表

每个逻辑门都有其对应的真值表,用于描述其输 入输出逻辑关系。

逻辑门的输入输出值

逻辑门 非门 与门 或门 与非门

输入值 0/1 00/01/10/11 00/01/10/11 00/01/10/11

解码器(Decoder)

将较少数量的输入信号解码成较多数量的输出信 号。

时序逻辑电路1来自触发器(Flip-Flops)

用于存储和控制逻辑门电路的状态和信号。

2

寄存器(Registers)

用于存储和传输多个二进制位的信息。

3

计数器(Counters)

用于计数和控制逻辑电路的运行。

状态图和状态表

状态图

逻辑门电路

逻辑门电路是数字电子学中的重要概念。它由不同类型的逻辑门组成,用于 处理和操作数字信号。本课件将介绍逻辑门的基本知识和应用。

逻辑门的类型

非门(NOT Gate)

将输入信号取反,输出为其相反值。

或门(OR Gate)

当任意一个输入信号为高电平时,输出为高 电平。

与门(AND Gate)

当所有输入信号均为高电平时,输出为高电 平。

D锁存器

有一个输入信号D,可以存储 一个比特。

振荡器(Oscillators)

1 简谐振荡器

2 应用示例

通过正反馈回路产生稳定的周期性输出信 号。

振荡器可用于时钟发生器、通信设备和音 频设备。

逻辑门设计和实现

逻辑门设计

设计逻辑门需要考虑电路的功能、布局和性能 要求。

逻辑门实现

与门的输出信号取反。

逻辑门的符号和真值表

符号

每种逻辑门都有其独特的图形符号,用以表示其 功能。

真值表

每个逻辑门都有其对应的真值表,用于描述其输 入输出逻辑关系。

逻辑门的输入输出值

逻辑门 非门 与门 或门 与非门

输入值 0/1 00/01/10/11 00/01/10/11 00/01/10/11

解码器(Decoder)

将较少数量的输入信号解码成较多数量的输出信 号。

时序逻辑电路1来自触发器(Flip-Flops)

用于存储和控制逻辑门电路的状态和信号。

2

寄存器(Registers)

用于存储和传输多个二进制位的信息。

3

计数器(Counters)

用于计数和控制逻辑电路的运行。

状态图和状态表

状态图

逻辑门电路

逻辑门电路是数字电子学中的重要概念。它由不同类型的逻辑门组成,用于 处理和操作数字信号。本课件将介绍逻辑门的基本知识和应用。

逻辑门的类型

非门(NOT Gate)

将输入信号取反,输出为其相反值。

或门(OR Gate)

当任意一个输入信号为高电平时,输出为高 电平。

与门(AND Gate)

当所有输入信号均为高电平时,输出为高电 平。

D锁存器

有一个输入信号D,可以存储 一个比特。

振荡器(Oscillators)

1 简谐振荡器

2 应用示例

通过正反馈回路产生稳定的周期性输出信 号。

振荡器可用于时钟发生器、通信设备和音 频设备。

逻辑门设计和实现

逻辑门设计

设计逻辑门需要考虑电路的功能、布局和性能 要求。

逻辑门实现

逻辑门电路ppt课件

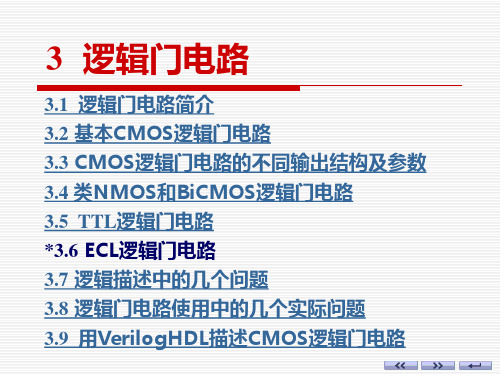

第3章 逻辑门电路

3.2.1 TTL系列门电路 ◆ TTL(晶体管—晶体管逻辑)门电路只制成单片集成电路。输入级由多发射极晶体管构成, 输出级由推挽电路(功率输出电路)构成。标准TTL与非门如下图所示。

◆ 标准TTL与非门

◆ 电路工作原理

1. 电路组成 2. 逻辑关系 当当3一个个发发射射极极都或接3高个电发平射(极A都、接B、低C电都平 接导通(定U通,+B工A25≈(则、V作0).有倒B2在V、时置饱,C,工接和晶T作地导体1的状)通 管集态,状T电2)多态必结至发,定处使射其截于T极集止正2晶电,、向体使极T偏4管T电饱置3T饱压和而1一和导 导U通B4,≈0而.7VT,4截U止CE,S2≈输0出.2V端L 为高电平。 UB3≈0.9V,T3截止,UL≈0

带灌电流负载特性:与非门输出uO为低电平 时,带灌电流负载。当输入都为高电平时, 与非门的V2、V5饱和导通,输出uO为低电平 UOL,这时,各个外接负载门的输入低电平电 流都流入(即灌入)V5的集电极,形成了输 出低电平电流。当外接负载门的个数增加时, 流入V5集电极的电流随之增大,输出低电平 稍有上升,只要不超过输出低电平允许的上 限值,与非门的正常逻辑功能就不会被破坏。 设与非门输出低电平时,允许V5最大集电极 电流为IOL(max),每个负载门输入低电 平电流为IIL时,则输出端外接灌电流负载 门的个数NOL为。NOL=IOL(max)/IIL

第3章 逻辑门电路

第3章 逻辑门电路

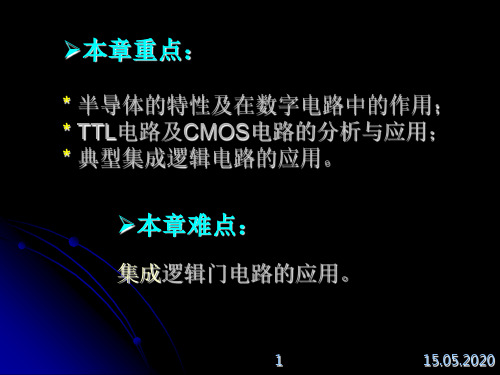

一、学习目的

逻辑门电路是构成数字电路的基本单元。要从内部结构上认识了解逻辑门电路的基本构造和性能 特点,了解逻辑门电路的逻辑关系用分立元件是如何实现的,了解集成门电路的分类和各类集成 逻辑门电路的工作特点及主要参数。

第6部分逻辑门电路47页PPT文档

E 截止状态

17

15.05.2020

6.2 TTL门电路

TTL门电路是晶体管-晶体管逻辑门电路的简称,它是目 前使用最为广泛的一种门电路。

18

15.05.2020

6.2.1 TTL与非门

19

15.05.2020

TTL与非门电路由三部分组成: 1. 输入级

包括多发射极晶体管VT1和基极电阻R1,形成与门 电路,实现逻辑“与”功能。VT1的发射极是“与”输 入 ,VT1的集电极是“与”输出端。

2. 中间倒相级 包括VT2及电阻R2,R3。主要作用是将VT2管的基

极电流放大,以增强对输出级的驱动能力。 3. 输出级 由VT3,VT4,VT5管和电阻R4,R5组成。VT3、

VT4组成射极跟随器电路,同时与VT5组成推挽电路, 提高电路带负载能力。

20

15.05.2020

当电路输入全为高电平时,输出F为低电平;输入 中有一个或一个以上为低电平时,电路输出为高电平。 其逻辑关系为:

3)反向截止特性 当二极管两端的反

向电压大于反向击穿电压 UBR时,反向电流突然剧 增。二极管反向击穿。

12

15.05.2020

6.1.2 半导体三极管

半导体三极管(双极型三极管)简称三极管,它 是利用特殊工艺制成的具有两个PN结的半导体器件。 它有三个电极:基极B、发射极E、集电极C。根据结 构不同,三极管可以分为NPN型和PNP型两类。

砷、锑等)。 杂质原子的五个价电子与周围硅原子组成共价键时,

多出一个价电子,使晶体产生一个自由电子。 根据掺入杂质的多少,可以控制自由电子的数量。

由于自由电子的数量远远大于空穴的数量,这种半导体 导电以自由电子导电为主。将自由电子称为多数载流子, 简称多子;空穴称为少数载流子,简称少子。