直放站和RRU应用TI方案介绍-2011-11

浅谈室内分布系统及RRU.直放站建设技术规范

浅谈室内分布系统及RRU.直放站建设技术规范电信室内分布系统建设⽬录第⼀章系统要求第⼆章系统设计第三章设备安装第⼀节RRU设备第⼆节室内分布系统第四章系统整体测试第⼀节室外直放站系统整体测试第⼆节室内覆盖系统整体测试第⼀章系统要求室内分布系统及RRU/直放站建设必须达到以下要求:1、室内分布系统及RRU必须满⾜系统容量和呼损要求。

2、室内分布系统覆盖设计要求为98%以上区域不得低于-85dBm。

RRU系统覆盖设计要求为95%以上区域不得低于-75dBm。

3、室内分布系统及RRU/直放站建设中所选⽤的元器件必须是在省公司框架协议中确定的产品范围以内室内分布系统建设中覆盖⾯积1000平⽶以上的分布系统建设中必须采⽤1/2"以上馈线。

分布系统建设中各类型天线系统应能适应⽹络发展的需求,⼯作频段需达到2.5G。

4、⼲扰保护⽐:同频⼲扰保护⽐:C/I≥12dBm(不开调频),C/I≥9dBm(开调频)邻频⼲扰保护⽐:200KHZ邻频⼲扰保护⽐:C/I≥-6dBm5、在基站或微蜂窝接受端位置收到的上⾏噪声电平⼩于-120dBm。

6、室内天线的发射功率应⼩于15dBm/每载频即导频功率应⼩于5dBm/每载频。

7、主设备机房位置和⼲线放⼤器安装位置不应影响原有设备的摆放和机房环境,并要求为今后增加设备预留安装空间。

第⼆章系统设计第九条室内分布系统及RRU/直放站⼯程设计概述1、建筑物情况描述:(1)、建筑物基础信息描述包括建筑物的地理位置(含经纬度)、建筑物的⽤途、周边环境情况、建筑物的结构与楼层使⽤分配、建筑物的总⾯积、电梯数量与⽤途、⼈流量等基础信息。

(2)、建筑物当前信号覆盖情况简要描述。

(3)、进⾏覆盖的⽬的。

(4)、本次设计⽅案规模的简介含本次⼯程拟覆盖区域及⾯积,分布系统的类型,信号源的类型,⼯程预算投资总额。

2、⽅案设计依据。

3、⼚家现场勘察报告。

4、设计思路叙述。

(1)根据覆盖⽬标话务和周围⽹络情况选择信号源类型、分布系统类型。

RRU电力解决方案

RRU电力解决方案引言概述:随着无线通信技术的快速发展,基站设备的电力供应成为一个重要的问题。

尤其是无线电单元(RRU)作为基站的核心设备之一,其电力需求更是不可忽视。

本文将介绍RRU电力解决方案,以满足基站设备的电力需求。

一、电力需求分析1.1 RRU的功耗分析RRU作为基站设备的重要组成部分,其功耗是影响整个基站设备电力需求的关键因素之一。

通过对RRU的功耗分析,可以更好地了解其电力需求。

RRU的功耗主要包括射频功耗、数字处理功耗和其他辅助电路功耗等。

对于不同频段和不同制式的RRU,其功耗也会有所不同。

1.2 基站电力供应要求基站电力供应要求是指为RRU提供稳定、可靠的电力供应的条件和要求。

基站电力供应要求包括电压稳定性、电流稳定性、电源容量和备用电源等。

电压稳定性和电流稳定性要求较高,以保证RRU的正常工作。

电源容量要求根据RRU的功耗和基站的规模来确定,以满足RRU的电力需求。

备用电源则是为了应对突发情况,保证基站设备的持续运行。

1.3 现有电力供应方案的问题目前,基站设备的电力供应主要采用市电供电和蓄电池供电的方式。

然而,这种供电方式存在一些问题。

首先,市电供电存在电压波动和停电等风险,容易导致RRU工作异常。

其次,蓄电池供电需要定期维护和更换,增加了运维成本和工作量。

因此,需要寻找更好的RRU电力解决方案来解决这些问题。

二、RRU电力解决方案2.1 太阳能供电方案太阳能供电方案是一种可持续、环保的RRU电力解决方案。

通过安装太阳能电池板和逆变器,将太阳能转化为电能供应给RRU。

太阳能供电方案具有稳定可靠、无需外部电源、环保节能等优点,可以降低基站的运维成本和对传统电力的依赖。

2.2 风能供电方案风能供电方案是另一种可持续、环保的RRU电力解决方案。

通过安装风力发电机,将风能转化为电能供应给RRU。

风能供电方案具有稳定可靠、无需外部电源、环保节能等优点,适用于风能资源丰富的地区。

2.3 蓄电池+UPS供电方案蓄电池+UPS供电方案是一种传统的RRU电力解决方案。

电信数光纤直放站跟模拟直放站工程运用指导资料

需要注意的是导入的数据中的设备编号、系统时间等配置都是导出设备的, 需要进行具体的调整。

6. 联机调试

开通测试

通话测试完毕要再次确认有无干扰基站 。 开通调试完毕后,记下各设置参数,最好能对

各配置项进行截图,以便后期维护和做竣工文 件时使用。

近端机:标准19”2U机箱,88×482×360(mm) 远端机:180×250×500 (mm )

防护等级

符合IP30(近端机);符合IP65(远端机)

重量

近端机:约5kg远端机:约25kg

工作温度

近端机:0℃~+55℃ 远端机:-40℃~+55℃

1. 主要产品性能指标

与同类产品主要指标差异

DFR-3210 数字化宽带 具有AGC(自动增益控制)功能 光输出功率-9dBm~-3dBm 1台近端理论最多支持24台远端 可采用星形菊花链混合组网 支持自动或手动时延调整 时延≤13μs

链连接)的OP2连接。

6. 联机调试

远端机开关量设置

降噪功能选项(远端机) DFR-3210宽带数字光纤直放站不采用降噪功能,在降噪功能选项中

选择设置“不实现降噪功能”,否则影响覆盖效果。

6. 联机调试

近端机衰减设置

在可调范围内调整上、下行增益,使下行输出功率达到设计要求,上下行链 路平衡,保证上行输出噪声电平不干扰基站。

设置完成之后,当进行过一次切换的设备之间再进行切换时,就不需再重新读 取数据,可以直接切换到要切换的设备配置界面。

6. 联机调试

其他操作参数设置

如果要进行多台设备,并且各台设备的配置基本一致时,当配置好一台设 备后,可以通过数据导出、导入数据模版对其他设备直接进行数据配置。

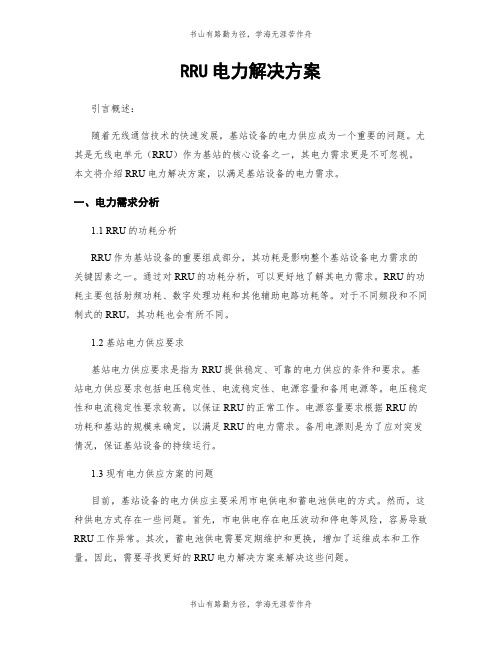

直放站系统介绍

塔放的应用

• 基站塔顶放大器分三种类型:1、上行塔顶放大器 2、

双向塔顶放大器 3、基站功率放大器

基站天线 塔放

NF 馈线

10.5Km

TPA13.5Km

微蜂窝

上行塔顶放大器

• 当基站天线与接收机之间距离较远,或者在接收 机输入端前加有分路、合路器,影响无线覆盖区 上行链路时,可以在天线端增加一个塔顶放大器 以提高上行接收机灵敏度,保证上、下行链路平 衡,扩大基站覆盖范围。

解

波

光发送机

复

分

用

复

器

光纤 用

器

1.31µm

1.31µm

同纤传输方式

1.55µm

1.55µm

光发送机

波

波

光接收机

分

分

MS

复

复

用

光纤 用

BS

光接收机

器

器

光发送机

1.31µm

1.31µm

光缆中如仅有一根空闲光纤,可以采用上下行信号 同纤传输方式,分别用单模光纤中的1.31m和1.55 m 窗口来传输上下行信号。

1.55µm

光端机

1.55µm

1.31µm

波分复用方式

1.31µm

典型光纤直放站光路结构图(三)

C镇 A镇

基站所在地 B镇

光路由图

要求:覆盖A镇和B镇

移频直放站的应用

移频直放站(直接耦合方式)

F1 耦合器 F2

BTS

中继端机

F1

MS

远端机

移频直放站的应用

F1

天线

BTS 天线

近端 机

天线

1 F1 覆盖区域

光纤直放站 覆盖端机C

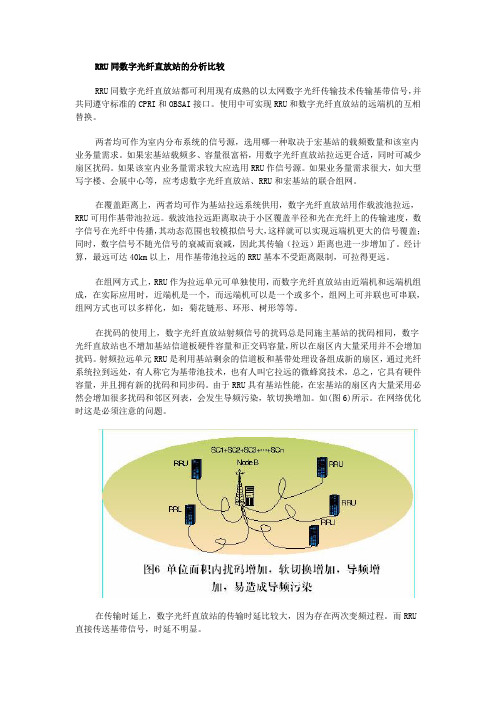

RRU同数字光纤直放站的分析比较

RRU同数字光纤直放站的分析比较RRU同数字光纤直放站都可利用现有成熟的以太网数字光纤传输技术传输基带信号,并共同遵守标准的CPRI和OBSAI接口。

使用中可实现RRU和数字光纤直放站的远端机的互相替换。

两者均可作为室内分布系统的信号源,选用哪一种取决于宏基站的载频数量和该室内业务量需求。

如果宏基站载频多、容量很富裕,用数字光纤直放站拉远更合适,同时可减少扇区扰码。

如果该室内业务量需求较大应选用RRU作信号源。

如果业务量需求很大,如大型写字楼、会展中心等,应考虑数字光纤直放站、RRU和宏基站的联合组网。

在覆盖距离上,两者均可作为基站拉远系统供用,数字光纤直放站用作载波池拉远,RRU可用作基带池拉远。

载波池拉远距离取决于小区覆盖半径和光在光纤上的传输速度,数字信号在光纤中传播,其动态范围也较模拟信号大,这样就可以实现远端机更大的信号覆盖;同时,数字信号不随光信号的衰减而衰减,因此其传输(拉远)距离也进一步增加了。

经计算,最远可达40km以上,用作基带池拉远的RRU基本不受距离限制,可拉得更远。

在组网方式上,RRU作为拉远单元可单独使用,而数字光纤直放站由近端机和远端机组成,在实际应用时,近端机是一个,而远端机可以是一个或多个,组网上可并联也可串联,组网方式也可以多样化,如:菊花链形、环形、树形等等。

在扰码的使用上,数字光纤直放站射频信号的扰码总是同施主基站的扰码相同,数字光纤直放站也不增加基站信道板硬件容量和正交码容量,所以在扇区内大量采用并不会增加扰码。

射频拉远单元RRU是利用基站剩余的信道板和基带处理设备组成新的扇区,通过光纤系统拉到远处,有人称它为基带池技术,也有人叫它拉远的微蜂窝技术,总之,它具有硬件容量,并且拥有新的扰码和同步码。

由于RRU具有基站性能,在宏基站的扇区内大量采用必然会增加很多扰码和邻区列表,会发生导频污染,软切换增加。

如(图6)所示。

在网络优化时这是必须注意的问题。

在传输时延上,数字光纤直放站的传输时延比较大,因为存在两次变频过程。

基站基带拉远rru与光纤直放站应用比较-文档资料

RRU与光纤直放站的差异

前言

很多基站设备提供商推出RRU设备,有的推出微蜂窝设备,很多情 况是在没有确定基站规划目标情况下,将RRU当作NodeB节点来使用。 造成在一个基站服务扇区内有多个NodeB节点,一旦网络全面开通将形 成扰码污染、邻区列表数十个,软切换到处存在,出现虚假话务量,网 络质量很难提高。如果在基站规划一次到位情况下,适当使用无线和光 纤直放站,效果就大大不同,整个扇区只有一个主扰码,导频污染没有 了,邻区列表简单化,直放站产生的泄漏变成有益的多径信号,使得服 务区内网络整体质量得到很大提高,因此基站规划头等重要。

S/P

Cch

S/P

Cch

S/P

Cch

S/P

Cch

S/P

Cch

Gain

Gain Gain Gain Gain Gain

同步码(*)

PSC

S GP

SSCi

GS SCH 同步信道

下行扰码

S I+jQ

I 基带滤波

S 基带滤波 Q

SC1 f1下行链路RF输出

I/Q 调制

SC1 f1RF输出

基带滤波 基带滤波

I/Q 调制

RRU单元

射频调制系统

RRU射频调制与解调系统

它包括: 低噪声放大器、 模拟射频接收机、 ADC、 数字下变频、 数字滤波与天线分集、 多载波功放、 模拟射频发射机、 DAC、 数字上变频器、 预失真与数字滤波等部件。

对这些部件均有一定的监控和管理量。

CPRI 和OBCAI接口概述

CPRI 接口

ADC

DAC

数字 下变频

数字滤波 与天线分集

数字

RRU和直放站的运用方案技术对比分析

RRU和直放站的运用方案技术对比分析作者:杨洋来源:《电子技术与软件工程》2015年第04期RRU技术可以节省常规建网方式中需要的大量机房和基带单元的投资。

本文就RRU方案运用的进行技术对比分析,从实际运用分别探讨其优缺点、当前运用的问题及建议和注意事项等。

【关键词】RRU 优缺点问题及建议注意事项RRU是分布式网络覆盖模式的一种,它是将大容量的BTS集中放置在环境良好的局间机房,将基带信号处理设备集中处理,将BTS采用通过光纤拉远到远端射频信号单元,布置在预先设计的网络上,及确定的节点上,从而节省常规建网方式中需要的大量机房和基带单元的投资。

其工作原理是将BTS下行方向的信号,经过变频和滤波,在由射频滤波器和线性功率放大器放大后,再由滤波器件发送传至天馈线设备上;上行方向是将接收到的MS上行无限信号,经过滤波器件和低噪声放大器,以及信号放大器、滤波器、下变频器件后,再由模数转换器件、数字中频等器件进行相关处理等。

1 RRU和直放站相关技术参数分析在直放站的覆盖范围内,例如不设置直放站,此时BTS覆盖的边延,MS到达BTS的时延是τ1,BTS的preamble win length搜索窗的宽度是preamble pn offset+τ1。

当在边延增加直放站后,MS到达BTS的时延是τ1+τ0,BTS的preamble win length搜索窗宽度应设为:preamble pn offset+τ1+τ0>preamble pn offset+ τ1。

因此增设了直放站后,在直放站所能辐射的区域范围内,MS到达BTS的信号时延会有上升,为了MS能正常的接入移动网系统,提高相应QOS的质量,BTS的preamble win length也必须增大。

Preamble win length增加的大小应与直放站时延和直放站与BTS间的光纤时延同步。

但是在电信的实际扩大了CDMA BTS容量与BTS个数以后,BTS的搜索窗口已经在市区超过其最大值,因此相关参数在设置时难度较大。

数字直放站介绍(调试版)

二、整 机 原 理 介 绍

优势 1.射频和光在传输过程中是独立的,两者互不影响。

2.动态范围大,信号不随光信号的衰减而衰减。

3.信号的分路与合路通过数字方式实现:下行分路通过数字比特流的复 制实现,上行合路通过数字和实现,信号不会产生任何损耗。

4.数字传输受光的色散影响较小,短距离传输时可采用多模光纤。

FPGA IC

多了4个面板同步指示灯

远端数字板

下行150M中频输出

上行76.8M中频输入 BGA易出问 题

输出15.36M信号 给变频模块做本 振参考源

LED10:ARM RUN指示 灯隔1秒闪烁,快闪2下 表示485总线正常 LDE20:主光口同步亮起 LED13:主光口同步亮起 LED14、11:FPGA RUN闪 LED21:光收正常亮起 LED22:检到光模块亮起 LED2:光发正常亮起

DFR-1080R 10W NIV

GRRU-1080R 40W DIV

DFB-3322131 2W

DFB-3322131 2W

一体化数字板:主监控板+ 数字处理部分+变频模块

GRRU-1022A H8 I

GRRU-1022A H8 II

GRRU-1022A

H16

GRRU-1822A

H16

GRRU-1022WA (60W)

DFR-1080L

(10W ) DIV

DFR-1080 L (40W ) DIV

GRRU-1022R 一体化 (P49)

GRRU-1023R

四、生产情况及调试要点

四、生产情况及调试要点

四、生产情况及调试要点

数字板好坏的关键工序 贴片的目标良品率:95%

下行76.8M中频输入

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

日程•直放站和RRU基础•TI系统方案最新器件介绍应用方案介绍•ADC/DAC模拟接口•频谱规划基础之什么是直放站?直放站是一种信号中继器(Repeater),把接收的基站下行射频信号和手机的上行射频信号进行功率放大。

直放站在下行链路中,由施主天线现有的覆盖区域中拾取信号,通过带通滤波器对带通外的信号进行极好的隔离,将滤波的信号经功放放大后再次发射到待覆盖区域。

在上行链接路径中,覆盖区域内的移动台手机的信号以同样的工作方式由上行放大链路处理后发射到相应基站,从而达到基地站与手机的信号传递。

常见的直放站通信制式有GSM, CDMA,WCDMA,以及专网等。

在TDD系统直放站应用比较少,如WiMAX, TDS, TDDLTE等,为什么?基础之什么是RRU?RRU(Remote Radio Unit),将传统基站分割为两个部分,即基带处理单元(BBU)和远端射频单元(RRU),二者之间通过光纤连接;其接口基于开放式接口协议CPRI或者IR协议等。

理论上只要所有RRU设备遵循相同的接口协议,可以和所有的主设备厂家BBU进行连接,实现通用性。

在新架构网络中,一个BBU可以连接多个RRU单元,既节省空间又降低成本,同时提高了组网灵活性。

3G网络大量使用分布式基站架构,RRU(射频拉远模块)和BBU(基带处理单元)之间需要用光纤连接。

一个BBU可以支持多个RRU。

采用BBU+RRU多通道方案,可以很好地解决大型场馆的室内覆盖。

目前TDS,CDMA2K,WCDMA,LTE,WiMAX等主流制式都广泛采用BBU+RRU架构,在传统的GSM系统中,也有部分厂家在推广BBU+RRU架构来代替传统基站+直放站模式。

基础之数字直放站Vs RRU直接基带传输,时延小两次变频,时延大时延独立扰码和同步码与施主基站同扰码干扰高低建设成本单设备比直放站差不多1拖多成本优势大设备成本容量可调整容量受限于源容量可灵活组网可灵活组网组网RRU 数字直放站增加导频污染导致软切换增加结论结论::在目前GSM 网络架构下,直放站的成本优势不太可能被RRU 完全代替。

但是在LTE 等模式下如果采用PICO/FemtoCell 模式,直放站市场会下滑比较快。

由于目前3G 网络对日益增长终端数据业务的承载能力仍略显不足,各大运营商都在大力投入WLAN 的建设,而数字直放站设备和WLAN 的融合混模覆盖可以增加运营商对其青睐。

基础之系统拓扑RRU直放站RRURRU基础之数字直放站覆盖注:这里仅讨论数字直放站方案优点:架设方便,成本低;缺点:存在同频干扰问题,需要收发天线之间大隔离度,防止PA 自激.需要开发数字ICS 算法降低同频干扰,会提高设备成本;空中传输信噪比恶化快,无法承载高据流量;TX RFRX RFDUC/DDCDDC/DUCduplexerNear repeaterRX RFTX RFduplexerBS freq relay freqTX RFRX RFDUC/DDCDDC/DUCduplexerremote repeaterRX RFTX RFduplexerBS freq relay freq BSUEUE优点:架设方便,成本低;收发不同频,无同频干扰;缺点:需要额外的频谱资源;增加移频中继设备,成本上升;空中传输信噪比恶化快,无法承载高据流量;TX RFRX RF DUC DDCOptical interfaceduplexerTX RFRX RFDUC DDC Optical interfaceduplexerNear repeaterRemote repeaterOptical fiber优点:没有同频干扰;传输数字化,信号无误差传输;降低了底噪。

高性能,承载高数据流量业务;缺点:铺设光纤成本高硬件成本稍微高;信号源通过射频电缆从基站天线耦合基础之中射频框图(数字直放站和RRU中射频功能几乎相同)基础之中射频框图TI HPAADS58C28/58C23 DAC3482/3484/34H84 TRF3705-02ADS58C28TI&SVA combo SolutionTI SVALMH6521 LMK048xx LMX2531/2541DAC3482/3484TI HPA&SVA High Speed Signal Chain Combo SolutionLMH6521 RX0 RX1TRF3705-02 I/Q Modulator TX0ADC ADCDAC DACPRI_REFSEC_REFTCXO10MHzLMX2531/41Digital ProcessorLMX048xxDual Loop PLLDual Loop PLLSVATRF3705-02VCXO30.72MHzDAC DACI/Q ModulatorTX1SVA基础之中射频框图TI HPA&SVA RF PA Combo Solution TI HPADAC6578/TLV5631/AMC7812/AMC7891 TMP75/TMP20 INA193TI&SVA combo SolutionTI SVALMH2110MCUDAC(DAC6578)Current Sensor(INA193)Power Detector(LMH2110)RF AttenuatorTemp Sensor(TMP75)AMC7812/7891TI系统方案之器件篇 系统方案之器件篇ADS58C28/ADS58C48接收机ADC 接收机Dual/Quad 11-bit 200MSPS ADC with SNRBoost3G Low Power Consumption• 335 mW/ch with 60+MHz SNRBoost 185MSPS • 35% power reduction from ADC62C17 • Wideband SNRBoost3G: 60MHz Signal BW • 72.2 dBFS SNR at 140MHz and 185MSPS • 88 dBc SFDR at 140MHz and 185MSPS • 6 dB gain in 1 dB steps • Selectable DDR LVDS or CMOS outputs • 9x9mm, 64-pin QFN package • 1.8V AVdd and DVdd supplies • No export license required• Lower system operating cost • Enables TD-SCDMA, LTE, WiMAX and MC-GSM • Optimization of SNR and SFDR • Compatible to the GC53xx family as well as all FPGAs and most ASICs • High density with ease of use from a QFN • See AppNote SLAA461 on Power Supply Design • Unlimited orders to China14bit BW=0.33*FsTI系统方案之器件篇 系统方案之器件篇ADS58C20/3: High SFDR Dual Channel Receiver IC• • • • • • • 14 bit Internal ADC, 9 or 14 bit output Maximum Input Sample Rate: 500MSPS Maximum Output Sample Rate: 250MSPS Optional 2x Decimating Filter Optional 75 MHz BW SNR Boost Power = 700mW/channel Input Buffer with high impedance eases filter design • 80-pin TQFP package with PowerPAD • Pin Compatible Family Members– ADS58C20 – 9 or 14-bit output, high SFDR –HD2-5 = 86 dBc MIN, 90 dBc TYP –Non-HD2-5 = 92 dBc MIN –SFDR in 40 MHz (Fs*3/8) = 90 dBc MIN – ADS58C23 – 9 of 14-bit output, reduced SFDR –SFDR = 80 dBc MIN 85 dBc TYP接收机ADC 接收机TI系统方案之器件篇 系统方案之器件篇ADS58B18/58B19• Low power consumption: 360mW with LVDS I/O • High Impedance input buffer • Flattens gain response across 3dB bandwidth • Removes sample-and-hold kickback • High performance with selectable SNRBoost • 66.2 dB SNR, 87 dBc SFDR at 70MHz IF • 72.2 dB SNR, 83 dBC SFDR at 150 MHZ with 30MHz wide SNRBoost • 6 dB gain in 1 dB steps for SNR/SFDR trade-off • 7x7mm, 48-pin QFN package • Selectable DDR LVDS or CMOS outputs with halfand full-swing LVDS modes • 1.8V AVdd and DVdd supplies • Export control compliant – no license requiredDPD反馈 反馈ADC 反馈Low Power, Buffered Input 11-bit 200MSPS/9bit 250Msps ADC with SNRBoost• Reduces load on power supply and minimizes thermal requirements – see 1Q 2010 Analog Applications Journal for best power designs • Eases gain matching for passive and active AFE designs in wide bandwidth DPD feedback signals • Provides high SNR and dynamic range required for high performance digital pre-distortion • Allows for optimization of SNR and SFDR for input signal swings between .5 and 1.5 Vpp • Small form-factor for minimized board space • Compatible to the GC53xx family as well as all FPGAs and most ASICsDAC5682z TX TRF372017 I/Q Modulator LO DPD FeedbackGC5322/28DUC-CFR-DPD DUC-CFR-DAC DACADS58B18ADCPGA870 Mixer Attenuator FB LO (EXT)TI系统方案之器件篇 系统方案之器件篇ADS62PF49TI系统方案之器件篇 系统方案之器件篇Dual 16-bit, 2x-4x Interpolation, 800MSPS DAC • • Dual 16-Bit 800 MSPS DAC 8-Bit Input LVDS Data Bus • 8 Sample Input FIFO • Optional Data Pattern Checker • Compatible with GC5330 Multi-DAC Synchronization Excellent Performance • 80dBc ACLR WCDMA TM1 at 153.6 MHz Low Power Dissipation • 1.1W at full-speed Digital Processing & Options: • Optional 2x/4x Interpolation FIR • Fs/2 and Fs/4 Coarse Mixer • Digital Quadrature Modulator Correction: Gain, Phase and Offset • • • • • • •DAC3283• •Temperature Sensor 3- or 4-wire Serial Control Interface On Chip 1.2V Reference 3.3V Analog, 1.8V Digital Supplies Small Package: 7x7mm 48-pin QFN Scaleable Output Current: 2 to 20mA Now in Production!• •TI系统方案之器件篇 系统方案之器件篇Quad and Dual Channel 16bit, 1.25GSPS DACs • DAC3484: Quad, Byte-wide DDR, 88-mRQFN • DAC3482: Dual, Word-wide DDR, 88-mRQFN • Low Power • Total Power ~ 1W • 65% lower power than competition • Space Saving Packages Options: • 9x9mm 88 pin mrQFN Package • Multi-DAC Synchronization • Input Sample FIFO • On-board 2x-32x PLL • Interleaved LVDS Data Bus • 4 ch: 250 MHz Bandwidth (312.5Msps) • 2 ch: 500 MHz Bandwidth (625Msps) • GC5330 Compatible • Digital Processing & Options: • Selectable 2x-16x Interpolation • Coarse Mixer • Complex Mixer with 32-bit NCO • Digital Quadrature Modulator Corr. • Sinx/x Correction FilterDAC3484/DAC3482• 3-wire or 4-wire serial control bus (SPI) • Integrated Temperature Sensor DAC3484 (Quad, 88-mRQFN): • Samples/EVMs Now • RTM June 2011 • Reduces board space by half when compared to today’s 2 dual DAC solutions. • Reduce interface pin count required by half compared to DAC5682Z. This saves cost on expensive FPGA IO. • Digital Signal Processing options allows for flexible IF placement • Optimized for wide bandwidth multiantenna applications.1.25GSPS, 8x, 140MHz IF, ACLR = 78dBcTI系统方案之器件篇 系统方案之器件篇• Same Features as DAC3484 • Very Low Power design: ~1W at 1.25GSPS • 32-LVDS data lines, DDR interface– Input Sample FIFO – Optional Data Pattern Checker – Optional Dual Parity Function: one for each complex channelDAC34H84Quad Channel 16bit, 1.25GSPS DAC, Word-wide DDR Interface 12x12mm, 196 BGA Package Modified Interface and Package • 32-Pairs LVDS Data Bus • Two 16-bit DDR Interfaces • 500 MHz Bandwidth Support • BGA Package • 12x12mm, 0.80mm pitch• Interface allows double the data rate than the DAC3484 • Multi-DAC Synchronization • On-board very low jitter PLL • Digital Processing & Options:– – – – – Selectable 2x-16x Interpolation Independent Complex Mixers with 32-bit NCO Power Saving Coarse Mixers: ±n*Fs/8 Digital Quadrature Modulator Correction (QMC) Sinx/x Correction Filters• 3-wire or 4-wire serial control bus (SPI) • Integrated Temperature Sensor20TI系统方案之器件篇TRF3705-0221TI 系统方案之器件篇•Multi-standard Base Stations•3GPP (LTE, W-CDMA, TDS-CDMA)•MC-GSM•WiMAX and WiBRO (OFDMA)•3GPP2 (CDMA2000)•Software Defined Radios –defense and commercial•Wireless infrastructure repeaters•Up to 4x8 MIMO transceivers•Up to 48 Channels of DUCs and DDCs in 4x 12 channelblocks, configurable into a single wideband DUC or DDC•1 DUC and DDC channel up to 100MS/s each •24 DUC and DDC channels up to 6.4MS/s each •1-98,304x decimation and interpolation range•40 Tx LVDS pairs, 38 Rx LVDS pairs with 1.24GSPS data rate support for Tx, 930 MSPS Rx•Supports multi-channel, multi-carrier, multi-mode andmulti-band operation across wide bandwidths•Complete analog and solution with reference design available to speed time to market•Upcoming EVM compatible with over 60 TI high speed ADC and DAC EVMs.•Fractional resampler for each 12 channel DUC/DDC block•I/Q imbalance correction for transmit and receive•Highly configurable DUC and DDC channels enable wide bandwidth support as well as multi-band, multi-mode transmit and receive solutions without FPGA development•Supports converters for up to 4 Tx and 8 Rx chains without the need for costly FPGAs•Allows for rapid development of highly flexible, software configurable wireless platforms•Enables rapid evaluation and prototyping of complete transmit and receive solution•Provides multi-rate support for each DUC/DDC block•Reduces DC offset and compensates for I/Q imbalances and LO leakage to improve receiver error vector magnitudeGC6016TI 系统方案之器件篇•Multi-standard Base Stations•3GPP (LTE, W-CDMA, TDS-CDMA)•MC-GSM•WiMAX and WiBRO(OFDMA)•3GPP2 (CDMA2000)•Multi-carrier power amps (MCPAs)•Wireless infrastructure repeaters •Up to 4x8 MIMO transceivers•Highly Integrated digital transmit and receive processor:•Digital Pre-Distortion –5th order adaptive correction •Crest Factor Reduction•1-48 Configurable bandwidth DUCs and DDCs•Supports multiple transmit antennas for main/diversity and MIMO applications•Four transmit antennas with 30MHz of bandwidth•Two transmit antennas with 60MHz of bandwidth •Supports multi-channel, multi-carrier, multi-mode andmulti-band operation across wide bandwidths•Complete analog and DSP solution with reference design •Direct connection to C6748 with TI high performance DPDalgorithm. Can also be used with customer DPD IP •DPD algorithm compensates for PA memory effects•40Tx LVDS pairs, 30 Rx LVDS pairs and 8 DPD feedback LVDS pairs with 1.2GSPS support (Rx), 921MSPS (Tx)•Integration reduces design complexity, development time, power consumption and cost compared to large FPGA (Virtex, Stratex) and ASIC DSP solutions•Simplifies board layout for 2x2, 2x4, 4x4 and 4x8 solutions while reducing cost by an order of magnitude vs. FPGAs •Allows for development of highly flexible, software configurable wireless platforms•Saves up to 6 man-months of evaluation and prototyping by enabling customer PA linearization within one hour•Provides flexible software environment for upgrading DPD algorithm to adapt to new and emerging standards•Improves ACLR by as much as 30 dB, enabling PA to be driven harder and to higher efficiencies•Supports converters for up to 4 Tx and 8 Rx chains plus DPD feedback without the need for costly FPGAsGC5330/5337TI系统方案之器件篇SVA LMH6521TI系统方案之器件篇LMH6517 to LMH6521Utra-Low noise Clock Jitter cleanerBlock DiagramUtra-Low jitter Clock GeneratorDual Buffer with 14 programmable outputsTI系统方案之器件篇LMK04800 +LMK01801 Clocking for RRU systemTI系统方案之器件篇 系统方案之器件篇3:10 Differential Fanout BufferSVA LMK00301TI系统方案之器件篇 系统方案之器件篇Wideband Frequency SynthesizerSVA LMX2581LMX2531,2541 to 2581TI系统方案之器件篇 系统方案之器件篇CPRI Serdes with Precision DCMSVA SCAN25100• Exceeds LV and HV CPRI voltage & jitter requirements • 614.4, 1228.8 and 2457.6Mbps operaion • 800ps Delay Calibration Measurement accuracy • Receiver and remote end synchronization without reference clock • Low noise recovered clock • Optional 8b/10b encoding • Transmit de-emphasis extends cable driveTI系统方案之器件篇 系统方案之器件篇CIF TLK10002TI系统方案之器件篇 系统方案之器件篇SVA LMH21108 GHz Logarithmic RMS Power Detector with 45 dB dynamic rangeTI系统方案之数字直放站方案 系统方案之数字直放站方案RX LO ADS58C28 ADS58C23 ADS58C20 DAC3484 DAC3482 DAC34H84 TX C TRF3703/4-17/TRF3705-02RX AAttenuatorsADC ADCAttenuators LMH65xxGC6016DUC-DDC DUC-DAC DAC DAC DACI/Q ModulatorAttenuators TRF372017I/Q ModulatorFPGAInterface ProtocolBuff.LOEMIF SPIEP M3/ARM Serdes TLK313xSVA CLOCKPowerUCD/TPSSupport 30MHz,12 carriers/ANTTI系统方案之 系统方案之1Tx2Tx带DPD方案 系统方案之 带 方案RX LO GC5322 GC5325 GC5328 TX CAttenuatorsADS58C28DAC5682zTRF372017ADC ADCAttenuators LMH65xxGC532xDUC-CFR-DPD DUC-CFR-DAC DACI/Q ModulatorLOADS58B18/19 RX BADCFPGADSP C6727BPGA870MixerAttenuatorSupport 20MHzTLK3132 TLK6002 TLK10002SerdesEPIEP M3/ARMSVA CLOCKPowerUCD/TPSTI系统方案之 系统方案之2x2 MIMO LTE 系统方案之GC5322 GC5325 GC5328 RX LO DAC5682z TRF372017GC532xDUC-CFR-DPD DUC-CFR-TX 1DAC DACI/Q ModulatorLOADS58B18/19 Attenuators ADS58C28ADCPGA870 Mixer AttenuatorADC ADCAttenuators LMH65xxGC532xDAC5682z TRF370317DUC-CFR-DPD DUC-CFRRX BTX 2DAC DACI/Q ModulatorFPGADSP C6727BSupport 20MHzTLK3132 TLK6002 TLK10002SerdesEPIEP M3/ARMSVA CLOCKPowerUCD/TPSTI系统方案之 系统方案之2x2 MIMO LTE 系统方案之RX LOGC5330 GC5337DAC3482 DAC3484 TX 1TRF372017 /3705-02GC533xDAC DACADS58B18/19 ADS62PF49I/Q ModulatorLOAttenuatorsADS58C28DUC-CFR-DPD DUC-CFR-DDCADCPGA870 Mixer AttenuatorADC ADCAttenuators LMH65xxDAC3482 TX 2TRF370317/3705-02RX BDAC DACI/Q ModulatorFPGADSP C6727BGC5330 This Arch can support 2 x30MHz in HP mode 24 TX and RX channels( 12 channels per ANT) Note DSP can be shared for up to 4 GC5330 Support ET functionTLK3132 TLK6002 TLK10002SerdesEPIEP M3/ARMSVA CLOCKPowerUCD/TPSTI系统方案之 系统方案之Two 2x2 MIMO LTE 系统方案之GC5330 GC5337RX LO Attenuators ADS58C48 ADS58C28 DAC3484 TX 1/2 TRF372017GC533xDAC DACADS58B18/19 ADS62PF49I/Q ModulatorLOADC ADCDUC-CFR-DPD DUC-CFRADC ADCAttenuators LMH65xx TX 3/4ADCPGA870 Mixer Attenuator-DDCDAC3484 TRF370317DAC DACI/Q ModulatorFPGADSP C6748TLK3132 TLK6002 TLK10002This Arch can support 4 x15MHz in HP mode and 4x30MHz in HB mode 24 TX and RX channels ( 6 channels per ANT) No ET support Note DSP can be shared for up to 4 GC5330 SVA CLOCK PowerUCD/TPSSerdesEPIEP M3/ARMTI系统方案之 系统方案之MGSM DPD方案 系统方案之 方案RX LO GC5330 GC5337 ADS58C28 ADS58C23 ADS58C20 DAC34H84 DAC3484 DAC3482 TRF372017/3705-02AttenuatorsADC ADCAttenuators LMH65xxGC533xDUC-CFR-DPD DUC-CFR-DDCTX CDAC DACADS62PF49I/Q ModulatorLOADC ADCAttenuator DemodulatorFPGADSP C6748TLK3132 TLK6002 TLK10002SerdesEPISupport 30MHz BW UMTS-30MHzSVA CLOCK PowerUCD/TPSEP M3/ARMADC/DAC模拟接口 模拟接口Transformer interface to ADCR-C-R滤波器用于吸收ADC采样开关 导致的开关噪声(Glitch);如果你发现你 的信号输出带有毛刺,那么它就是Glitch. ADC模拟口内部集成有高带宽的滤波器, 如果你的中频比较低,可以再增加外部 滤波器,以增强效果。