Mentor工具

利用MENTOR 工具进行的PCBA制造可行性分析使用教程

3

Valor_NPI 目录的设置及开启

• • •

使用记事本打开Valor npi的安装目录的环境配置文件env_file ,(在开始菜单中输入 %sdd_home%\ Valor_NPI\e93 回车)添加“valor_console=1”与“LANG=GB”两行,这 样在运行时规则名称可以显示为中文,并且开启了控制台查看 设置完成之后,可以通过“开始”所有程序 Mentor Graphics SDD Valor Valor NPI来开启 valor 程序,也可以通过expedition pcb 的output中开启 License选择Molular

ODB++输出

以单机形式打开工程文件,在expedition PCB 的主界面找到OutputODB++

1

ODB++输出

输出层如图设置,以保证输出的文件 包含了工程的全部信息

2

Valor_NPI 目录的设置及开启

• • • • Valor_NPI环境设置,此设置只需要设置一次。 点击“开始”所有程序 Mentor Graphics SDD Valor SetValorDir,内容如图,将new valor dir 设置为“Y:/013A_DIDA3013/Valor_NPI” 然后点击updata 调整系统环境变量,“VALOR_ENV_FILE” 变量值为“Y:\013A_DIDA3013\Valor_NPI\env”

• 开启窗口后如图,使用默认设置分析即可 • 三个图标从左到右 依次是“全局运行 ”、“目前可视区 域运行”、 “profil行性分析

• 由于与既定的规则有冲突,按此图标即可显示检测结 果 • 单击一条规则,然后点击

利用MENTOR工具进行的PCBA制造可行性分析使用教程

利用MENTOR工具进行的PCBA制造可行性分析使用教程使用MENTOR工具进行PCBA制造可行性分析的教程概述:PCBA(Printed Circuit Board Assembly)制造可行性分析是为了确保在实际生产过程中能够成功制造出满足设计要求的电路板。

MENTOR是一款专业的电路板设计软件,它提供了一套全面的工具,可以帮助进行PCBA制造可行性分析。

本文将介绍如何使用MENTOR进行PCBA制造可行性分析。

步骤一:导入设计文件首先,打开MENTOR软件,点击文件菜单中的“导入”选项,选择需要进行分析的PCBA设计文件。

MENTOR支持多种PCBA设计文件格式,如PADS、Altium Designer等。

选择好文件后,点击“确定”按钮导入设计文件。

步骤二:定义制造要求在MENTOR的工具栏中,选择“制造可行性分析”工具,然后点击“新建”按钮创建一个新的分析项目。

在弹出的对话框中,填写项目名称和项目描述,并设置分析的工艺要求,如最小线宽、最小孔径等。

点击“确定”按钮完成项目定义。

步骤三:执行可行性分析在新建的项目中,选择需要进行可行性分析的电路板图层,如顶层丝印、顶层铜等。

然后点击“执行分析”按钮开始执行可行性分析。

MENTOR 会自动检测设计文件中的制造问题,并生成相应的报告。

步骤四:查看分析报告分析完成后,MENTOR会生成一个详细的分析报告,包含了所有发现的制造问题和建议。

点击报告菜单中的“查看报告”选项,即可打开分析报告。

可以通过报告中的索引和目录,方便地浏览报告内容。

步骤五:解决制造问题步骤六:导出制造文件当电路板设计文件经过修改后,没有出现任何制造问题时,可以导出制造文件。

在MENTOR的文件菜单中,选择“导出”选项,选择需要导出的文件格式和存储路径,点击“确定”完成导出。

结束语:使用MENTOR工具进行PCBA制造可行性分析可以帮助我们及时发现并解决设计中存在的制造问题,从而提高电路板制造的成功率和效率。

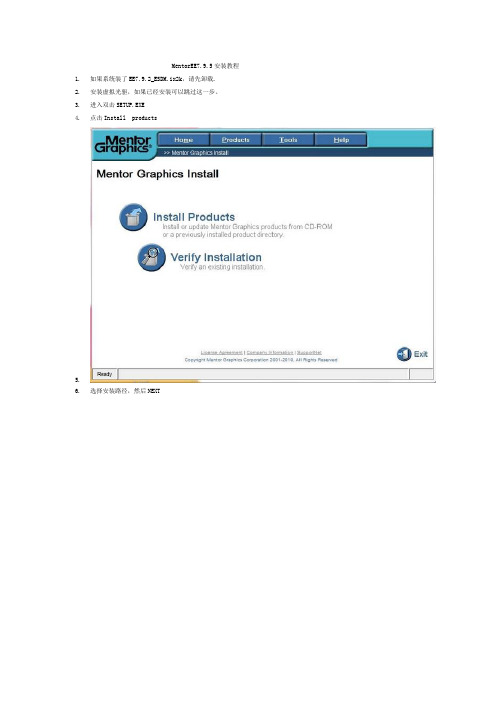

(完整)MentorEE7.9.5安装教程

MentorEE7.9.5安装教程

1.如果系统装了EE7.9.2_ESDM.ix2k,请先卸载.

2.安装虚拟光驱,如果已经安装可以跳过这一步。

3.进入双击SETUP.EXE

4.点击Install products

5.

6.选择安装路径,然后NEXT

7.

8.选择如图,Next

9.

10.由于是帮助文件,安装哪个自己选择,然后next

11.

12.出现下面窗口ok即可

13.

14.点击同意

15.

16.点击安装

17.

18.点击Done,帮助文件安装完成

19.

20.到了选择LICENSE的对话框,停在这里,去安装包里找破解工具MentorKG.exe

21.

22.双击破解工具,弹出CMD对话框,等着

23.

24.弹出LICENSE文件另存为license.dat,保存

25.

26.选择刚刚新建的license.dat,下一步

27.

28.C盘新建一个英文文件夹,名称随意,作为WDIR的文件夹

29.

30.点击Done,文件安装完成

31.

32.如果没有中心库,打开软件的时候选择否。

mentor的fastscan用法

mentor的fastscan用法Mentor的FastScan是一种用于快速扫描的工具,可以帮助用户快速找到所需信息。

它采用了先进的技术和算法,可以在海量数据中迅速搜索并提供准确的结果。

本文将介绍Mentor的FastScan的用法,并提供一些使用技巧和注意事项。

要使用Mentor的FastScan,用户需要安装并打开Mentor的软件。

在软件界面的搜索框中输入关键词或问题,然后点击搜索按钮即可开始快速扫描。

FastScan将立即开始搜索,并在几秒钟内提供结果。

FastScan的搜索结果以列表的形式呈现,每个结果都包含了相关的信息。

用户可以点击每个结果来查看详细内容。

在搜索结果中,用户可以看到标题、摘要和链接等信息。

用户可以根据自己的需求选择相应的结果进行查看。

在使用FastScan时,用户可以通过以下几种方式提高搜索效果。

首先,使用准确的关键词进行搜索。

关键词应该精确描述用户需要查找的内容,避免使用模糊的词语。

其次,可以使用引号将多个关键词组合在一起,以便更精确地搜索。

例如,可以使用“Mentor FastScan”来搜索与这个工具相关的信息。

FastScan还提供了一些高级搜索选项,使用户可以更精确地筛选搜索结果。

用户可以根据时间、地点、文件类型等进行搜索。

例如,用户可以通过选择特定的日期范围来搜索最新的信息。

在使用FastScan时,用户还需要注意一些事项。

首先,由于FastScan是一种快速扫描工具,搜索结果可能会显示较多的信息。

因此,用户需要根据自己的需求仔细选择结果。

其次,用户还需要注意信息的可靠性和来源。

在浏览搜索结果时,用户应该查看信息的来源,并对其进行评估和验证。

Mentor的FastScan是一种强大的快速扫描工具,可以帮助用户快速找到所需信息。

通过准确的关键词和适当的搜索选项,用户可以提高搜索效果。

然而,用户在使用FastScan时也需要注意信息的可靠性和来源。

希望本文对大家了解和使用Mentor的FastScan有所帮助。

mentor使用说明

mentor使用说明导语:导语部分是对所需说明内容的简要介绍,为读者提供整体的概念,并引起读者的兴趣。

本文将介绍一种名为“Mentor”的应用程序的使用说明。

Mentor是一款以导师-学生关系为基础的教育辅助应用程序,旨在帮助学生获得更好的学习体验并提高学业成绩。

本文将详细介绍Mentor的功能和使用方法,以便读者可以充分利用该应用程序。

1. 介绍MentorMentor是一款基于智能手机的教育辅助应用程序,主要用于学生与导师之间的交流和互动。

学生可以通过该应用程序与导师进行文字、语音和视频交流,向导师寻求学习建议和指导。

2.注册和设置个人资料3.寻找导师一旦注册并设置了个人资料,用户可以开始寻找导师。

Mentor提供了一个导师功能,用户可以根据导师的学科领域、评分和费用等条件进行筛选。

用户还可以查看导师的个人资料,了解其教育背景和教学经验。

5.学习辅导除了与导师进行交流外,Mentor还提供学习辅导的功能。

用户可以通过应用程序获取学习资料、参加在线课程或是解决特定的学习问题。

Mentor还提供学习资源的推荐和学习计划的制定,帮助用户更好地组织和管理学习时间。

6.管理学习进度Mentor帮助用户跟踪学习进度并为用户制定学习计划。

用户可以记录已完成的任务和学习成果,了解自己的学习进度。

用户还可以设置提醒以及定期检查学习计划,确保自己按时完成学习任务。

7.提供反馈和评分Mentor鼓励用户与导师进行积极的互动,并提供反馈和评分机制。

用户可以对导师的教学质量和服务态度进行评价,帮助其他学生选择合适的导师。

同时,用户也可以接收导师的反馈和评价,以便改善自己的学习方式和方法。

8.保护个人隐私和安全Mentor非常注重用户的个人隐私和安全。

应用程序采用加密技术保护用户的个人信息和通信内容,防止任何未经授权的访问。

此外,Mentor 还提供了举报机制,让用户可以报告任何违规或不当行为。

结语:结语部分对上述说明进行总结,并提供进一步帮助的渠道。

利用MENTOR工具进行的PCBA制造可行性分析使用教程

利用MENTOR工具进行的PCBA制造可行性分析使用教程MENTOR是一款常用的PCBA设计和制造工具。

它可以帮助工程师进行电路板设计、布局和制造的各个环节。

在这篇教程中,我将介绍如何使用MENTOR工具进行PCBA制造可行性分析。

1.准备工作在开始使用MENTOR进行PCBA制造可行性分析之前,需要准备以下材料和软件:-一台计算机,安装有MENTOR软件。

-PCB设计文件。

- BOM(Bill of Materials)文件,用于列出所需的元器件和材料。

-制造工艺规范,包括焊接、印刷、组装等细节。

2.导入PCB设计文件首先,打开MENTOR工具,并导入已完成的PCB设计文件。

在软件的菜单栏中选择“文件”>“导入”>“PCB设计文件”,然后选择所需的PCB设计文件进行导入。

3.导入BOM文件接下来,导入BOM文件以获取所需的元器件和材料清单。

在软件的菜单栏中选择“文件”>“导入”>“BOM文件”,然后选择所需的BOM文件进行导入。

MENTOR将自动将BOM中的元器件与PCB设计文件中的对应元件进行匹配。

4.进行制造可行性分析一旦PCB设计文件和BOM文件都导入成功,就可以开始进行制造可行性分析了。

在软件的菜单栏中选择“制造”>“可行性分析”。

MENTOR将根据PCB设计文件、BOM文件和制造工艺规范进行分析,并生成制造可行性报告。

在制造可行性报告中,MENTOR将列出以下信息:-PCB设计的制造可行性评估,包括焊盘尺寸、间距、最小线宽/线距等。

-元器件的可用性评估,包括元器件的供应状态、替代品等信息。

-制造流程的可行性评估,包括印刷、组装、测试等工艺的可行性。

5.优化PCB设计和制造过程根据MENTOR生成的制造可行性报告,可以对PCB设计和制造过程进行优化。

例如,如果报告中指出一些焊盘尺寸太小,可能导致制造困难,可以根据报告建议调整设计。

如果报告中指出一些元器件供应状态不稳定,可能会导致生产延迟,可以考虑替换为可靠的替代品。

MentorGraphics工具使用的几点心得

MentorGraphics工具使用的几点心得作为Mentor Graphics工具的用户,我在使用过程中总结了一些心得体会。

首先,Mentor Graphics提供了广泛的电子设计自动化工具,包括PCB设计、电气布线、印制线路板生产等领域,所以在使用之前需要了解各个工具的应用场景和功能特点。

其次,对于初次接触Mentor Graphics工具的人来说,可以从学习和使用Capture软件开始。

Capture是一款用于原理图设计和电路仿真的工具,非常适合初级用户使用。

在使用Capture时,我发现最重要的是理解电路的结构和原理,并且要仔细阅读软件的帮助文档。

另外,对于一些复杂的电路设计,可以先画草图,然后逐步将其转化为Capture中的元件和连线。

除了Capture,我还使用了Mentor Graphics的Layout工具进行PCB 设计。

在进行布线之前,我首先需要对电路板的尺寸、层数、电源要求等进行全面的规划。

在进行布线时,我通常会按照信号的传输速度和重要性来确定电路板上的信号路径和阻抗匹配要求。

此外,合理的分层设计和有效的地平面规划也是保证信号完整性的重要手段。

在使用Layout工具过程中,我还发现使用布线规则检查功能非常有用。

这个功能可以帮助我们检查布线是否符合规范,并给出相应的错误提示。

要注意的是,布线规则检查只是辅助工具,最终设计的质量还是要靠人工的判断和优化。

除了基本的设计工具,Mentor Graphics还提供了一些辅助工具和功能,比如PCB封装库管理、3D模型导入等。

在使用这些工具时,我发现保持库文件的更新和整理非常重要,可以提高设计效率和减少错误。

此外,Mentor Graphics的技术支持也是一个很重要的资源。

他们提供了丰富的培训教程、用户社区、在线帮助等,可以在使用过程中快速解决问题。

在遇到问题时,可以通过相关的解决方案,或者向技术支持人员提问。

当然,也可以借助其他用户的经验和意见来解决问题。

Mentor Graphics AMS for Linux 电路设计工具简介

└┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┴┘

System design

Block validation

├ ┤

├ 按CTRL+F搜索,不要输入版本号,或按下联系方式找王小姐咨询 ┤

├ ┤

├ 在线客服: ┤

2007还提供更强大的工具能力,工程师无论在数位为主 (digital-centric) 或是类比为主 (analog-centric)

的设计流程中,都能验证他们的设计,确认其功能符合原始规格。

AMS

2007版现能为八种语言提供完整支援,包括SystemVerilog、SystemC、VHDL、Verilog、SPICE、VHDL-AMS、Verilog-AMS以及C语言,让使用者能在单一模拟环境中,执行从系统规格阶段到后布局验证阶段的功能方块层级检查及全晶片功能验证。

Mentor透过AMS 2007提供一个共同平台,以便扩大数位验证和类比验证,支援混合讯号设计。它能支援数位为主的验证,例如测试平台

(testbench),包括定向测试 (directed testing)

和准随机测试;它能支援类比为主的验证,例如电路模拟,包括直流、交流、暂态、参数、Monte Carlo以及边界条件

├ MSN: caxcai@ ┤

├ ┤

├ 邮件:caxcai@ ┤

enables top-down design and bottom-up verification of multi-million

gate analog/mixed-signal system-on-chip designs.

ADVance MS RF

mentor中文教程

一、原理图的绘制:1、建立一个project:打开Design capture → project → new →指定project名和project路径→新建一个project → project/settings:●Central library:指定该project的库文件路径并选择库的类型;●Design:指定各种设计文件存放路径,最下面一行“Absorb instanse data into……”处于选中(打勾)状态,执行“Forward Annotation”时CDB会重新生成(否则需要cdb complier生成cdb);如果block很多时,不要选;●File locations:配置文件管理;●Libraries:指定Central library后,不用管这里;2、file → new →选择“schematic”:新建一个原理图;3、改变原理图尺寸大小:● Place →symbol →选择border →选择期望的尺寸→放在坐标(0,0)处;●view → select filter →点击“select all”→点击原理图中原有的边框→选中并删除→ select filter中点击“reset”(把不可选的东西去掉);说明:编辑原理图设计时间、版本等信息也要先选中再编辑;4、设置库属性和pcb的一些特性(一定要在进行设计前完成):Library manage → edit → property verification →选择原理仿真、热仿真等;Library manage →setup →setup parameters →(一般只能看)5、画原理图:● project →global signals:定义电源网络(net);● Verify →compile CDB →package design →进入expendition pcb二、pcb中pcb文件的建立和网表调入:1、pcb文件建立:file →new →根据job management wizard来建立;2、调入网表:●打开新建的pcb文件,运行forword annotion(或者运行design capture中的PCBintegration);●edit →place →part :在“unplaced”前打勾→选中所有元器件→点击“》”图标把所有元器件放到“active”框中→ apply →左键拖动点击→元件件以及网络连接都到pcb中了;●改动了原理图之后调入网表:在capture中先保存→verify →compile CDB →package design (tools中)→ pcb integration(project中),要执行forword annotation →在pcb中用上述方法把元器件加到pcb文件中;3、修改pcb层数:setup →setup parameters :general →layers →number of physical 中数字改为希望的层数(如“2”)→点击右面的“remap layers”图标→在弹出框中点击“ok”→点击右下角的“apply”→完成设置;4、修改pcb尺寸:在draw mode下拖动原有的板框即可,或者选中框→右键→编辑框属性→修改尺寸,draw mode切换方式如下:注:1、红色框是pcb框,淡兰色框是布局、布线区;2、将尺寸设置为mm:setup →setup parameters→general →右侧→选;Expendition pcb 中常用操作1、选择重叠的不同层的元器件等:左键点住+tab;2、布线:点击工具栏的“route mode”图标(见下图),在器件引脚处点住左键拖动一小段即可(“esc”结束布线、双击切换布线层、单击后可以拐弯);印制线位置调整:在“Route mode”下选中印制线拖动即可;3、设置最小移动距离等:setup→edit control→grids→palcement related 第二行改数字;4、自动布线:进入“route mode”→印制线全选(点住左键画个大框)→del :删除印制线;route →auto route →设置→点击下面的“route”按钮即可;5、自动放置测试点:route →test piont →auto assign →在相应 net 右面required下设置需要的个数→点击“place”按钮即可;注:要在 setup →setup parameters→general 右下角“test piont settings”中设置好测试点的类型等;cell是测试点类型,test选择测试点放在哪一面,ref des 中填写自动命名测试点的前缀;6、铺设地线层:route →planes →place shape →画一个框→在drawing mode下选中该框,点击右键编辑其属性:定义框的网络属性(选择一个net),定义框在哪一层;route →planes →processor →在弹出框中定义“铺设(hatch)”方式→ok●左面:定义同一 net 名的焊盘和过孔的连接方式;●右面:定义clearance(一般25 th);●右下角的工具框:定义印制线 hatch 的宽度和方式;禁布铜皮:edit →place →plane obstruct →画一个框即可;hatch时自动让开;注意1:setup →setup parameters →planes中可以定义某一层为某个net 的planes,设定planes的net只要把希望的net选入“included nets”中即可(当心:只可以选择一个net);不定义“planes层”照样可以“hatch”;注意2:只在“All on”和“display schemes”pcb显示方式下才可以看到铺设的铜皮;7、删除所有的铜皮和导线:都在route下拉菜单下;8、布置泪滴:route →teardrops →设置参数→ apply ;删除泪滴:edit →add to select set → teardrops →按“delete”即可删除;如果不行,再edit →unfix →按“delete”注意:如果pcb空间不够,就不会生成泪滴;9、pcb开槽:“draw mode”下画一个闭合的框,定义其属性为drill drawing ( through )即可;要在view →display control →general 中设置drill drawing层的显示颜色,否则会看不到;Analog design 使用mentor的原理图仿真不需要设计仿真模型,只要按照正常设计来画原理图即可(用于生成网表、调入pcb文件);用于仿真时,只要根据设计选择不同的“source”和“load”,同时设置连接位置(net)就可以了(比pspice、saber要高级);仿真时先打开“project”,然后设置仿真“setup”文件(需要 new、save等,“.vas”文件);仿真“setup”文件包括:source和load的选择和分配、仿真类型选择(进行哪些仿真)、仿真计算哪些输出(monitor)、算法设置等;设置好“setup”文件(.vas)要保存才可以仿真;1、画好原理图,进行一些编译工作(“compile CDB即可”);2、设置输入信号以及信号参考点:进入project →global signals,先指定仿真时的电压参考:选择一个net,“suply attribute”设为“gnd”,仿真时即把该点作为参考电平;指定仿真输入点:选择一个net,其电源属性里选择“positive”或“negtive”;注意:仿真setup文件中“source”中用到的net都要在“global signals 中设定属性”);所有电平参考也要在其中设定“gnd”属性。

使用mentor软件的体会

使用Mentor公司PCB设计工具(DxDesigner及Expedition PCB)的设计体会根据课题需要,我们要搭建一个雷达信号处理的硬件平台。

在此平台上,有4个DSP(C’6203)及多个高速同步RAM,总线频率100Mhz。

我们选用我所新近购买的Mentor公司的PCB工具作为设计手段,目的是熟悉使用该软件,进行必要的仿真,使设计能够尽可能一次成功。

经过3个多月的工作,我们最终完成了两块10层板的设计工作。

这段时间中,对Mentor的Dxdesigner及Expedition PCB进行了熟悉使用,现将这段工作的设计体会进行简单的总结。

关于Expedition的设计思想对于大部分硬件工程师来讲,PCB设计使用最多的恐怕就是protel,因此在使用Expedition 做PCB设计时不自觉的就会把两者设计思想进行比较,从本质上来讲,两者并无什么不同,都是符号,封装,互连关系,但是在具体形式上,Expedition比起Protel要更为细致。

Protel 在设计时只需要两个库:符号库及封装库,原理图设计时在元件的属性中进行两者的对应,然后生成网表文件,就可以带入到PCB中进行布局布线,如图1所示。

与此不同,Expedition中引入了中心库(Central library)的概念,符号(Symbol)与封装(Cell)的对应是在中心库中完成,形成器件(Part)。

可以说,中心库是整个设计的基础,从焊盘定义,封装制作、符号与封装的对应,都在中心库中完成。

在进行原理图设计时,可以从中心库中调符号,当然也可以自己建立本地符号库,但是在进行编译之前,要用中心库中的符号代替自己建立的符号,并在符号的属性中指定与中心库中Part的对应关系,同时指定中心库路径,这样才可以完成编译,进入下一步PCB的流程(图2)。

前端输入工具(DxDesigner)我所购置的Mentor软件的前端管理工具是DxDesigner。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Mentor Graphics各大系列系统单芯片验证系列硬件描述语言的仿真、硬件与软件的协同验证、多核心内嵌式系统的除错以及「可测试设计」(Design-for-Test)等。

●Seamless:可提供早期而精确的硬件/软件协同验证;●Nucleus:嵌入式实时操作系统;●XRAY:芯片制造前与制造后的软件除错工具;●FastScan:芯片测试资料的自动产生工具;●VStation和Celaro:硬件仿真工具/虚拟原型建构系统。

硬件描述语言与FPGA设计VHDL及混合硬件描述语言的仿真、FPGA组件的合成、以及设计的捕捉与管理等;在百万逻辑闸等级的FPGA设计领域里,能够提供整合式设计解决方案。

●ModelSim:提供数字仿真的功能;●HDL Designer Series:设计的输入、分析与管理工具;●Precision Synthesis:强大的FPGA合成解决方案。

实体设计与分析设计人员必须克服深次微米制程技术带来的许多复杂实体效应所产生的影响,才能把设计转换为实际的芯片。

●Calibre:速度最快且结果最精确的深次微米设计实体验证工具;●Calibre OPC与PSM:次波长光学制程修正及相偏移光罩的发展工具;●ADvance MS:混合模拟讯号设计解决方案;●Eldo:晶体管阶层的仿真工具;●EldoRF:射频分析工具;●IC Station:全订制型集成电路设计与察看的整合式工具流程。

电路板与系统设计●Board Station系列:不受限制的企业设计环境;●Expedition系列:最适合个别设计人员或小型工程团队的设计环境;●AutoActive RE:最佳的绕线作业环境,不但能立刻增加工程师的生产力,还能与Expedition及Board Station整合在一起;●DMS:数据管理系统。

工具简介设计技术平台Mentor Graphics公司面向“IP/ASIC/SoC设计环境平台”提供定制IC芯片设计技术、混合信号混合语言SoC的仿真验证技术、FPGA与PCB设计技术、系统设计技术等。

●定制IC设计领域Mentor Graphics公司提供DA-IC、IC Station、Eldo以及Calibre等技术和产品构成完善高性能的定制IC设计全流程;●混合信号混合语言的IC/ASIC/SoC仿真验证提供行业最著名并且支持最完备的ADMS环境平台,支持包括C、SystemC、SystemVerilog、Verilog、VHDL、SPICE等在内的广泛设计抽象的完整的芯片级验证和分析;●大规模复杂的数字ASIC和SoC设计Mentor Graphics公司领先的仿真验证技术、硬件软件协同验证技术、DFT技术、物理验证技术以及硬件仿真器技术都是行业最领先的解决方案,并且成功地应用在广泛的设计实践中;●芯片和模块封装有SuperMax产品系列,支持集成电路芯片、MCM以及混合电路的封装设计和分析;●系统设计Mentor Graphics处在行业的最前沿,包括FPGA设计技术FPGA Advantage、板级系统设计技术DxDesigner/Expedition、系统物理分析技术以及嵌入式软件技术等。

设计规则与物理验证为了保证集成电路设计的成功流片及具有更高的成品率,代工厂商都会依据工艺水平设定众多的设计规则,对版图图形进行约束。

由于采用的工艺不同,代工厂商不同,因此设计规则也不尽相同。

设计规则主要取决于代工厂商加工工艺,即使采用相同的工艺。

在设计过程中,由于人为或者工具的因素,不可避免会违反设计规则,要确保设计的质量,必须进行物理验证,确保整个设计都是满足设计规则的。

物理验证主要包含三部分的工作,即DRC(Design Rule Check)、LVS(Layout VS Schematic)和PEX(Parasitic EXtraction)。

1.DRC主要进行版图设计规则检查,也可以进行部分DFM(Design ForManufacture)的检查(比如金属密度,天线效应),确保工艺加工的需求;2.LVS主要进行版图和原理图的比较,确保后端设计同前端设计的一致性;3.PEX则主要进行寄生参数的提取,由于在前端设计时并没有或者不充分的考虑金属连线及器件的寄生信息,而这些在设计中(特别是对于深亚微米设计)会严重影响设计的时序、功能,现在要把这些因素考虑进来,用仿真工具进行后仿真,确保设计的成功。

●物理验证工具Calibre DRC/LVSCalibre是业界所公认的深亚微米及纳米设计和半导体生产制造中物理验证的行业标准。

Calibre提供了快速准确的设计规则检查(DRC)、电气规则(ERC)以及版图与原理图对照(LVS)功能。

Calibre独到的层次化架构以及多项行业领先的专利技术大大简化了复杂ASIC/SoC设计物理验证的难度。

Calibre的核心专利算法兼顾平面式处理技术与层次化处理技术相结合的结构特点。

用户不需要针对芯片设计的类型来进行特殊设置,同时也可以根据直观、方便的物理验证结果浏览环境迅速而准确地定位错误位置,并且与版图设计工具之间紧密集成实现交互式修改、验证和查错。

Calibre的并行处理能力支持多CPU运算,能够显著缩短复杂设计验证的时间。

与其相对应的工具有Synopsys的Hercules和Cadence的Assura。

Calibre物理验证系列●Calibre DRC●Calibre DRC-H●Calibre LVS●Calibre LVS-H●Calibre Multithreaded●Calibre CI●Calibre Interactive●Calibre DESIGNrev●Calibre RVE/QDB-H●Calibre MGCCalibre寄生参数提取系列●Calibre xRC●xCalibrate●Calibre xRC-CBDFT测试设计系列DFTAdvisorDFTAdvisor利用友好的图形用户界面引导完成可测性分析并优化测试结构的插入,执行全面的测试规则检查,从而保证在ATPG之前不存在任何遗留的可测性设计问题。

DFTAdvisor 测试综合工具自动插入测试结构电路,支持全扫描或部分扫描的测试逻辑,能够自动识别电路中的时序单元并自动转换成可扫描的单元,并能够把电路中可扫描的单元串接成扫描链,从而大大增强了IC和ASIC设计的可测试性。

此外,利用它在设计过程的早期阶段进行可测性分析,测试综合生成和测试向量自动生成之前发现并修改违反测试设计规则的问题,尽可能提高ATPG的效率并缩短测试开发的周期。

主要特点:1、支持多种形式的设计输入。

包括GENIE,EDIF,TDL,VHDL,Verilog;2、支持Mux-DFF、Clocked-Scan和LSSD扫描结构;3、支持多种扫描结构的插入。

包括全扫描结构,多种可选的部分扫描结构和自动测试点的插入;4、支持智能化的、层次化的测试逻辑的自动化插入;5、通过密集的基于仿真的测试规则检查(超过140条测试规则)来确保高效率的可测性分析;6、通过自动测试点插入与综合来加强设计的可测性;7、通过插入测试逻辑电路自动纠正设计中违反可测性设计规则的部分;8、支持版图层次上的扫描链单元的次序控制,以提高测试逻辑插入过程中的时序有效性;9、为后续的ATPG过程提供充分支持,生成ATPG工具要求的全部SETUP 文件DFTInsightDFTInsight是与Mentor Graphics的ATPG工具包紧密集成的图形化调试工具,提供了方便的可测性问题的图形化调试手段。

在DFTAdvisor、FastScan或FlexTest 中都可调用DFTInsight生成电路图窗口显示信息,快速确定和解决可测性问题。

它的电路图显示可以智能地将层次化设计的其它信息屏蔽,而只显示与可测性问题有关的电路。

它根据标准网表信息生成电路图,不需要特殊的电路图符号支持,这个功能意味着DFTInsight能够以即插即用的方式插入用户选择的设计环境中。

主要特点:1、通过图形化分析加速ASIC与IC的可测性调试;2、根据设计规则检查结果进行原理图的动态划分,定位出可测性问题的发生位置;3、根据故障分类信息结果进行原理图的动态划分,定位出ATPG工具没有覆盖的故障所在位置;4、根据ATPG工具分析ATE机上失败的测试向量结果来帮助定位芯片上的故障位置;5、可以在原理图上通过部件间的交互选择与跟踪来检查设计;6、无需专门的库支持来进行原理图显示;7、与FastScan、FlexTest和DFTAdvisor紧密集成FastScanFastScan是测试向量自动生成(ATPG)工具,为全扫描IC设计或规整的部分扫描设计生成高质量的的测试向量。

FastScan支持所有主要的故障类型,它不仅可以对常用的Stuck-at模型生成测试向量,还可以针对关键时序路径、transition模型生成at-speed测试向量、针对IDDQ模型生成IDDQ测试向量。

此外FastScan 还可以利用生成的测试向量进行故障仿真和测试覆盖率计算。

主要特点:1、支持对全扫描设计和规整的部分扫描设计自动生成高性能、高质量的测试向量;2、提供高效的静态及动态测试向量压缩性能,保证生成的测试向量数量少,质量高;3、支持多种故障模型:stuck-at、toggle,transition、critical path和IDDQ;4、支持多种扫描类型:多扫描时钟电路,门控时钟电路和部分规整的非扫描电路结构;5、支持对包含BIST电路,RAM/ROM和透明Latch的电路结构生成ATPG6、支持多种测试向量类型:Basic,clock-sequential,RAM-Sequential,clock PO,Multi-load。

7、利用简易的Procedure文件,可以很方便地与其他测试综合工具集成;8、通过进行超过140条基于仿真的测试设计规则检查,保证高质量的测试向量生成;9、FastScan CPA选项支持at-speed测试用的路径延迟测试向量生成;10、FastScan MacroTest选项支持小规模的嵌入模块或存储器的测试向量生成;11、FastScan Diagnostics选项可以通过分析ATE机上失败的测试向量来帮助定位芯片上的故障;12、ASICVector Interfaces选项可以针对不同的ASIC工艺与测试仪来生成测试向量FlexTestFlexTest的时序ATPG算法使它在部分扫描设计的ATPG领域拥有巨大的优势,可以显著提高无扫描或全扫描设计的测试覆盖率。

其内嵌故障仿真器可以估计功能测试向量的故障覆盖率,然后在此基础上生成部分扫描电路结构的时序ATPG。