MENTOR_WG2005中文翻译指导

tutor翻译

tutor翻译基本解释●tutor:导师,辅导教师●英音:[ˈtjuːtə(r)] 美音:[ˈtuːtər]●n. 导师,辅导教师●v. 辅导,指导变化形式●n. 复数形式:tutors●v. 第三人称单数:tutors●过去式:tutored●过去分词:tutored●现在分词:tutoring具体用法●●名词:o导师,辅导教师o同义词:instructor, mentor, coach, guide, teacher o反义词:student, learner, pupil, novice, beginnero例句:●The university assigned a tutor to help the students with theircoursework, ensuring they understood the materialthoroughly.●大学为学生分配了一位导师,帮助他们完成课程作业,确保他们彻底理解材料。

●As a tutor, she was responsible for guiding her studentsthrough complex mathematical concepts and ensuring theywere well-prepared for exams.●作为一名导师,她负责指导学生理解复杂的数学概念,并确保他们为考试做好充分准备。

●The tutor met with his students twice a week to review theirprogress and address any questions they had about thesubject matter.●导师每周与学生见面两次,审查他们的进展,并解决他们对课程内容的任何疑问。

●He worked as a private tutor, offering personalized lessons tostudents who needed extra help outside of school hours.●他作为私人导师工作,为需要课外额外帮助的学生提供个性化课程。

LAYOUT交互和转化

PADS、OrCAD、PowerPCB、Protel选择随心所记2009-11-19 15:13:30 阅读213 评论0 字号:大中小现在市面上流通的eda软件比较多,而且优劣不一,我们只谈谈用的最多最广的几种吧。

1、protel无疑是最早接触的eda软件了,在大部分大学里都有protel软件的课程,但是不得不承认,protel在eda软件家族中的确是最低端的软件之一,制作单面板,两层板尚能得心应手,但是4层就开始感觉到不好用了,更多层就更不必说了,如果面对高频高速的多层板,能用protel做出高质量的板子的人是相当不错的:)protel在未来的日子会不会被淘汰不好说,现在使用protel的人还是有相当的市场的.学习PROTEL是学习高端PCB软件的基础。

2、pads即powerpcb,我把它称作低端中的无冕之王,它是我认为在所有低端的pcb软件中最优秀的一款,好用,易上手,做出的板子质量不会比wg,allegro 等逊色,现在市场上使用范围最广的一款eda软件,适合大多数中小型企业的需求。

3、orcadorcad的pcb比protel还要差,但是orcad的原理图设计部分capture CIS被业界视为最优秀的原理图工具之一,界面好看,易上手,操作方便,仿真等功能强大,如果和dxdesigner相比在使用方面,我觉得是占上风的,只是dx有非常好的管理功能,集成环境,原理图复用等功能。

4、wgmentor公司的产品,最新出了WG2005,基于windows平台,在中高端的几个软件在功能方面没有很大优劣差别的情况下,只有拉线爽的软件才是好软件,而WG2005正是拉线最爽的软件,被誉为拉线之王,它的自动布线功能非常强大,布线规则设计非常专业,expeditionPCB是WG的pcb核心部分,WG2005包含了DX,DC,DV,LIB,EXP等部分部分。

5、en同为mentor公司的产品,最新推出的EN2004,因为是基于unix平台的产品,而且市面上没有中文教材,软件学习难度较大,令很多人望而却步;它的专业程度决定了它不适合中小型企业,特别是小型企业,因为没有这个需要,一碗水就能熄灭的火干吗要爬山走远路去更远的河里去取,对不对,况且这个软件本来就是为大型企业设计的,因此没有这个需要的朋友不必去费心费力的,如果工作需要的话就另当别论了,原理图是epd2004,基本上,它最重要的是集成管理体系。

mentor使用说明(中文)

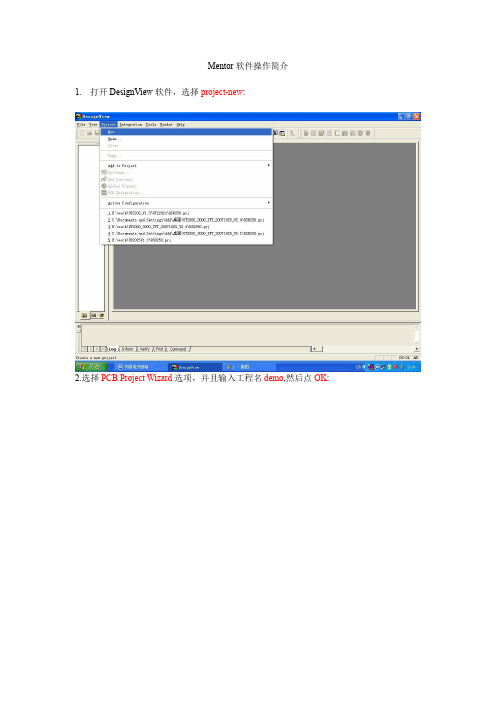

Mentor软件操作简介1.打开DesignView软件,选择project-new:2.选择PCB Project Wizard选项,并且输入工程名demo,然后点OK:然后点下一步:4.鼠标点击Add,添加已有的设计文件,然后点下一步:5. 用鼠标勾掉Use CES for constrain前面的√,然后点完成:6. 以上设置完成后,新工程就建好了,如下图所示:7. 接着要新建原理图,选择File->new,然后点击鼠标左键:8. 在弹出的菜单选择Schematic,然后点OK:9. 出现如下新建的原理图:10. 接着开始画原理图,先放元器件,将鼠标移动到下图所示的图标:11. 这时会弹出一个选择框,根据你设计的要求选择,如果你要布的是4层板就选4Layer Template,然后点OK:12. 如下图,将Partition下拉菜单改为[ALL]:13. 在Parts found表格中用鼠标左键选择需要的元件,同时会在右边显示该元件的symbol(符号)和cell(封装),比如选择Part Number为1206的元件,然后Place如下图:14. 在合适的地方点击鼠标左键来放置此元件:15. 然后出现如下的画面,表示如果再按一下鼠标左键会继续放置此元件,本例不需要,故按键盘上的Esc:16.按了Esc后又出现之前的画面,接着你可以继续放置需要的元件,操作过程与上同,不再赘述:17. 鼠标左键选择如下图中的四个图标可以对元件旋转:18. 若要放置一些没有CELL的特殊元件,如GND符号,可以用鼠标左键点击下图中的图标,弹出Symbol Menu窗口,在里面找到GND这个符号放到原理图上,如下图:19. 接着用同样的方法放置VCC符号,全部元件放好如下图所示:20. 元件放好后开始连线,用鼠标点击可以开始连线,在元件的一端点鼠标左键开始连线,在目标处再点鼠标左键结束本次连线,连好后如下图所示:21. 这样本次原理图就画完了,然后鼠标左键点如下图中的图标保存此原理图:22.弹出如下图的窗口,输入文件名保存:23. 输入完成后,如下图所示,鼠标单击保存(S):24. 鼠标单击Yes:25. 此时软件窗口如下图显示:26. 鼠标选中demo_schematic,右键选择Open in Pcb:27. 在弹出的窗口中选中,然后点:28. 在接下来的窗口中设置最初我们建立的demo.prj工程文件的路径,鼠标单击下图的按钮来设置:29.选中如下图所示的demo.prj文件,点打开(O):30. 在接下来弹出的窗口中直接选择:31. 在接下来弹出的窗口中直接选择:32. 在接下来弹出的窗口中直接选择:33. 接着将出现如下图所示的窗口,直接点OK:34.在接下来弹出的窗口中直接选择:这样才能将原理图里的元件放到PCB中来,所以这步是必须的:36. 上一步完了后,原先,现在变成了,表示原理图和PCB同步起来了:形),选中下图中图标(画图模式):38. 然后点击下图中(属性图标),弹出窗口:39. 在Type下拉菜单中选择:40.然后在PCB中用鼠标左键画出一个封闭的:41. 画完后,如下图所示:42. 接下来就可以放元件了,点击图标,如下图所示:43. 在弹出的窗口中勾选前面的,如下图所示:44. 选中位号为L1和U1的元件,如下图:45. 然后点击旁边的图标,就把刚选中的LI和U1元件导入到active框中了,接着点击按钮开始放置LI和U1元件,如下图:46. 然后出现下图的情景,我们在合适的位置单击鼠标左键就放好L1元件了,接着在其他地方再单击鼠标左键就放好U1元件了:47. 放好元件后如下图所示:48. 为了在PCB上看的比较直观,我们把一些用处不大的东西隐藏起来,单击鼠标右键,选择Display Control选项,如下图:49. 在弹出的窗口中选择Part选项,勾掉和和这三行上的√,如下图:50. 上面的设置以后,PCB上的元件就看起来比较直观了,如下图所示:51. 我们看到PCB上L1(其实就是元件L1的位号)字符有两个一模一样的,就删掉其中任意一个,然后在剩下的L1字符上双击鼠标左键,如下图:52. 在弹出的Properties窗口中设置和,表示将此位号L1的字高设为30mil,线宽设为5mil,如下图:53. 同理设置位号U1,完成后如下图:54. 接着点击图标,切换到布线模式,接下来开始布线了,如下图:55.点击图标,开始一次布线,如下图:56. 在L1元件的1脚(1:S)单击鼠标左键,开始拉线,如下图:57. 然后在元件U1的1脚(1:L)上单击鼠标左键,完成拉线,如下图:58. 完成以上操作后,如下图所示:59. 接下来开始敷铜,鼠标单击菜单,在弹出的子菜单中选择选项,如下图:60. 然后点击图标,如下图:61. 在弹出的Properties窗口中选择Layer 为1,Net为GND,如下图:62.然后使用鼠标左键在元件U1的周围画出一个封闭的敷铜外形,如下图:63. 完成后的敷铜外形如下图中的虚线框:64. 同理,画出Net为VCC的另一个敷铜外形,鼠标单击菜单,在弹出的子菜单中选择选项,如下图:65. 在弹出的Properties窗口中选择Layer 为1,Net为VCC,然后使用鼠标左键在元件L1的周围画出一个封闭的敷铜外形,如下图:66. 完成后的敷铜外形如下图中的虚线框:67. 两个敷铜外形都已画完,现在开始生成敷铜,鼠标单击菜单,在弹出的子菜单中选择选项,如下图:68. 在弹出的窗口中勾选和以及之前的√,如下图:69. 然后点击按钮,开始敷铜,如下图:70. 敷铜完成后弹出如下提示信息,点确定,如下图:71. 敷铜完成后如下图所示:72. 接下来生成丝印层,鼠标单击菜单,在弹出的子菜单中选择选项,如下图所示:73. 在弹出的菜单中按下图设置,然后点击OK按钮:74. 弹出生成成功的提示信息,如下图,点击确定:75. 接下来生成NC Drill文件(转孔文件),鼠标单击菜单,在弹出的子菜单中选择选项,如下图:76. 在弹出的窗口中选择的路径,点击图标,如下图:77. 我们选用公制格式的,所以在下图窗口中选择DrillMetric.dff文件,然后点击打开:78. 然后选择选项,如下图设置:79. 设置好后,点击OK按钮,弹出成功提示信息,点击确定,如下图:80. 生成转孔文件后如下图所示:。

candence、Mentor,Altium三家公司的软件分析之二

candence、Mentor,Altium三家公司的软件分析之⼆Cadence公司产品Cadence 公司的产品这⼏年变化很快,存在了 Orcad/SPB/PSD 等多个系列,很多⼈初学者就会疑惑 Orcad 是什么、SPB 和 PSD ⼜是什么?其实三者都是 Cadence 公司基于 capture 和 allegro 的 PCB 设计套件,区别仅在于软件配置。

Orcad 的配置是低端产品,存在价格低的优点,但是在 Orcad 中 Allegro 的功能⽐较弱,只有各项基本功能⽽没有 constrain manager,假如需要 SI 或者 constrain manager 呢,就需要另外的增加配置了。

PSD 和 SPB 其实是同⼀个东西,PSD 是 Allegro 系统互连设计平台的早期版本,后来新出的版本叫做 SPB,因为改进了设计理念,所以修改了套件包的名称。

由此⼤家因该明⽩了,SPB 是 Allegro 最全功能的版本。

Cadence 公司的推出的 SPB(Silicon Package Board)系列,原理图⼯具采⽤ Orcad CIS 或 Concept HDL,PCB Layout 采⽤的是Allegro。

衡量⼀个软件的优劣,其中⼀个很现实的标准就是看它的市场占有率,也就是它的普及和流⾏程度.Cadence Allegro 现在似乎成为⾼速板设计中实际上的⼯业标准,被很多⼤型电⼦通信类公司采⽤,板级电路设计系统:包括原理图输⼊、⽣成、模拟数字/混合电路仿真,fpga 设计,pcb 编辑和⾃动布局布线 mcm 电路设计、⾼速 pcb 版图的设计仿真等等。

包括:* Concept HDL 原理图设计输⼊⼯具,有 for NT 和 for Unix 的产品。

* Check Plus HDL 原理图设计规则检查⼯具。

(NT & Unix)* SPECTRA Quest Engineer PCB 版图布局规划⼯具(NT & Unix)* Allegro Expert 专家级 PCB 版图编辑⼯具(NT & Unix)* SPECTRA Expert AutoRouter 专家级 pcb ⾃动布线⼯具* SigNoise 信噪分析⼯具* EMControl 电磁兼容性检查⼯具* Synplify FPGA / CPLD 综合⼯具* HDL Analyst HDL 分析器* Advanced Package Designer 先进的 MCM 设计⼯具于博⼠曾经说过:“Cadence ⾼速板设计中实际上的⼯业标准。

mentor2005安装说明

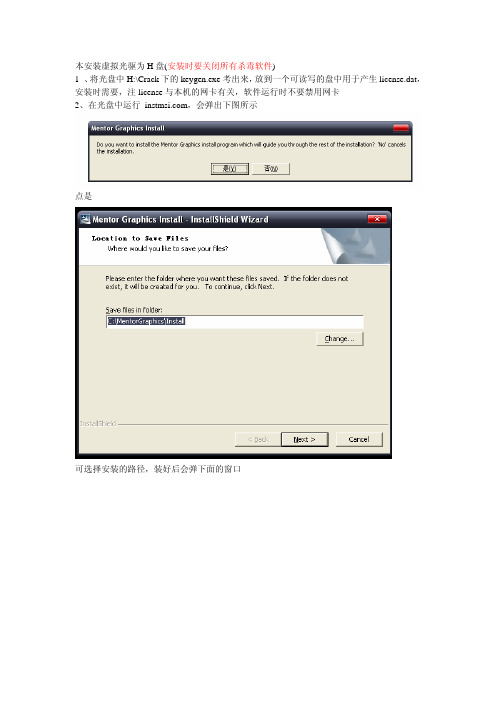

本安装虚拟光驱为H盘(安装时要关闭所有杀毒软件)1 、将光盘中H:\Crack下的keygen.exe考出来,放到一个可读写的盘中用于产生license.dat,安装时需要,注license与本机的网卡有关,软件运行时不要禁用网卡2、在光盘中运行_,会弹出下图所示点是可选择安装的路径,装好后会弹下面的窗口在先择Tools下拉的Set Targelist选择安装路径,完成后按Done。

回到最初安装面上面(Install Products)为安装,下面(Verify Installation)为检查点击Install Products会出现下面窗口点击Agree,会出现下面窗口上面路径为安装文件路径,下面路径为你要将软件到的安装文件路径下图为本次安装先好的窗口(软件在H盘中,安装到C盘中)。

然后点击下一步(Next),在Expedition Enterprise2005 spac1中可都选也可不选,一般选License Server下面的就可跟据自己情况选择,注若你选上级,你会看到全部打上勾,但有些会没打上,最好是一个一个查检,不要到时发现少功能。

选好后点下一步点安装(Install)最后只的耐心等待,直到出现如下窗口选择Licensing路径,可放D盘,一般与安装文件放一个目录下在上图中选择Typical好去找刚才产生的license.dat 然后点击下一步(Next)点击下一步(Next)注此路径放在你所安装软件盘中,只改盘符便可装完后会提示重起计算机,此时点同意,在开机时要关所有杀毒软件,否者会安装失败在出现下面图时就快完了在上图中选择Node-locked,然后点下一步找到最初产生的license.dat如下图不管只有点是会出现报错点OK就是了其间报错点OK点Donet,最后退出。

在上图中的WDIR文件一般放在安装文件目录下如下图点确定在下图中直接输入\WDIR然后点下一步点是创建文件最后完成最后软件会要求重起最后运行一下Mentor_Fix_V104.exe便可不然在新建原理图时会不正常下图为正常样式为然会在下图中现示些乱码。

MENTOR_WG2005中文翻译指导

MENTOR_WG2005中文翻译指导MENTOR WG 2005 使用入门BYonefinger软件模块说明:DxDesigner 原理图输入及集成管理环境DxDesigner是原理图设计输入的完整解决方案,包括设计创建、设计定义和设计复用。

提供强大的原理图输入功能,实现PCB网表的自动转换,支持LMS(Library Management System)库管理系统,DxDesigner支持层次化分页式模块化设计,方便实现设计复用缩短设计周期;集成的仿真和高速电路分析环境。

DxDesigner的主要特点包括:层次化设计输入管理以及设计复用提供原理图视图功能设计数据查询与交叉索引功能支持多属性编辑以及设计规则(包括物理规则和高速电气规则)传递集成的数字、模拟、数模混合仿真和高速电路分析环境集成的LMS库管理以及BOM清单生成集成的数据管理,支持团队设计,设计数据的检入、检出、锁定以及版本管理简单而便捷。

Library Manager 库管理工具Library Manager为开发和管理公司的设计库提供了一个中心位置,可确保设计库的一致性和集成性。

在Library Manager单一集成环境中,库管理员可创建、修改、维护原理图符号库、PCB封装库、焊盘库、IBIS库、以及包括板型在内的设计工艺库。

Library Manager 使管理员有能力对每一个终端、项目或预设计模板赋予相应的权限。

Library Manager有机结合了Mentor Graphics其它的设计工具如Expedition PCB。

在调用其他工具时,可启用Library Manager 相关工具模块。

同时,库管理员也可独立使用Library Manager以方便建库和维护。

Expedition PCB 设计及自动布线Expedition PCB为设计师提供了用于复杂PCB物理设计、分析和加工一整套可伸缩的工具,它将交互设计和自动布线有机地整合到一个设计环境中。

PCB工具软件介绍

PCB工具软件介绍早期的EDA企业有1000多家,后来发展到10家左右,其中Caden ce,Mentor,Zuken主要是高端产品,他们的软件要求在工作站上运行,操作系统都是UNIX,而且价格昂贵。

因为80年代就有EDA软件了,那个时候只有UNIX支持图形界面,并且工作站的性能要比PC机高出很多,所以一直延续至今,现在的大公司还是用工作站。

而Prote l,PowerPCB主要面向低端用户,对计算机的配置要求不高,一般在Windows下运行。

一般的PC机就可以很好的满足要求了。

随着,CPU和相关电脑硬件水平的不断提高,Cadence,Mentor,Zuken开始推出Windows下的产品,这方面Cadence走的比较快。

好像是2000年的样子吧,由于互连网泡沫的破裂,EDA产业进行了从新洗牌,上面的几家公司进行了重组!从市场占有率来说. Mentor公司现在最高,Cadence公司第二,Zuken 公司第三。

单个的PCB工具,Allegro在中国高端用户中软件占有率应该是最高的,其次PowerPCB,Protel 在中国大陆使用人比较多。

下面具体说说三间公司各自的特点。

Mentor公司的产品是BoardStation(EN)和ExpeditionPCB(WG)以及收购来的PADS(powerPCB)。

EN是传说中的PCB无敌高手,那些只考虑工期不考虑成本,总是做8层~12层PCB的通讯和军工研究所必杀绝技。

WG好像所有的bbs都同意这是地球上最好的布线工具。

PowerPCB就不说了,用的人也不少。

Mentor公司收购了PowerPCB后,继续两条腿走路,高端的还是原来的Mentor,现在最新版Me ntor EN2006;低端的产品还是PowerPCB,新名字叫PADS2005,最新的叫PADS2007,但是PADS2005SP2是一个比较稳定的版本。

还有德国一个小软件非常流行,是EAGLE,在欧美很有市场。

2005新增功能说明

2005/12/29增強表格式注解輸出(WT.ARX)功能說明:可設定表格式注解輸出的欄位操作說明:1. 進入WT對話方塊,選擇注解輸出按鈕,輸入F,彈出表格注解設定對話方塊(如圖)2. 點選規劃備料單按鈕,彈出設定檔(如圖)3.參照上圖設定,即可控制使用表格輸出時需輸出的欄位2005/11/4注解輸出時讀取板厚資料(WT.ARX)功能說明:可讀取圖元上的標籤資料操作說明:1. 進入WT雜項設定對話框,將[註解輸出時至圖元讀取板厚資料]選項開啟。

2005/10/6副程式檔名追加字串(WT.ARX)功能說明:可設定兩個以上副程式檔名操作說明:1. 進入WT雜項設定對話框,在副程式檔名追加字串一欄以“,”方式分別設定多個副程式檔名。

Ex: 程式檔名為Test.Nc , 欄位內字串設為{A,B,C} , 則第二個程式檔名為TestA.nc第三個程式檔名為TestB.nc第四個程式檔名為TestC.nc2005/10/2自動化加工切斷部分增加回起割點功能(WT.ARX)功能說明:使用自動化加工時,於切斷時會自動回起割點操作說明:1. 用記事開啟後處理檔2. 找到後處理檔中Variable 40描述欄位,將其初始值改為8,在生成自動化加工程式時在切斷部分會回起割點2005/9/2I、J值以相對座標方式(WT.ARX)功能說明:圓孔I、J值以相對座標方式輸出操作說明:1. 用記事開啟後處理檔2. 找到後處理檔中Variable 70 = 0.30-,abs,not_modal,init/0描述欄位,將其初始值改為12(init/12),如此程式當中的I、J值將以相對座標方式輸出2005/8/28DBF檔放電碼新規則設定(WT.ARX)功能說明:可分別設定多組放電代碼操作說明:1. 用記事開啟PDF檔2. 具體設定方式如下所示原資料01 02 11 12 21 22 23粗割粗割修一修一修二修二修三於DBF檔的第一行加標籤New-Dbf 則使用新規則01 02 11 12 21 22 2331 32 ……粗割粗割割1修1(割) 割1修1(修) 割1修2(割) 割1修2(修1) 割1修2(修2) 割1修3(割) 割1修3(修1) ..2005/8/16新增材質歸類功能(WT.ARX)功能說明:不同材質獲取加工資料庫中同種材質的加工資料操作說明:1. 用記事開啟Wir_mat.dat檔(亦可直接從雜項設定對話方塊開啟)2. 在需使用的材質名稱後作如下修改,如圖示亮顯處所示上圖中SLD即為新增材質,括弧中內容為選用此種材料時,對應於資料庫中的材料名稱3. 轉程式後,若在材質框中選取為SLD時,自動獲取加工資料庫中SKD11的加工資料2005/8/16新增修刀引線自動偏移功能(WT.ARX)功能說明:修刀切入點自動偏移操作說明:1. 用記事本開啟需使用的後處理檔2. 找到後處理檔中如下描述欄位V ariable 67=X0.30-,rel,modal,init/0.將其初始值更改為所需的偏移量(如init/0更改為init/0.3)3. 找到後處理中修刀引線進入描述段escape_in_feed="G01",(@47>0)?(@X=@67,@Y=@68);,@X,@Y,(@27!=#27)?#27;$將其更改為:escape_in_feed="G01",(@47>0)?(@X=#67,@Y=#68);,@X,@Y,(@27!=#27)?#27;$4. 修改完成後保存,轉程式摹擬即可看到修刀進線位置,向加工路徑相反方向偏移了0.32005/8/16無屑切割路徑製作方式調整(WT.ARX)功能說明:製作無屑加工路徑操作說明:1. Wpcam中選用無屑切割,彈出設定介面如下[取消原來的銅線溶解量和精修預留量兩設定項]2. 生成無屑路徑後,最後一圈的距離,將由條件組中的補正值與每刀補正偏移量設定值一半之和來確定2005/8/16內外R角自動圓角功能調整(WT.ARX)功能說明:分別設定每刀加工路徑的不同圓角值操作說明:1. 用記事本開啟需使用的後處檔2. 在後處理檔任何位置添加TRIM_FILLET=ON描述欄位3. Wpcam介面中整體條件項將增加如圖所示項目(圖1)4. 點擊修刀圓角設定按鈕彈出如下對話方塊在此設定框中可分別設定程式中每刀不同的圓角半徑值5. 轉程式後,每刀生成不同半徑值的R角,路徑最後一刀圓角的R值將抓取圖1處內外圓角設定值2005/7/19新增線割路徑置換標籤功能(WT.ARX)功能說明:能自動將已轉成路徑而具有相同加工條件的圖元一次性全部選取到,並賦予新的加工條件操作說明:於WPCAM裏圖元選取時,增加C:置換標籤選項,如下:"\n路徑專用- S:設定/A:自動/M:手動/T:切換型態/P:轉程式/3:上下異形/D:其他細節/O:秩序/C:置換標籤/K:同直徑選取<單孔>請選路徑>:"1. 進入Wpcam設定介面,選擇所需的加工孔類型2. 點選圖元按鈕進入命令行提示,輸入C,選擇需置換的路徑(只需選取其中一個)3. 程式自動將同種加工條件的加工路徑於拾取狀態,確定即可完成條件置換,置換後的路徑採用新的孔名稱,條件設定等各項參數設定.2005/7/17增強內外脫凹槽功能(WT.ARX)功能說明:配合CS2指令於圖元上做中斷點,所產生的NC檔其補償值代號左右相差40操作說明:1. 進入Wpcam介面,選取一般加工孔類型制作圖元的程式路徑2. 使用CS2指令,進入內外脫凹槽設定對話方塊,如圖,設定好參數選取對應的路徑段。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

的限制,提供给设计师最大的设计空间。Expedition PCB 的核心-获业界大奖的 Auto Active 自动布线器是基于形状的无网格布线器,布线速度极快,布线的可加工性首屈一指。它实现 真正的 45 度布线,并完全支持当今各种复杂封装如 BGA、CSP、COB 和微过孔、埋孔、盲孔 等加工工艺。其器件放置推挤后自动线调整,大面积覆铜处理方法皆独一无二。

了中心库。

3.3 同样的方法将SOIC cell partition加入中心库。

4、创建一个Part Partition。 右键点击Parts节点,从弹出菜单中选择New Partition,显示New Part Partition 对话框,键入Logic_Gates点击OK, Logic_Gates part partition就加入了中心库。 如下图所示:

3.1 选择 Setup > Partition Editor 或 点击图标 ,显示Partition Editor 对话框如图3,点击 ,键入Logic_Gates后点击Apply。

图3 3.2 右键点击Cells节点,从弹出菜单中选择New Partition,显示New Cell

Partition 对话框,键入Dip_Thru,点击OK, Dip_Thru cell partition就加入

时延驱动的层次化区域规则保证器件布局满足信号完整性和时延及生产规则,信号完整 性优化使设计者能找到满足信号完整性要求的终端策略;而拓扑、延时、信号完整性等规则 驱动着综合过程。所谓的综合是布出满足所定义电气规则的网线,信号完整性分析则支持交 互式探查和系统严整两种方式。在已有的一些 EDA 工具中,该工具支持双面接口。

MENTOR WG 2005 使用入门

BY onefinger

软件模块说明:

DxDesigner 原理图输入及集成管理环境

DxDesigner 是原理图设计输入的完整解决方案,包括设计创建、设计定义和设计复用。 提供强大的原理图输入功能,实现 PCB 网表的自动转换,支持 LMS(Library Management System)库管理系统, DxDesigner 支持层次化分页式模块化设计,方便实现设计复用缩短 设计周期;集成的仿真和高速电路分析环境。DxDesigner 的主要特点包括:

Library Manager 库管理工具

Library Manager 为开发和管理公司的设计库提供了一个中心位置,可确保设计库的一 致性和集成性。在 Library Manager 单一集成环境中,库管理员可创建、修改、维护原理图 符号库、PCB 封装库、焊盘库、IBIS 库、以及包括板型在内的设计工艺库。Library Manager 使管理员有能力对每一个终端、项目或预设计模Graphics 其它的设计工具如 Expedition PCB。在调用其他工具时,可启用 Library Manager 相关工具模块。同时,库管理员也可独立使用 Library Manager 以方便建 库和维护。

层次化设计输入管理以及设计复用 提供原理图视图功能 设计数据查询与交叉索引功能 支持多属性编辑以及设计规则(包括物理规则和高速电气规则)传递 集成的数字、模拟、数模混合仿真和高速电路分析环境 集成的 LMS 库管理以及 BOM 清单生成 集成的数据管理,支持团队设计,设计数据的检入、检出、锁定以及版本管理简单 而便捷。

IS_Synthesizer 基于电气规则驱动的互连综合工具

IS_Synthesizer 能帮助设计者以自动或交互式的方式实现没有电气错误的高速电路板 设计。IS_Synthesizer 将自动、交互智能布线器及与之相对应的分析机制结合起来,在电 气规则驱动下,布出满足所定义电气规则的高速连线,保证所有的连线满足电气和生产要求。 系统所分析和比较的是电气规则,如延时等而非线长和平行线等物理限制。IS_Synthesizer 支持真正的无网格结构、实时自动 45 度布线。其特点有:用对称配对拓扑技术,自动综合 出差分对线,以确保最小时延偏差和共模噪声;支持育孔、埋孔、错孔、螺旋孔等 HDI 技术, 以及许多预先定义和定制的连线拓扑。对主要是高速连线的设计来说,IS_Synthesizer 一 次完成你的设计,使设计的周期为最短。

IBIS Standard Library模型解决方案

对于互连综合的模型解决方案 Mentor Graphics 提供了经过验证,确保高度精确的模型 库,ICX Standard Library™提供基于测试的高精度 IBIS 模型包括 ASIC 器件、微处理器、 ROM、RAM 器件、可编程器件和数字逻辑器件,每个模型包含了半导体厂商的数据和完整的 器件标号。

5、 输入Dxd Symbol到中心库

5.1 点击 Symbols,显示出Logic_Gates symbol partition。 5.2 右键点击Logic_Gates弹出菜单如下图所示

5.3 选择Import Symbols,浏览到Mentor Graphics\2005Exp\SDD_HOME \wg\tutorial\LibMgr, 选择 g244a.1和74f244_full.1 DxDesigner symbols 点击OPEN,显示如下图:

Tau板级时序分析 Tau 是业界第一个板极时序验证工具,它专为验证复杂功能块之间的时序关系而开发,这些 功能块包括处理器,存储器和 ASIC 等高速数字器件。执行验证操作时不需要激励信号,也 不需要器件的完整功能模型,可以比全功能仿真更为快速地给出板级时序关系。Tau 既考虑 了芯片内部时延和时钟相位漂移,也考虑了板级时钟摇摆和连线时延。其仿真对象包括同步 电路,异步电路和时钟树。在原理图设计阶段,Tau 可以帮助确定器件速度类型 并 发现需 设置高速布线规则的关键网线,关键互联时延的松弛方程组可以用来驱动 Interconnect Synthesis 工具完成满足板级时序要求的物理布线。Tau 还可以接受高速分析工具生成的连 线时延数据并结合器件时序模型进行板级时序的后验证,以确保设计的时 序正确性,还可 以进一步确定电路板的工作速度极限。

IS_Floorplanner 基于电气规则驱动的布局及预分析工具

IS_Floorplanner 允许用户通过定义关键路径时延,信号质量,和物理规则等要求来进 行高速设计。这些物理设计要求和电气设计要求,通过 IS_Floorplanner 来即时监视和权衡。 IS_Floorplanner 的集成环境中有一个规则管理系统、时延驱动层次化区域规划器以及交互 式综合和信号完整性分析的能力。规则管理的电子表格界面使之易于输入和维护驱动设计过 程的规则。

2.2 点击 File > New创建一个中心库文件(.lmc),首先显示一个选择中心 库目录的对话框,如图1:

2.3 点击图标 。键入中心库的名字(如Company_Library),按 ENTER, 然后点击 OK. 显示出中心库的导航树,如图2

图1

图2 库管理模块创建的中心库目录包含以下子目录和文件 CellDBLibs – 包含所有cell (.cel)文件的目录。 Config -包含所有libpdf.cfg文件的目录,libpdf.cfg是Library PDF配置

文件。 IBISModels -包含所有IBIS Model (.ibs)文件的目录。 Layout -包含padstack文件PadstackDB.psk的目录。

LayoutTemplates -包含所有设计模板文件的目录。 LogFiles -包含与中心库相关的LOG文件的目录。 PartsDBLibs -包含所有part (.pdb)文件的目录。 pkt –与一个DxDesigner项目相关联的目录。 sch -与一个DxDesigner项目相关联的目录。 sym -与一个DxDesigner项目相关联的目录。 SymbolLibs -包含所有symbol文件的目录。 wir -与一个DxDesigner项目相关联的目录。 Work – 一个空的目录。 CentLib.prp文件 – 一个包含symbol特性信息的文件。 <central_library_name>.dbc 文件- DxDatabook 用户的配置文件 。 <central_library_name>.lmc 文件-创建的中心库。 <central_library_name>.dproj 文件- 专属中心库的项目文件 <central_library_name>.cfg – 记录中心库配置的文件。 sysindex.cbf – 一个与中心库相关联的文件。 viewdraw.ini – DxDesigner用到的配置文件 3、创建一个Symbol:

Quiet Expert 电磁兼容分析专家系统

Quiet Expert 是高性能的 EMI/EMC 分析设计工具,具有专家系统的功能,可提供多种 类型的电磁分析,并根据相关的条件计算出电磁辐射的频谱图。 Quiet Expert 内嵌 EMC 专家知识库,可以实现 PCB 板级设计 EMC 检查,报告设计中对 EMC 设计准则的违反,并且指出可能的解决方案;支持常见的建模方式,也可以简单地指定器件 管脚模型的相关参数迅速构建分析模型;可以检查单线的 EMI 辐射频谱,可以考察单线以及 整板的 EMI 辐射,也可以根据辐射方式来考察;支持磁通图、电路板图、频谱辐射、电容谐 振曲线、信号串扰等图形方式。

models, and layout templates; b、定义和管理partitions-一组Part; c、与PCB或其他库中输入/输出 parts, cells, symbols, padstacks, and

IBIS models d、 建立和存储标准的PCB模板(板形、布线层、过孔,线距)

IS_Multiboard高速电路的多板设计工具 对于包含多板和连接器,电缆或多封装模块的高速数字系统的设计 IS_Multiboard 提供完整的解决方案。IS_Multiboard 的主要目的是考究跨越多 板系统的互连网络,将信号完整性扩展到系统级。该工具能分析不同模块之间的 关键信号,其易于使用的界面帮助用户定义电路板、回板和 MCM 的系统结构。例 如,只需将电路板拖放到连接器上,电路板就被装配上了。为了给出最精确的结 果,信号分析包含了连接器插座、电缆插座。系统级连线的信号完整性分析能保 证整个系统的信号完整性。IS_Multiboard 同时也支持将电路板简化成 EBD 模型, 将一个系统简化成一个板来做简单的分析。