脉宽调制PWM的VHDL实现

基于VHDL的SVPWM发生器的实现

模 块 、 WM 波输 出模块 、 P 同步 脉 冲模 块 , 下面将 分 别

进 行详 细的说 明 。 前 面介 绍 了 S P V WM 的 基 本 原 理 , 用 V L 采 HD

计 而不必 改动硬 件 电路 。使 用 F G P A来 开发 数字 电 路 , 以大大缩 短设计 时 间 , 少 P B面积 , 可 减 C 提高 系

统 的可靠 性 。

了广 泛应 用 。但 使 用 D P单 核 心 的控 制 方 法 存 在 S

一

些 缺陷 : 的硬 件 已完 全 固化 , 开 发 利 用 的 功 它 可

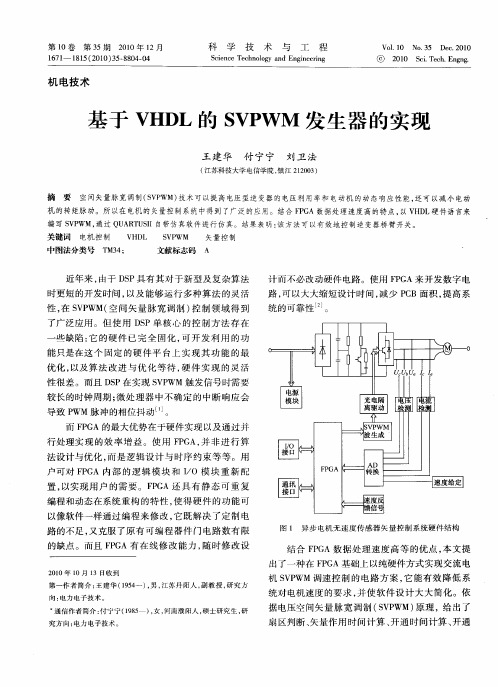

种 基于 F G 的无 速 度 传 感 器 矢 量 控 制 系 统 的 PA

目的 。

3 SP V WM 模块设计及其仿真结果

SP V WM模 块是 整个 设 计 的难 点 与 重 点 , 这 在

里 主要分 为作 用时 间 及输 出状 态 模块 、 间过 调 制 时

1 无速度传感器矢量控制 系统硬件结构

机的转矩脉 动。所 以在 电机 的矢量控制系统中得到 了广泛的应用。结合 F G P A数据处理速度高的特 点, V D 以 H L硬件语言来

编写 S P V WM, 过 Q A T SI自带 仿 真 软 件进 行 仿 真 。结 果 表 明 : 方 法 可 以有 效 地 控 制 逆 变 器桥 臂 开 关 。 通 U R UI 该

⑥

2 1 S i eh E gg 0 0 c T c. nn. .

机 电技 术

基 于 V L的 S P HD V WM 发 生 器 的实 现

基于vhdl的正负脉宽数控调制信号发生器的设计

基于VHDL的正负脉宽数控调制信号发生器的设计1. 引言正负脉宽数控调制信号发生器是一种常用的电子设备,用于产生特定频率和幅度的调制信号。

在很多应用中,如通信系统、音频处理等领域都需要使用到这种信号发生器。

本文将介绍基于VHDL语言实现正负脉宽数控调制信号发生器的设计。

2. 设计目标设计一个能够产生正负脉宽数控调制信号的电路,具体要求如下: - 支持设置输出频率范围; - 支持设置输出幅度范围; - 支持设置占空比范围; - 输出波形应为可调节幅度和频率的方波。

3. 设计思路基于VHDL语言实现正负脉宽数控调制信号发生器需要以下步骤: 1. 定义输入和输出接口; 2. 设计主模块,包括时钟分频模块、方波生成模块、幅度和频率控制模块; 3. 实现各个模块,并进行仿真验证; 4. 进行综合和布局布线操作; 5. 下载到目标设备进行测试。

4. 设计细节4.1 输入和输出接口正负脉宽数控调制信号发生器的输入和输出接口如下: - 输入接口: - 频率设置:用于设置输出频率范围; - 幅度设置:用于设置输出幅度范围; - 占空比设置:用于设置占空比范围。

- 输出接口: - 正负脉冲信号:产生正负脉宽数控调制信号。

4.2 主模块设计主模块是整个电路的核心,包括时钟分频模块、方波生成模块和幅度和频率控制模块。

4.2.1 时钟分频模块时钟分频模块用于产生时钟信号,通过对输入的时钟信号进行分频来实现不同的输出频率。

可以使用计数器来实现分频功能,具体步骤如下: 1. 接收输入的时钟信号; 2. 设置计数器初始值为0; 3. 每次接收到时钟信号后,计数器值加1; 4. 当计数器值达到设定值时,产生一个输出脉冲,并将计数器重置为0。

4.2.2 方波生成模块方波生成模块根据输入的时钟信号和占空比设置产生正负脉宽数控调制信号。

具体步骤如下: 1. 接收时钟信号和占空比设置; 2. 根据占空比设置,将时钟信号分为高电平和低电平两个阶段; 3. 在高电平阶段输出高电平信号,在低电平阶段输出低电平信号。

使用VHDL设计基于CPLDFPGA逆变电源的PWM波形

筘23卷第6期焊接学报v。

I.23N。

.620O2年l2月TRANSACTl0NSOFTHECHINAWELDINCINSr兀TUTIONDecember20O2使用VHDL设计基于CPLD/FPGA逆变电源的PWM波形刘松,熊腊森,余爱民(华中科技大学,武汉430074)摘要:介绍了使用VHDL设计基于cPLD/FPcA逆变电源PwM驱动波形的优点,并详细地探讨了PwM波形的设计原理,提出了三种程序设计的方案,并给出了实时性最好的基于ROM结构的PwM波形的VHDL程序。

设计的程序经过AcⅡve一ⅦDL仿真器仿真。

结果表明:使用VHDL设计PwM波形.控制精度高,可以通过改变cPL工旷FP.cA外接的晶振的频率来提高占空比的漏节精度,而且,控制方式灵活,能够调整功率开关管的死区时间,保护开关管安全工作,易于实现数字化的PI、PID词节。

关键词:非常高速集成电路硬件描述语言;弥冲宽度词制;逆变电源;仿真中围分类号:咄33文献标识码:^文章编号:0253—360x(2002)06—89—03O序言目前,逆变电源常常使用专用的芯片如TL494、sG3525等来产生PwM(脉冲宽度调制)波形,并由其通过反馈信号来实现对PwM波形的宽度的调节,从而获得稳定的输出。

当控制电路设计完成后,就是一个相对独立的系统,诃节、控制方式不能再更改,系统的总体协调功能差。

近几年,基于微机控制的逆变系统主要采用单片机或DsP(数字信号处理器)控制。

采用单片机的系统若使用定时器产生PwM.由于中断的特点,使输出的PwM的脉宽容易发生改变,从而影响输出电压的精度。

如Mcs5l系列,中断响应为3—8个机器周期,用6MHz的晶振,机器周期为2斗s,逆变器工作频率为20kHz,工作周期50斗s,则误差范围为12%一32%;此外.单片机对系统调节的实时性差(96系列的机型也不能满足要求),因此单片机构成的系统一般需要外接产生PwM的芯片,单片机主要用于协词系统的工作及输出显示。

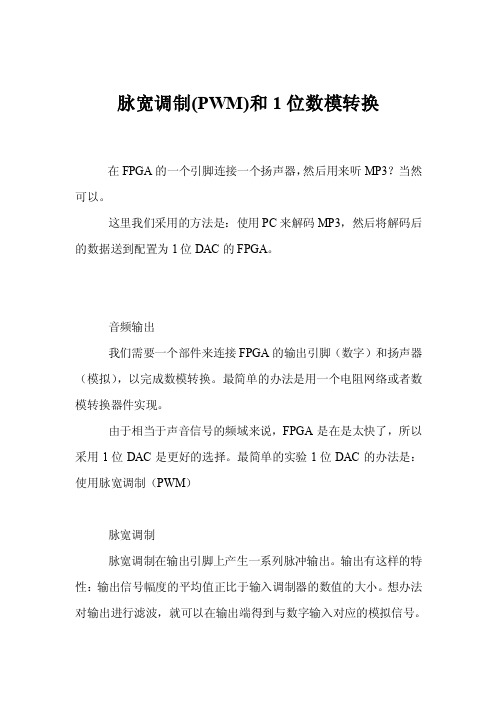

脉宽调制(PWM)和1位数模转换

脉宽调制(PWM)和1位数模转换在FPGA的一个引脚连接一个扬声器,然后用来听MP3?当然可以。

这里我们采用的方法是:使用PC来解码MP3,然后将解码后的数据送到配置为1位DAC的FPGA。

音频输出我们需要一个部件来连接FPGA的输出引脚(数字)和扬声器(模拟),以完成数模转换。

最简单的办法是用一个电阻网络或者数模转换器件实现。

由于相当于声音信号的频域来说,FPGA是在是太快了,所以采用1位DAC是更好的选择。

最简单的实验1位DAC的办法是:使用脉宽调制(PWM)脉宽调制脉宽调制在输出引脚上产生一系列脉冲输出。

输出有这样的特性:输出信号幅度的平均值正比于输入调制器的数值的大小。

想办法对输出进行滤波,就可以在输出端得到与数字输入对应的模拟信号。

脉宽调制器的输入可以是任意宽度,通常是8位或16位其输出则是1位的(一个输出)脉宽调制也广泛的应用于微控制器,详见应用笔记AN665.累加器生成脉宽调制信号的最简单的办法就是使用硬件累加器。

一旦累加结果溢出,就输出1(高电平),否则输出0(低电平)。

这在FPGA中很容易实现。

V erilog 代码:module PWM(clk, PWM_in, PWM_out);input clk;input [7:0] PWM_in;output PWM_out;reg [8:0] PWM_accumulator;always @(posedge clk) PWM_accumulator <= PWM_accumulator[7:0] PWM_in;assign PWM_out = PWM_accumulator[8];endmoduleVHDL 代码:library IEEE;use _LOGIC_;use _LOGIC_;entity PWM isport (clk : in std_logic;PWM_in : in std_logic_vector (7 downto 0) := “00000000”;PWM_out : out std_logic);end PWM;architecture PWM_arch of PWM issignal PWM_Accumulator : std_logic_vector(8 downto 0);beginprocess(clk, PWM_in)beginif rising_edge(clk) thenPWM_Accumulator <= (“0” & PWM_Accumulator(7 downto 0)) (“0” & PWM_in);end if;end process;PWM_out <= PWM_Accumulator(8);end PWM_arch;输入数据越大,累加器越快溢出,从而使得输出1的频率越高,这正是我们希望的。

VHDL语言PWM风扇等精度测速装置的实现

VHDL语言PWM风扇等精度测速装置的实现李贵子;王季【摘要】According to the requirements of high precision and intelligentialize in the process of PWM fan performanceevaluation,complex programmable logic device CPLD of VHDL language was used to develop an equal-precision and self adaptive measurement system to measure the speed of small fan.The system use VHDL language to program,select Quartus Ⅱ as the development platform with solution for hardware and software of the system.The simulation and experiment show the measurement of system is reliable and the measurement precision,sensitivity and resolution ratio are excellent.Therefore the system is convenient for field test.%针对PWM风扇性能评价中对高精度、智能化的要求,利用VHDL语言的复杂系统可编程逻辑器件CPLD,开发一种等精度自适应小型风扇转速测量系统.该系统采用VHDL语言编写程序,选用Quartus Ⅱ作为开发平台,并给出系统的软硬件方案.通过仿真试验表明:系统测量工作可靠,有良好的测量精度、灵敏度、分辨率,便于现场测试.【期刊名称】《中国测试》【年(卷),期】2013(039)004【总页数】4页(P109-112)【关键词】VHDL语言;PWM风扇;等精度测速【作者】李贵子;王季【作者单位】甘肃省机械产品检测与技术评价重点实验室,甘肃兰州730030;甘肃省机械科学研究院,甘肃兰州730030;甘肃省机械产品检测与技术评价重点实验室,甘肃兰州730030;甘肃省机械科学研究院,甘肃兰州730030【正文语种】中文【中图分类】TM925.11;TM930.114;TP274+.2;TP302.7随着电子、机械装置可靠性水平的提升,PWM控制小型直流散热风扇(以下简称风扇)在加速发展。

直流电机PWM控制的FPGA实现

. . .人文科技学院课程设计报告课程名称:VHDL语言与EDA课程设计设计题目:直流电机调速控制器系别:通信与控制工程系专业:电子信息工程班级: 2008级电信1班学生: 湘宇晨旭学号: 08409107 08409101起止日期:2011年06月15日~ 11年 06月24日指导教师:田汉平教研室主任:侯海良摘要文章详细地介绍了直流电机的类型、结构、工作原理、PWM调速原理以与FPGA 集成芯片。

并对直流电机PWM调速系统方案的组成、硬件电路设计、程序设计与系统仿真分别进行了详细的叙述。

拟开发的直流电机PWM调速装置具有调速围宽、低功耗、可实现在线调试等特点。

本系统是以FPGA为其控制核心,输入电路以键盘作为输入方式向FPGA控制系统发出控制命令,以有源晶振构成的时钟电路发出信号。

控制系统接收命令后直接向H型桥式驱动电路发出PWM控制信号。

输出电路主要实现正反转、起停控制、速度在线可调功能。

本设计已通过了实验仿真。

关键词:直流电机;PWM;FPGA;有源晶振目录设计要求11、方案论证与对比11.1方案一11.2方案二22、设计原理与其实现过程32.1设计总原理32.2设计总原理图42.3模块设计和相应模块程序52.3.1 PWM脉冲调制信号电路模块52.3.2 二进制计数器电路模块62.3.3 数字比较器模块72.3.4 细分计数器电路模块72.3.5 逻辑控制模块92.4 电路的总仿真图102.4.1正/反转控制仿真102.4.2 启/停控制仿真112.4.3 加/减速仿真112.4.4 仿真结果分析123、课程设计结论与心得体会134、仪器仪表清单145、参考文献146、致14附录电路完整程序程序14直流电机调速控制器设计设计要求设计一个直流电机PWM调速控制器,并能进行正反转控制;1、方案论证与对比1.1方案一基于单片机的直流电机PWM调速方案AT89C51图 1 基于单片机控制的PWM调速系统如图1所示为基于单片机的直流电机PWM调速方案的系统方框图。

脉宽调制PWM的VHDL实现

COMPONENT lpm_compare

GENERIC (

lpm_representation

: STRING;

lpm_type

: STRING;

lpm_width

: NATURAL

4/6

); PORT (

dataa : IN STD_LOGIC_VECTOR (7 DOWNTO 0); datab : IN STD_LOGIC_VECTOR (7 DOWNTO 0); AgB : OUT STD_LOGIC ); END COMPONENT;

pwm_output : out std_logic ); end PWM;

architecture behav of PWM is

signal Triangle_data : std_logic_vector( 7 downto 0 ); 5/6

signal pwm_data : std_logic;

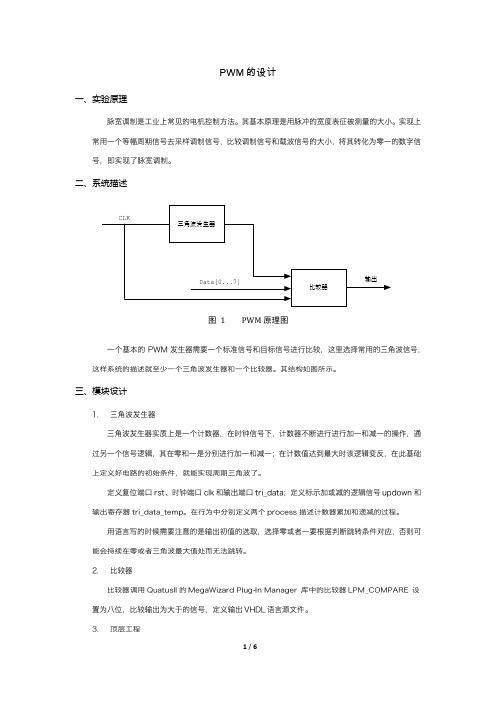

一、实验原理

PWM 的设计

二、系统描述

CLK

三角波发生器

Data[0...7]

输出 比较器

图 1 PWM 原理图

三、模块设计

1/6

四、实验结果

五、问题与展望

图 2 PWM 仿真波形图

2/6

附源代码

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE ieee.std_logic_unsigned.all;

component Triangle is port( rst : in std_logic; clk : in std_logic; tri_data : out std_logic_vector ( 7 downto 0 ) );

基于VHDL的PWM信号发生器的设计论文

Yi bin University EDA技术及应用课程设计报告题目基于VHDL的PWM信号发生器系别物理与电子工程学院专业电子信息科学与技术学生姓名学号班级2013 年 12月 21日摘要本次课程设计是基于VHDL的PWM信号发生器,PWM信号发生器应用所学的数字电路和模拟电路的知识进行设计。

在设计过程中,所有电路仿真均基于Quartus II 9.1仿真软件。

本课程设计介绍了PWM 信号发生器的设计方案及其基本原理,并着重介绍了PWM信号发生器各单元电路的设计思路,原理及仿真,整体电路的的工作原理,控制器件的工作情况。

设计共有三大组成部分:一是原理电路的设计,本部分详细讲解了电路的理论实现,是关键部分;二是性能测试,这部分用于测试设计是否符合任务要求。

三是是对本次课程设计的总结。

关键词: PWM信号发生器仿真设计目录第1章绪论1.1 EDA 和QuartusⅡ的简介及起源 (1)1.2 EDA的优势及发展趋势 (1)第2章系统设计思路 (3)第3章可自加载加法计数器的设计 (4)第4章信号发生器设计过程 (6)第5章软件仿真5.1 Quartus Ⅱ软件简介 (8)5.2 用Quartus Ⅱ的仿真步骤和图像 (9)5.3 逻辑综合结果 (12)第6章设计总结 (13)第7章参考文献 (15)附录设计程序 (16)第1章绪论1.1 EDA和QuartusⅡ的简介及起源EDA是英文“electronic design automation”(电子自动化设计)的缩写,EDA技术是20世纪90年代迅速发展起来的,是现代电子设计的最新技术潮流,是综合现代电子技术和计算机技术的最新研究成果,是电子线路设计与分析的一门技术。

EDA包括电子线路的设计、计算机模拟仿真和电路分析及印制电路板的自动化设计三个方面的内容。

随着可编程逻辑器件迅速发展,出现了功能强大的全新的EDA工具。

具有较强描述能力的硬件描述语言(VHDL、Verilog、HDL)及高性能综合工具的使用,使过去单功能电子产品开发转向系统级电子产品开发。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3/6

process ( rst, clk ) begin

if rst = '0' then tri_data_temp <= B"00000001";

elsif clk'event and clk = '1' then case updown is when up => tri_data_temp <= tri_data_temp + 1; when down => tri_data_temp <= tri_data_temp - 1; when others => end case;

pwm_output <= pwm_data; end behav;

6/6

COMPONENT lpm_compare

GENERIC (

lpm_representation

: STRING;

lpm_type

: STRING;

lpm_width

: NATURAL

4/6

); PORT (

dataa : IN STD_LOGIC_VECTOR (7 DOWNTO 0); datab : IN STD_LOGIC_VECTOR (7 DOWNTO 0); AgB : OUT STD_LOGIC ); END COMPONENT;

end if; --tri_data <= tri_data_temp; end process;

end behav;

LIBRARY ieee; USE ieee.std_logic_1164.all;

LIBRARY lpm; USE lpm.all;

ENTITY Compare IS

PORT

(

dataa

一、实验原理

PWM 的设计

二、系统描述

CLK

三角波发生器

Data[0...7]

输出 比较器

图 1 PWM 原理图

三、模块设计

ቤተ መጻሕፍቲ ባይዱ

1/6

四、实验结果

五、问题与展望

图 2 PWM 仿真波形图

2/6

附源代码

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE ieee.std_logic_unsigned.all;

: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

datab

: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

AgB

: OUT STD_LOGIC

);

END Compare;

ARCHITECTURE SYN OF compare IS

SIGNAL sub_wire0 : STD_LOGIC ;

component Triangle is port( rst : in std_logic; clk : in std_logic; tri_data : out std_logic_vector ( 7 downto 0 ) );

end component;

component Compare is port( dataa : in std_logic_vector( 7 downto 0 ); datab : in std_logic_vector( 7 downto 0 ); AgB : out std_logic );

pwm_output : out std_logic ); end PWM;

architecture behav of PWM is

signal Triangle_data : std_logic_vector( 7 downto 0 ); 5/6

signal pwm_data : std_logic;

BEGIN AgB

<= sub_wire0;

lpm_compare_component : lpm_compare GENERIC MAP (

lpm_representation => "UNSIGNED", lpm_type => "LPM_COMPARE", lpm_width => 8 ) PORT MAP ( dataa => dataa, datab => datab, AgB => sub_wire0 );

begin

process( rst, clk ) begin

if rst = '0' then updown <= up;

elsif clk'event and clk = '1' then case updown is when up => if tri_data_temp >= B"11111110" then updown <= down; end if; when down => if tri_data_temp <= B"00000001" then updown <= up; end if; when others => end case;

ENTITY Triangle IS

port(

rst

: in std_logic;

clk

: in std_logic;

tri_data: out std_logic_vector( 7 downto 0 )

);

end Triangle;

architecture behav of Triangle is

constant up : std_logic := '0'; --* rising slope *-constant down : std_logic := '1'; --* descending slope *-signal updown : std_logic; signal tri_data_temp : std_logic_vector(7 downto 0);

END SYN;

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE ieee.std_logic_unsigned.all;

entity PWM is port( clk : in std_logic; rst : in std_logic; ADC_data : in std_logic_vector ( 7 downto 0 ); --Triangle_data : in std_logic_vector ( 7 downto 0 );

end component;

begin

Triangel_inst : Triangle port map( rst => rst, clk => clk, tri_data => Triangle_data );

Compare_inst : Compare port map( dataa => ADC_data, datab => Triangle_data, AgB => pwm_data );