2009-2010春季数字电子技术基础B卷答案

【精品】数字电子技术基础试卷及答案8套(可编辑

数字电子技术基础试卷及答案8套------------------------------------------作者------------------------------------------日期数字电子技术基础1一.1.(15分)试根据图示输入信号波形分别画出各电路相应的输出信号波形L1、L2、L3、L4、和L5。

设各触发器初态为“0”。

AB二.(15分)已知由八选一数据选择器组成的逻辑电路如下所示。

试按步骤分析该电路在M1、M2取不同值时(M1、M2取值情况如下表所示)输出F的逻辑表达式。

八选一数据选择器输出端逻辑表达式为:Y=Σm i D i,其中m i是S2S1S0最小项。

23FM 2 M 1 F0 01 1101三.(8分)试按步骤设计一个组合逻辑电路,实现语句“A>B ”,A 、B 均为两位二进制数,即A (A 1、A 0),B (B 1、B 0)。

要求用三个3输入端与门和一个或门实现。

四.(12分)试按步骤用74LS138和门电路产生如下多输出逻辑函数。

123Y ACY ABC ABC BC Y BC ABC=⎧⎪=++⎨⎪=+⎩ 74LS138逻辑表达式和逻辑符号如下所示。

五.(15分)已知同步计数器的时序波形如下图所示。

试用维持-阻塞型D 触发器实现该计数器。

要求按步骤设计。

六.(18分)按步骤完成下列两题1.分析图5-1所示电路的逻辑功能:写出驱动方程,列出状态转换表,画出完全状态转换图和时序波形,说明电路能否自启动。

2.分析图5-2所示的计数器在M=0和M=1时各为几进制计数器,并画出状态转换图。

图5-1图5-2七.45八.(10分) 电路下如图所示,按要求完成下列问题。

1.指出虚线框T1中所示电路名称.2.对应画出V C 、V 01、A 、B 、C 的波形。

并计算出V 01波形的周期T=?。

157 6 8 42 R 1NE5553R 2C1Vc+0.01uJK 1QQ&&V CCV 01ABCC 10K10KT 1T 267数字电子技术基础2一.(20分)电路如图所示,晶体管的β=100,Vbe=0.7v 。

数字电子技术参考答案

数字电子技术试卷(1)参考答案一.填空1. 1111011,7B2. 8613. 与,或,非 4. 0,1,高阻5. 真值表,逻辑图,逻辑表达式,卡诺图,波形图(时序图) 6. 波形的整形 7. 20伏8. 并行A/D ,串并行A/D ,逐次比较A/D ,双积分A/D (写出三种) 二.判断题1.× 2.√ 3.× 4.√ 5.√三.化简逻辑函数1.D B A Y +=-2.--+=D B A Y四.C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.AQ Q Qn +=-+1,A Q n =+1六.采用D 触发器,-=122Q Q D ,--=231Q Q D ,1230Q Q Q D -+=电路图略。

将非工作状态101,110,111带入方程得次态,101→001,110→101→001, 111→001,电路可以自启动。

七.f =65Hz数字电子技术(2)参考答案 一.填空题(16)1. 100011.110,23.C 2. 0,13. 当前输入,原状态4. 0,1,高阻;任何时候,只能有1个三态门被选通。

5. 有两个稳态,在触发信号作用下状态可相互转变,有记忆功能 6. 延时 7. 5.5v 8. 13二.判断题(10)1.√ 2.× 3.×4.√ 5.√三.化简题(14)1. B Y =2. -++=D A C B Y 四.(15)CD A B A Y --+= 五.(15)--+=B A Qn 11, Q B Q A Qn ---++=21六.(15)驱动方程:1,121=⊕=-K Q X J ,1,212=⊕=K Q X J逻辑功能:X=0时,同步三进制计数器;X =1时,同步三进制减法计数器。

该电路为同步三进制可逆计数器,并且能自启动。

七.(15)数字电子答案3 一.填空题(16)1. 1010110,100001102. 7 3. 16,64. 状态转换表,状态转换图,特性方程5. 06. 256×4bit 7. 5.275伏8. 转换精度,转换速度二.回答问题(10)1. 不正确。

2套 《数字电子技术》期末考卷+答案

第 1 页 共 12 页铜 陵 学 院2007-2008学年第二学期《数字电子技术基础》考试试卷(A 卷)(适用班级:06自动化本科)一、填空题(每空1分,共20分)1、数字信号是指在 和 上都不连续的信号。

2、二进制数11011转换为十进制数为 ,转换为十六进制数为 。

3、根据逻辑代数的运算规则有:A ·A = ,A ·A = 。

4、用4位二进制数表示一位十进制数,称为二-十进制代码,简称 码,最常用的二-十进制代码是 码。

5、按计数器中数值的增减分类,把计数器分为 、和可逆计数器。

6、计数器中,_____________计数器工作速度较快,_____________计数器电路结构简单。

7、一个容量为256×4位的RAM ,应有 个基本存储单元,每次访问 个基本存储单元,有 条数据线和 条地址线。

8、PROM 不可编程的逻辑阵列是 ,可编程的逻辑阵列是 。

9、逻辑代数中,最基本的三种逻辑运算是 运算、 运算和 运算。

二、判断题(第小题2分,共12分)1、真值表、逻辑代数式和逻辑电路图是同一逻辑功能的三种不同表达方式,只要知道其中一种,便可推出其它两种。

( )2、一个逻辑函数的所有最小项之积为1。

( )3、当用数码表示不同的事物时,这些数码已没有数量大小的含义。

( )4、TTL 门电路能带同类门的个数称为噪声容限。

( )5、计数器不仅能对时钟脉冲进行计数,还可以用于定时、分频、产生节拍脉冲等。

( ) 6、已知二输入端的TTL 与非门,将其中的一端经Ω100电阻接地,则当电源接通时,其输出端的状态为0。

( ) 三、选择题(每小题3分,共18分)1、若逻辑表达式F=C B A +·,则下列表达式中与F 功能相同的是( ) ①A B +C ②A B C ③AB C ④AB +C 2、函数F= AB+A C 的“或非-或非”表达式是( )①B A B A +++ ②(AB+A )·(AB+C ) ③C A B A + ④(A +B) ·(A+C) 3、一组合逻辑电路如用两级或非门实现,则其逻辑函数表达式应写成( )。

《数字电子技术基础》课后习题及参考答案

【题

(1)

解:(1)25=(0010 0101)BCD

(

(

(

【题

解:4位数格雷码;

0000、0001、0011、0010、0110、0111、0101、0100、1100、1101、1111、1010、1011、1001、1000、

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

此电路是三人表决电路,只要有两个人输入1,输出就是1。

A

B

C

D

Y2

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

0

0

1

0

0

0

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

0

1

1

1

1

《数字电子技术基础》课后习题及参考答案

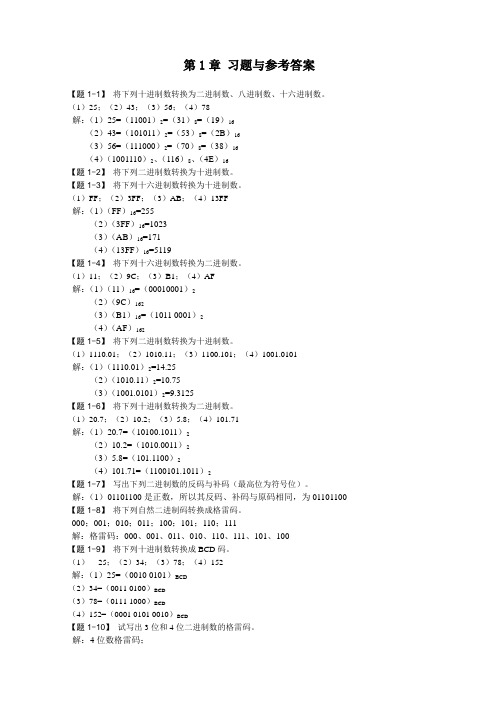

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

000;001;010;011;100;101;110;111解:格雷码:000、001、011、010、110、111、101、100【题1-9】将下列十进制数转换成BCD码。

数字电子技术基础题库及答案

试题库及答案试卷一一.基本概念题(一)填空题(共19分,每空1分)1.按逻辑功能的不同特点,数字电路可分为和两大类。

2.在逻辑电路中,三极管通常工作在和状态。

3.(406)10=()8421BCD4.一位数值比较器的逻辑功能是对输入的数据进行比较,它有、、三个输出端。

5.TTL集成JK触发器正常工作时,其d R和d S端应接电平。

6.单稳态触发器有两个工作状态和,其中是暂时的。

7.一般ADC的转换过程由、、和4个步骤来完成。

8.存储器的存储容量是指。

某一存储器的地址线为A14~A0,数据线为D3~D0,其存储容量是。

(二)判断题(共16分,每题2分)1.TTL或非门多余输入端可以接高电平。

()2.寄存器属于组合逻辑电路。

()3.555定时器可以构成多谐振荡器、单稳态触发器、施密特触发器。

()4.石英晶体振荡器的振荡频率取决于石英晶体的固有频率。

( )5.PLA 的与阵列和或阵列均可编程。

( )6.八路数据分配器的地址输入(选择控制)端有8个。

( )7.关门电平U OFF 是允许的最大输入高电平。

( )8.最常见的单片集成DAC 属于倒T 型电阻网络DAC 。

( )(三) 选择题(共16分,每题2分)1.离散的,不连续的信号,称为( )。

A .模拟信号 B.数字信号2.组合逻辑电路通常由( )组合而成。

A .门电路 B.触发器 C.计数器3.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

A .111 B.010 C.000 D.1014.十六路数据选择器的地址输入(选择控制)端有( )个。

A .16 B.2 C.4 D.85.一位8421BCD 码译码器的数据输入线与译码输出线的组合是( )。

A .4:6 B.1:10 C.4:10 D.2:46.常用的数字万用表中的A/D 转换器是( )。

A .逐次逼近型ADC B.双积分ADC C.并联比较型ADC7.ROM 属于( )。

数字电子技术春季A卷答案

2、密封线左边请勿答题,密封线外不得有姓名及相关标记。

年级 :

线

封-

密-

学院:

-------------------------------------------------

得分

一、 填空题(每空 0.5 分,共 10 分)

1、逻辑等式 F = AC + BC + D 的对偶式是 F* = ABC + AD + CD ; 反演式是 F = ABC + AD + C D (均化成最简“与或”式)。

姓名 :

学号:

第1页共8页

PDF 文件使用 "pdfFactory Pro" 试用版本创建

6、设计模值为 61 的二进制计数器和十进制计数器分别需要 6 级和 8 级触

发器。一个五位二进制加法计数器,由 00000 状态开始,问经过 109 个输入脉冲后,

此计数器的状态为 1101 。

(D)7

8、在下列器件中,不属于时序逻辑电路的是 (B) 。

(A)移位寄存器

(B)数据选择器

(C)顺序脉冲发生器

(D)序列信号发生器

9、石英晶体多谐振荡器的输出脉冲频率取决于 (C) :

(A)电路 RC 参数大小

(B)组成振荡器的门电路的平均传输时间

(C)晶体的固有频率 f0

(D)晶体的固有频率 f0 和 RC 参数值

专业:

年级 :

得分

六、下图所示为一可变进制计数器。该计数器由 4 个 JK 触发器, 一个 3 线-8 线译码器 T330 和一个 4 选 1 数据选择器 T1153 组成( S

为片选端)。T330 输出表达式为 Y0 = E A2 A1 A0 ;L;Y7 = EA2 A1 A0 ,式中

数字电子技术基础习题答案(精编文档).doc

【最新整理,下载后即可编辑】数字电子技术基础答案第1章自测题 1.1填空题1. 100011.11 00110101.01110101 11110.01 1E.42. 43. n 24. 逻辑代数 卡诺图5.)(D C B A F )(D C B A F +='6.))((C B D C B A F7. 代数法 卡诺图8. 1 1.2判断题1. √2.√3. × 1.3选择题 1.B 2.C 3.C1.4 A F =1⊙B AB F 2 B A F +=3 1.51.6 C L =1.7 AB C B A BC Y 习题1.1 当000012 A A A ,7A 到3A 有1个不为0时,就可以被十进制8整除 1.2 (a)AC BC AB F ++=1 (b )B A AB F +=2(c)C B A S ⊕⊕= AC BC AB C 0 1.3略 1.4 (1))(B A D C F )(1))((1B A D C F ++=' (2))(B A B A F )(2))((2B A B A F ++='(3) E D C B A F 3 DE C AB F ='3 (4))()(4D A B A C E A F )())()((4D A C AB E A F +++='1.5 C B A F ⊕⊕=1.6 (1) B A C B C A L (2) D B C B D C A L (3) AD L (4) E ABCD L (5) 0 L 1.7 C B A BC A C AB ABC C B A L ),,(1.8(1) ABD D A C F 1 (2) BC AB AC F 2(3) C A B A B A F 3 (有多个答案) (4) C B D C AB C A CD F +++=4 (5) C B A ABD C B A D B A F 5 (6) 16 F 1.9 (1) AD D C B B A F 1 (2) B A AC F 2(3) D A D B C B F 3 (4) B C F 4 1.10 (1) C A B F 1 (2) B C F 2(3) D A B C F 3 (4) C B A D B D C F 4 1.11 C A B A D F1.12 (1) D B A D C A D C B F 1(多种答案) (2)C B BCD D C D B F 2(3) C B C A D C F 3 (4) A B F 4 (5) BD D B F 5(6) C B D A D C A F 6(多种答案) (7) C A D B F 7(多种答案)(8) BC D B F 8(多种答案) (9) B D C F 9 1.13 略第2章自测题 2.1 判断题1. √2. √3. ×4. √5. √6. √7. ×8. √9. × 10√ 2.2 选择题1.A B 2.C D 3.A 4.B 5.B 6.A B D 7.C 8.A C D 9.A C D 10.B 习题2.1解:ABC Y =1 2.2解:(a)mA234.0503.012=-=-=C CES CC BS R U V I βBS mA 1.0537.06I I B <=-=∴三极管处于放大状态,)V (711.05012=⨯⨯-=-=CB CC O R I V u β。

(完整word版)【数字电子技术基础】试题和答案

《数字电子技术基础》一、填空题(每空1分,共5分)1.十进制9用余3码表示为 1100 。

2. 逻辑函数Y=A (B+C ),其反函数Y =C B A +。

对偶函数Y ’= A + BC 。

3. OC 门在实际使用时必须在输出端外接 负载电阻和电源 。

4. 设计模值为30的计数器至少需要 5 级触发器。

二、选择题(每题2分,共10分)1. 逻辑函数的描述有多种,下面 B 描述是唯一的。

A.逻辑函数表达式B.卡诺图C.逻辑图D. 文字说明 2. 一只四输入与非门,使其输出为0的输入变量取值组合有 D 种。

A.15B.8C.7D.1 3. 可用来暂时存放数据的器件是 B 。

A.译码器B.寄存器C.全加器D.编码器 4. D 可用来自动产生矩形脉冲信号。

A.施密特触发器B.单稳态触发器C.T 触发器D. 多谐振荡器 5. 单稳态触发器的主要用途是 C 。

A.整形、延时、鉴幅B. 整形、鉴幅、定时C.延时、定时、整形D.延时、定时、存储三、化简题(每题5分、共10分)用卡诺图化简下列逻辑函数,要求用与或式。

⒈ D C A D C A C B A D C ABD ABC Y +++++= 解:D A D C A D C A C B A D C ABD ABC Y +=+++++=得分 评卷人 复查人得分 评卷人 复查人得分 评卷人 复查人⒉ ∑∑+=)15,14,13,12,11,10()9,8,7,6,5(d m Y解:BD BC A d m Y ++=+=∑∑)15,14,13,12,11,10()9,8,7,6,5(四、分析题(共30分)1.(本题10分)分析电路,要求给出最简的与或逻辑表达式。

解:⒈逐级写表达式并化简:(6分)C B A B A C B B A B A BC B A BC B A Y +=+⋅+=⋅⊕=+⊕=)()()(⒉列真值表:(2分)A B C Y 0 0 00 0 1 0 1 00 0 1得分 评卷人 复查人0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 1 1 0 0⒊逻辑功能:(2分)当C 为0时,输出Y 为两输入A 、B 异或,当C 为1时,输出Y 为A ·B 。

《数字电子技术实验》试卷及答案 (B卷)

数字电子技术实验试题(B卷)班级:学号:姓名:台号:成绩:说明:1 .本卷请在90分钟内完成,包括整理仪器、设备。

2 .实验数据、波形、结论和问题解答等请直接写在试卷上,否则无效。

一、判断题:请在你认为陈述正确的题目前圆括号内打“√”认为错误的打“×”(每题 1 分,共 10 分)1.() CMOS 电路比 TTL 电路功耗大。

2.()数字示波器TDS-2002垂直灵敏度设置过高时,峰峰值测量结果带“?”。

3.()寄存器、计数器都属于组合电路;编码器、译码器属于时序电路。

4.()单稳态触发器无需外加触发脉冲就能产生周期性脉冲信号。

5.() EPROM 存储器属于只读存储器,当掉电后其存储的信息不会消失。

6.()模拟示波器具有平均值采样功能7.()二进制计数器既可实现计数也可用于分频。

8. ()同步计数器的计数速度比异步计数器快。

9. ()数码管有共阳和共阴两种,选用要根据译码器的类型而定。

10. ()将几个 D 触发器进行串接,前一级触发器的输出与后一级触发器的输入连接起来,就构成了移位寄存器。

二、解答下列问题(共 20 分)1.简述扫描测试法测量TTL与非门V TH的步骤(7分)2.右下图电路具备什么功能?用于何处?S为单刀双掷开关,Q为电路输出端。

(6分)3.四位二进制同步计数器74LS161 “同步”的含义是指什么?计数器的连接如下图,当工作稳定后,请画出输出端QA 、QB 、QC 、QD 的波形。

三、实验设计(70分)用JK 触发器设计一个计数器输出4位2进制数Q4 Q3 Q2 Q1按以下规律变化:设计一控制电路,将计数器的输出作为输入,当Q4Q3Q1Q1为1001、1010时 输出Y 为0;其余六个状态输出Y 为1,要求器件数量最少。

1.计数器、控制电路完整地理论推导,画出实验电路原理图。

(25分)可用器材包括:四位二进制计数器74LS161一片,双 J-K 触发器74LS73两片、四2输入与非门74LS00两片;四2输入与非门CD4011一片、四2输入或非门74LS02一片、四2输入与门74LS08一片、四2输入或门74LS32一片、异或门74LS86一片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第 - 1 -页 共 5 页

北方民族大学试卷

课程代码: 01100980 课程: 数字电子技术基础(B 卷)答案

一、填空题(20分,每空2分)

1、 逻辑函数 (,,)()()Y A B C A C B C =++的最大项表达式为 (2,4,6)∏ ;F AC BC

=+的最小项表达式为 (1,3,5)∑ 。

2、 循环码有两个显著特点,其一是 相邻性 ,其二是 循环性 。

3、 按存取方式来分,半导体存储器可分为 ROM 和 RAM 。

4、 按照电路的输入与输出之间的关系,可将数字电路分为 组合逻辑电路 与 时序逻辑电路 。

5、 如图1所示,当0EN =时,Y 为Y AB =。

图1

6、 二级管门电路如图2所示,Y 的逻辑表达式为Y A B C =。

图2

二、单项选择题(20分,每题2分)

1、(A B)(A C )(B C )+++中的冗余项为( B )。

A )A

B + B ) A

C + C )B C +

D )无冗余项 2、逻辑式Y AB AC =+中存在 ( A )冒险。

A )0

B )1

C )0,1

D )无冒险 3、与D C B A 逻辑不相邻的项为( B )。

A )ABC D

B )ABCD

C )ABC

D D )ABC D 4、集成电路74LS00属于( B )。

A )标准TTL 电路

B )低功耗肖特基TTL 电路

C )高速TTL 电路

D )先进的低功耗肖特基TTL 电路

5、将1024×4位的RAM 扩展为8192×8位的RAM ,需用( D )片1024×4位的RAM 。

A )4 B )6 C )8 D )16

6、若输入变量A ,B 取值不同时,输出F=0,否则F =1,则其输出与输入的关系是( C )。

A )与或运算 B )异或运算 C )同或运算 D )与非运算

7、4096×8位的RAM ,其存储容量为( B )kbit 。

A )64

B )32

C )16

D )8

8、下列逻辑电路中,是时序逻辑电路的是( B )。

A )数值比较器

B )计数器

C )译码器

D )加法器 9、下列触发器中为电平触发的触发器为( D )。

A )T 型

B )JK 型

C )

D 型 D )RS 型 10、当1,0,1D D CP R S ===,钟控RS 触发器的1

1

,n n Q

Q

++的值为( A )。

A )1,0

B )0,1

C )1,1

D )0,0

三、判断题(10分,每题1分)

1、DAC 可以实现模拟量向数字量的转换。

( 错 )

第

- 2 -页 共 5 页

2、CMOS 电路多余不用的输入端不能悬空。

( 对 )

3、时序逻辑电路按输出信号的特点不同,可分为同步时序逻辑电路和异步时序逻辑电路。

( 错 )

4、一个64选1的数据选择器,其地址输入端有8个。

( 错 )

5、格雷码是一种无权码。

( 对 )

6、存储器位扩展增加的是地址端个数。

( 错 )

7、主从JK 触发器存在空翻现象。

( 错 )

8、PLA 是与阵列和或阵列都可编程的LDPLD 。

( 对 )

9、单稳态触发器由稳定状态到暂稳态的变化与外界触发脉冲有关。

( 对 ) 10、计数器也可以用来做分频器。

( 对 )

四、基础类型题(共30分)

1、 化简下列逻辑函数。

(1)Y AC ABC AC D CD =+++ (代数法化简) (5分) 解:

()()()Y AC ABC AC D C D A C BC C D C D A C B D C D AB A C D C D AB AC D C D AB A C D A C D

=+++=+++=+++=+++=++=++=+

(2)F (A,B,C,D )=Σm(0,1,2,5,6,7,8,9,10,13,14) (卡诺图法化简) (5分)

[评分标准:正确画出卡诺图加2分,画出正确的包围圈加2分,正确结果得1分] 解: F=B D CD ABC BCD +++

(8分)

0。

[评分标准:逻辑表达式3分,真值表3分,波形图2分]

解:J 2=n Q A 2+ , K 2=B

1

2

+n Q =y n n Q B Q Q A 222+∙+=n

2n 2

Q B Q A +∙ 真值表:

第 - 3 -页 共 5 页

3、用八选一的数据选择器74151实现逻辑函数F (A,B,C )=AC AC +。

(6分)

[评分标准:推导出D 0-D 7的取值得3分,画出正确的连线图得2分] 解:

1346

0011223344556677134602571,0

F AC AC

ABC A BC AB C A B C m m m m D m D m D m D m D m D m D m D m D D D D D D D D =+=+++=+++=+++++++=经比较得:

=======

4、设0123A A A A 为8421BCD 码,3210B B B B 为余3码,试用加法器74LS283实现0123A A A A 向3210B B B B 转换。

(6分)

[评分标准:有设计过程分析的得3分,画出正确的连线图得3分]

解: 0123A A A A 为8421BCD 码,则其所对应的余3码为321032100011B B B B A A A A =+,设计电路如图。

A A A A 0 0 1 1

B 3 B 2 B 1 B 0

五、综合类型题(共20分)

1、写出如图所示电路的驱动方程和状态方程,列出状态表,画出状态图,并分析电路的逻辑功能,能否自启动? (10分)

第 - 4 -页 共 5 页

[评分标准:驱动方程2,状态方程3,状态表2,分状态图2分,结果1分]

解:①驱动方程:

212110100202

n n n n n n J Q K Q J Q K Q J Q K Q ⎧==⎪==⎨⎪==⎩ 12

n

n

Y Q Q =

②状态方程:

1

n n

n

Q

J Q K Q CP +

=+↓

122222121211

111110101010

000020202n n n n n n n n

n n n n n n n n

n n n n n n n n Q J Q K Q Q Q Q Q Q Q J Q K Q Q Q Q Q Q Q J Q K

Q Q Q Q Q Q +++⎧=+=+=⎪=+=+=⎨⎪=+=+=⎩ ③状态真值表:

④状态转移图:

⑤功能分析:

有效循环的6个状态分别是0~5这6个十进制数字的格雷码,并且在时钟脉冲CP 的作用下,这6个状态是按递增规律变化的,即:

000→001→011→111→110→100→000→…

所以这是一个用格雷码表示的六进制同步加法计数器。

当对第6个脉冲计数时,计数器又重新从000开始计数,并产生输出

Y =1。

该电路不能自启动。

2、用74LS162设计5进制计数器,允许添加适当的逻辑门电路,需写清设计分析过程。

(共10分)

a) 采用复位法(清零)实现。

(5分)

b) 采用置位法(置数)实现,预置数32100011D D D D =。

(5分)

[评分标准:有设计过程分析和反馈逻辑设计的得2分,画出正确的连线图得3分] 解:

① 题目要求用复位法实现5进制计算器,要用到D R 端,此时32100100Q Q Q Q =,只需将2Q 通

过一非门接到D R 端即可,且ET=EP=1, LD =1,CP 接时钟脉冲,0123,,,D D D D 接地。

第 - 5 -页 共 5 页

② 采用置位法实现5进制计算器,要用到

LD

端,预置数3210

0011D D D D =,则3210

0111Q Q Q Q =,只需将210,,Q Q Q 通过一与非门接到LD 端即可,且ET=EP=1, D R =1,CP 接时钟脉冲。