简易逻辑分析仪的设计毕业设计开题报告

简易电路测试仪开题报告

简易电路测试仪开题报告1. 引言电路测试仪是一种广泛应用于电子工程领域的仪器设备,用于检测和分析电路的各种参数和特性。

然而,市场上现有的电路测试仪价格昂贵,使用复杂,对于一般用户来说并不便捷。

因此,本项目旨在设计和制作一种简易电路测试仪,以降低成本,简化操作流程,方便非专业用户进行电路测试。

本文档将介绍开发该电路测试仪项目的背景、目标和计划。

2. 背景电路测试仪广泛应用于电子工程领域,用于测试和分析电路的各种参数,如电压、电流、频率等。

传统的电路测试仪器价格昂贵,操作复杂,通常只有专业电子工程师才能操作和理解测试结果。

对于一般用户来说,这些电路测试仪并不方便和实用。

3. 目标本项目的目标是设计和制作一种简易电路测试仪,以降低成本,简化操作流程,方便非专业用户进行电路测试。

具体目标包括:•成本降低:基于现有的低成本元器件和开源硬件平台进行设计和制作,降低制造和销售成本。

•操作简化:设计简单直观的用户界面,使非专业用户能够方便地进行电路测试,无需复杂的操作步骤。

•测试项目丰富:支持测试电路的各种参数和特性,如电压、电流、频率、电阻等,以满足不同用户的需求。

4. 计划本项目的开发将按照以下计划进行:第一阶段:需求分析和系统设计在第一阶段,我们将进行需求分析和系统设计,具体包括:1.调研市场需求:了解用户对电路测试仪的需求和期望。

2.确定技术要求:确定设计和制作电路测试仪所需的硬件和软件技术要求。

3.系统架构设计:设计电路测试仪的整体系统架构,包括硬件和软件部分。

第二阶段:硬件和软件开发在第二阶段,我们将进行硬件和软件的开发,具体包括:1.硬件开发:根据系统设计要求,选择适当的元器件并进行硬件电路的设计和制作。

2.软件开发:开发控制电路测试仪的软件程序,包括用户界面设计和功能实现。

第三阶段:测试和改进在第三阶段,我们将进行测试和改进,具体包括:1.功能测试:对开发的电路测试仪进行功能测试,确保各项功能能够正常工作。

逻辑分析仪调查报告

逻辑分析仪调查报告一、概述(一)用途逻辑分析仪是数据域的电子测量仪器,主要用于观察和测量多通道数字信号的逻辑关系,广泛应用于数字设备的研制、生产、维修等工作中,还可以应用于教学实验、集成电路测试、无线电技术侦察、雷达侦测和监视等领域。

(二)分类与特点逻辑分析仪可以分为台式逻辑分析仪、虚拟式逻辑分析仪、高档逻辑分析仪和中低档逻辑分析仪等类型产品。

●台式逻辑分析仪的特点台式逻辑分析仪可以独立工作,也可以使用计算机进行程控,可以广泛应用于各种场合。

价格较高,显示屏幕较小。

●虚拟式逻辑分析仪的特点虚拟式逻辑分析仪必须和计算机一起工作,由逻辑分析仪采集数据,利用计算机进行数据的分析和处理,优点是价格较低,可以充分利用计算机的处理能力和大屏幕显示功能,缺点是不能独立工作,应用场合有时受限制。

●高档逻辑分析仪的特点高档逻辑分析仪非常复杂,采样速率很高,配备有复杂的采样探头适配器,主要应用于大规模集成电路的研制和测试,高档数字设备的维修和故障分析。

价格昂贵,使用方法难以掌握。

●中低档逻辑分析仪的特点中低档逻辑分析仪结构较简单,采样速率不很高,只配备简单的采样探头夹具,主要应用于教学实验,简单数字设备的维修和故障分析,价格便宜,应用广泛。

(三)产品国内外现状国产逻辑分析仪带宽在20MHz~100MHz、采样率在500MSa/s以内的中低档产品为主,并有相当的出口量。

高档逻辑分析仪带宽达30GHz、采样率达80GSa/s,被泰克、安捷伦等公司垄断。

(四)技术发展趋势●集成化、小体积已经成为未来逻辑分析仪产品主要的发展趋势;●高带宽、高采样率仍是逻辑分析仪追求的目标。

二、主要品牌调查2.1 泰克公司2.1.1 泰克的产品方案便携式TLA5000B系列逻辑分析仪以可承受的价格结合了高速定时分辨率、快速状态数据收集、合适的记录状态和先进的触发功能。

它是对目前的嵌入式设计进行验证工作的理想选择。

TLA6000系列逻辑分析仪价格低廉,为您调试、验证和优化数字系统的功能提供了所需的性能。

基于Proteus简易逻辑分析仪设计与实现

基于Proteus简易逻辑分析仪设计与实现熊建平【期刊名称】《顺德职业技术学院学报》【年(卷),期】2013(000)004【摘要】A simple logic analyzer development process is introduced based on Proteus. The circuit mainly comprises clock pulse and multichannel standard signal generator circuit,multichannel pulse divider circuit, multichannel electronic analog switch circuit and DC superposition circuit.With Proteus software simulating and debugging,the results show the circuit can display four way stable waveforms on the same screen and realize the logic analyzer function.%本文介绍了一种基于Proteus简易逻辑分析仪开发过程,电路主要包括时钟脉冲和多路标准信号产生器电路、多路脉冲分配器电路、多路电子模拟开关电路、直流叠加电路四个部分,并对设计电路利用Proteus软件进行仿真调试,结果显示在同一屏幕上能同时显示四路稳定波形,实现逻辑分析仪功能。

【总页数】3页(P17-18,22)【作者】熊建平【作者单位】深圳职业技术学院,广东深圳 518055【正文语种】中文【中图分类】TM935【相关文献】1.简易逻辑分析仪的设计与实现 [J], 朱震华;储婉琴2.基于FPGA简易逻辑分析仪的设计与实现 [J], 张俊涛;马文博3.简易逻辑分析仪的设计与实现 [J], 朱榜芹;乔威4.基于STM32的简易逻辑分析仪的设计 [J], 陈杰;沙玉龙5.实用简易逻辑分析仪的设计与实现 [J], 朱震华因版权原因,仅展示原文概要,查看原文内容请购买。

逻辑分析仪的设计与实现

逻辑分析仪的设计与实现庞利会;邓先荣;王军锋【期刊名称】《电力自动化设备》【年(卷),期】2012(32)9【摘要】A simple logic analyzer is designed based on the digital signal acquisition and the storage display principle of digital oscilloscope, including the modules of digital signal generator,data acquisition, trigger control,data storage,display,etc. It takes ARM chip S3C44B0X and FPGA chip EPC2Q208C6 as its system core and adopts multi-stage sampling clock and 32 sampling channels, with high test speed, multiple input channels and multiple trigger modes. The program is written with VHDL,and compiled,integrated and simulated in Quartus II. It is downloaded to FPGA device and the general functions of logical analyzer are successfully implemented, which verifies the correctness of the design.%设计了一款简易逻辑分析仪.采用数字信号采集以及数字示波器存储显示原理,以ARM芯片S3C44B0X与FPGA芯片EPC2Q208C6组成系统核心.该设计由数字信号发生器、数据采集、触发控制、数据存储、显示等模块构成.该设计具有多级采样时钟和32路采样通道,具有测试速率高、多输入通道、触发方式多等优点.采用VHDL编程,在QuartusⅡ下进行编译、综合、仿真,然后下载到FPGA器件上成功实现了逻辑分析的常规功能,验证了该设计的正确性.【总页数】4页(P149-152)【作者】庞利会;邓先荣;王军锋【作者单位】西华大学电气信息学院,四川成都610039;西华大学电气信息学院,四川成都610039;西华大学电气信息学院,四川成都610039【正文语种】中文【中图分类】TP216【相关文献】1.基于Proteus简易逻辑分析仪设计与实现 [J], 熊建平2.便携式逻辑分析仪的设计与实现 [J], 熊鸣;赵秦川3.基于 FPGA 的虚拟逻辑分析仪的设计与实现 [J], 王万昭;张鹏云;和志强4.基于单片机和FPGA的程控型逻辑分析仪设计与实现 [J], 谭联群;胡生亮;付学志5.逻辑分析仪自动测试系统设计与实现 [J], 田芳宁因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA逻辑分析仪设计

摘要逻辑分析仪是一种新型的数字测试仪器。

它应用于微机等数字系统的软件、硬件调试,故障检查,性能分析等过程中。

它可以监测硬件电路工作时的逻辑电平,并加以存储,用图形的方式直观地表达出来,便于用户检测,分析电路设计中的错误。

在数字电路调试中,往往要测试多路信号波形,分析其逻辑关系。

而普通示波器最多只能测试两路信号波形。

在很多数字电路的研究和实验中,往往需要同时查看多路数字信号的时序关系,并且有时信号不是周期性的,只用示波器无法完整的观察了解信号之间的关系,因此需要用到逻辑分析仪(LA)。

逻辑分析仪是数据领域测试仪器中最有效、最有代表性的仪器。

然而自1973年诞生第一台逻辑分析仪至今,逻辑分析仪的普及率仍很低,30%以上的数字设计师没有使用逻辑分析仪,最重要的原因在于其高昂的价格。

基于此,本文提出一种新型的简易逻辑分析仪的设计方法。

本设计以Altera 公司高性能FPGA 芯片为平台, 以VHDL语言为设计工具, 用自上而下的设计方法先对整个系统进行功能划分和定义,然后对划分的每个模块的行为级用VHDL进行描述,LCD 12864液晶显示器为显示工具的简易逻辑分析仪的设计方法。

它具有功能全面,价格低廉,能够实时分析8路数字信号的优点,因此具有很高的实用价值。

关键词:逻辑分析仪;FPGA;VHDL;ABSTRACTLogic analyzer is a new type of digital test equipment. It applies to computer software and other digital systems, hardware debugging, troubleshooting, performance analysis process. It can monitor the hardware circuit when the logic level, and stores, with an intuitive graphical way to express it, to facilitate detection, analysis of the circuit design error. In the digital circuit debugging, often multiple waveforms to test and analyze the logic. Ordinary oscilloscope can only test two-way signal waveform. Digital circuits in many studies and experiments, often need to simultaneously view multiple digital signals, timing relationships, and sometimes the signal is not periodic, only the observation of the oscilloscope can not be the complete understanding of the relationship between the signal and therefore need to use logical analysis Miriam (LA). Logic analyzer data field is the most effective test instruments, the most representative instruments.However, since 1973 the birth of the first logic analyzer so far, the logic analyzer rate is still low, more than 30% of the number of designers are not using logic analyzer, because of its high price.Based on this, we propose a new simple design method of the logic analyzer. The design for Altera's high performance FPGA chip as a platform to VHDL language design tools, top-down design with the first division of the whole system functions and definitions, and then divide each of the modules using VHDL for behavioral description, LCD 12864 LCD display tool for the simple logic analyzer design methods. It has a full-featured, low cost, real-time-channel digital signals, so it can have high practical value.KEY WORDS: logic analyzer; FPGA;VHDL目录摘要 (1)ABSTRACT (2)第1 章绪论 (4)1.1逻辑分析仪在数字科技中的重要地位 (4)1.2逻辑分析仪的发展状况 (7)1.3课题背景及意义 (8)1.4研究目标 (9)1.5工作内容 (9)1.6论文结构 (9)第二章逻辑分析仪硬件设计 (10)2.1硬件组成部分 (10)2.2FPGA的介绍 (10)2.3FPGA优势 (11)2.4FPGA特点 (12)2.5FPGA引脚配置 (14)2.5液晶显示器介绍 (15)2.6硬件描述语言概述 (18)第三章逻辑分析系统设计 (21)3.1统总体结构设计 (21)3.4数据捕获部分 (22)3.5数据显部分 (25)3.6逻辑分析仪系统的仿真 (29)第四章结论与展望 (32)5.1本次毕业设计的总结 (32)5.2基于FPGA逻辑分析仪的展望 (32)参考文献 (34)致谢 (36)附录 (37)第1 章绪论1.1 逻辑分析仪在数字科技中的重要地位一:数字科技对检测仪器的需求20 世纪70 年代以来,大规模集成电路、可编程逻辑器件、高速数据信号处理器和计算机技术等高新技术得到迅猛发展,为解决数字设备、计算机及VLSI 等电路在研制、生产、检修和维护中的测试问题,出现了一类新的测试设备。

简易逻辑分析仪

简易逻辑分析仪安阳⼯学院电⼦信息与电⽓⼯程学院《EDA技术》课程⼤作业题⽬:简易逻辑分析仪班级: 2011级电⼦信息⼯程⼀班评分标准:1、题⽬难易度。

10%2、设计和结论正确,分析清晰合理。

40%3、⼤作业报告阐述清晰,格式规范。

20%4、陈述清晰,回答问题正确。

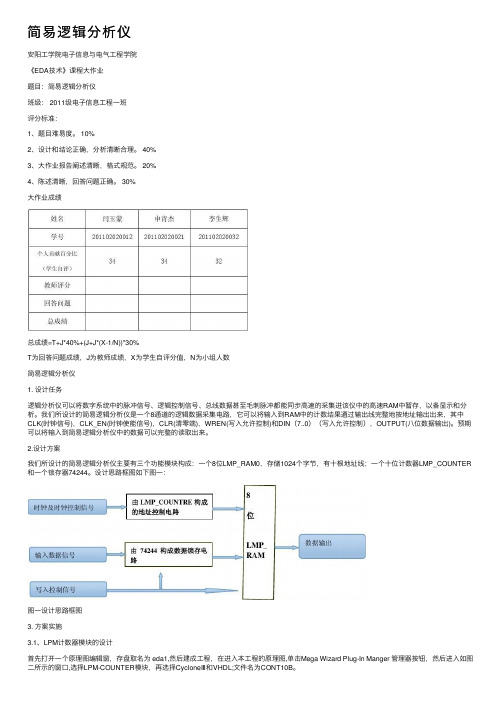

30%⼤作业成绩总成绩=T+J*40%+(J+J*(X-1/N))*30%T为回答问题成绩,J为教师成绩,X为学⽣⾃评分值,N为⼩组⼈数简易逻辑分析仪1. 设计任务逻辑分析仪可以将数字系统中的脉冲信号、逻辑控制信号、总线数据甚⾄⽑刺脉冲都能同步⾼速的采集进该仪中的⾼速RAM中暂存,以备显⽰和分析。

我们所设计的简易逻辑分析仪是⼀个8通道的逻辑数据采集电路,它可以将输⼊到RAM中的计数结果通过输出线完整地按地址输出出来,其中CLK(时钟信号),CLK_EN(时钟使能信号),CLR(清零端),WREN(写⼊允许控制)和DIN(7..0)(写⼊允许控制),OUTPUT(⼋位数据输出)。

预期可以将输⼊到简易逻辑分析仪中的数据可以完整的读取出来。

2.设计⽅案我们所设计的简易逻辑分析仪主要有三个功能模块构成:⼀个8位LMP_RAM0,存储1024个字节,有⼗根地址线;⼀个⼗位计数器LMP_COUNTER 和⼀个锁存器74244。

设计思路框图如下图⼀:图⼀设计思路框图3. ⽅案实施3.1、LPM计数器模块的设计⾸先打开⼀个原理图编辑窗,存盘取名为 eda1,然后建成⼯程,在进⼊本⼯程的原理图,单击Mega Wizard Plug-In Manger 管理器按钮,然后进⼊如图⼆所⽰的窗⼝,选择LPM-COUNTER模块,再选择CycloneⅢ和VHDL;⽂件名为CONT10B。

图⼆从原理图编辑窗进⼊LPM计数器编辑模块最终⽣成的计数器如图三所⽰:图三 LPM计数器模块LPM计数器模块的VHDL⽂件如下:LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY lpm;USE lpm.all;ENTITY cnt10 ISPORT( aclr : IN STD_LOGIC ;clk_en : IN STD_LOGIC ;clock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0)); END cnt10; ARCHITECTURE SYN OF cnt10 ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (9 DOWNTO 0);COMPONENT lpm_counterGENERIC (lpm_direction : STRING;lpm_port_updown : STRING;lpm_type : STRING;lpm_width : NATURAL);PORT (clk_en : IN STD_LOGIC ;aclr : IN STD_LOGIC ;clock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (9 DOWNTO 0));END COMPONENT;BEGINq <= sub_wire0(9 DOWNTO 0);lpm_counter_component : lpm_counterGENERIC MAP (lpm_direction => "UP",lpm_port_updown => "PORT_UNUSED",lpm_type => "LPM_COUNTER",lpm_width => 10)PORT MAP (clk_en => clk_en,aclr => aclr,clock => clock,q => sub_wire0 );END SYN;3.2、LPM随机存储器模块的设计按照以上设计LPM计数器模块,再次打开Mega Wizard Plug-In Manger管理器按钮,然后进⼊如图3所⽰的窗⼝,选择RAM:1-PORT模块,再选择CycloneⅢ和VHDL,⽂件取名为RAM0。

基于VGA显示的逻辑分析仪数字逻辑系统课程毕业设计

基于VGA显示的逻辑分析仪数字逻辑系统课程毕业设计目录摘要.................................................. 错误!未定义书签。

Abstract .................................................. 错误!未定义书签。

引言 (1)1 绪论 (2)1.1 VGA的背景 (2)1.2 VGA的发展与应用 (3)1.3 基于VGA显示的逻辑分析仪的优势 (3)1.4 论文的结构 (4)2 基于VGA显示的逻辑分析仪的设计 (5)2.1 总体方案的设计 (5)2.2 硬件设计的方案 (5)2.3 软件设计的方案 (6)2.4 采用的主要技术 (7)2.4.1 FPGA (7)2.4.2 VHDL语言 (8)2.4.3 Quartus II 7.0开发平台 (9)3 系统硬件电路设计 (10)3.1 FPGA最小系统 (10)3.1.1 配置电路 (10)3.1.2 时钟及复位电路 (11)3.1.3 系统电源 (12)3.2 VGA接口电路 (13)3.2.1 VGA接口概述 (13)3.2.2 VGA接口电路设计 (14)3.3 其他外围电路 (15)3.3.1输入控制电路 (15)3.3.2 状态显示电路 (16)4 系统软件设计 (17)4.1 双口RAM存储模块 (17)4.2 VGA驱动模块 (18)4.2.1 VGA时序 (19)4.2.2 VGA逐行扫描的工作原理 (19)4.3 波形显示控制模块 (21)4.3.1 波形数据存储格式 (21)4.3.2 波形图像显示 (21)4.4 键盘控制显示模块 (23)4.5 其他模块 (23)5功能调试与测试 (25)5.1 按键输入与显示 (25)5.2 系统测试 (26)6 总结及展望 (27)参考文献 (28)致谢.................................................. 错误!未定义书签。

基于VGA显示的逻辑分析仪 毕业论文模版

题目基于VGA显示的逻辑分析仪(显示控制部分)英文题目The Logic Analyzer Based onVGA Display(Display Control)摘要逻辑分析仪是一种有效的、最具代表性的数字逻辑分析仪器,目前得到了广泛的应用,但其昂贵的价格和复杂的操作方式,限制了其在小型实验室或教育机构的使用。

基于台式一体机的设计思想,本文提出了一种采用廉价FPGA实现数字逻辑信号采集,处理,由通用VGA显示器显示数字信号的逻辑分析仪。

VGA显示输出具有兼容性强,显示内容丰富,不需要依靠计算机的优势。

基于一体机的思路,系统硬件分为五大部分,分别为信号输入单元、FPGA核心处理单元、输入控制单元和状态显示单元及VGA接口单元。

分别实现信号的输入整形、采集处理、工作状态显示和显示数据DA转换。

本文采用电阻分压的方式进行色彩信号的DA 转换,将二进制RGB数据帧,转换为对应的模拟电压信号。

最终实现多路逻辑信号的采集、处理,最终将波形数据显示于VGA 显示器上。

逻辑处理部分,采用EDA自上而下的设计思想,首先,按功能划分模块,分为采样触发控制模块、采样频率控制模块、双口RAM 存储模块、波形显示控制模块、VGA 显示驱动模块、键盘显示控制模块六个模块;然后,用VHDL语言设计对应的模块,本文详细分析了VGA逐行扫描的工作原理,并最终实现数据的显示;最后,在系统级的层次,将各个模块有机结合在一起,形成了一个具有十路输入,六种触发方式,采样频率可调,使用通用VGA显示器显示的逻辑分析仪。

本设计利用FPGA芯片和EDA设计方法,实现了廉价实用的逻辑分析仪,既能够大大降低成本,又可以满足生产实践中不断变化的需要。

关键词:VGA;逻辑分析仪;EDA;FPGA- 1-Display Based on the Logic Analyzer DesignAbstractLogic analyzer is an effective, most representative of digital logic devices have been widely used at present, but its high price and complex mode of operation, limited in a small laboratory or educational institution use.Desktop machine based on one design, the paper proposes a low-cost FPGA using digital logic signal acquisition, processing, generic VGA display by the digital signal of the logic analyzer. VGA display output with the compatibility, display rich content and do not need to rely on the computer's advantage.Thinking on one machine, system hardware is divided into five parts, namely, the signal input unit, FPGA core processing unit, input control unit and the status display unit and the VGA interface unit. Respectively, and the signal is input shaping, acquisition and processing, work status, and display data DA conversion. This resistor divider with the way color signals DA conversion, the binary RGB data frame, converted to corresponding analog voltage signal. Ultimately multiple logic signal acquisition, processing, waveform data will eventually be shown on the VGA monitor.Logic processing, we adopt the EDA design from top to bottom, first, by function, module, trigger control module is divided into sampling, the sampling frequency control module, dual-port RAM memory modules, waveform display control module, VGA display driver module, keyboard Display control module 6 module; Then, the corresponding VHDL language design module, the paper analyzes the working principle of progressive scan VGA and, ultimately, the display of data; Finally, the level at the system level, the combination of the various modules in together to form a 10-input, six trigger, the sampling frequency is adjustable using the Universal VGA display logic analyzer.This design using FPGA chip and EDA design, cheap and practical realization of the logic analyzer, not only can greatly reduce the cost and production practices to meet changing needs.Key Words: VGA; Logic Analyzer; EDA; FPGA目录摘要 (I)Abstract (II)引言 (1)1 绪论 (2)1.1 VGA的背景 (2)1.2 VGA的发展与应用 (2)1.3 基于VGA显示的逻辑分析仪的优势 (3)1.4 论文的结构 (3)2 基于VGA显示的逻辑分析仪的设计 (5)2.1 总体方案的设计 (5)2.2 硬件设计的方案 (5)2.3 软件设计的方案 (6)2.4 采用的主要技术 (7)2.4.1 FPGA (7)2.4.2 VHDL语言 (8)2.4.3 Quartus II 7.0开发平台 (9)3 系统硬件电路设计 (10)3.1 FPGA最小系统 (10)3.1.1 配置电路 (10)3.1.2 时钟及复位电路 (11)3.1.3 系统电源 (12)3.2 VGA接口电路 (13)3.2.1 VGA接口概述 (13)3.2.2 VGA接口电路设计 (14)3.3 其他外围电路 (15)3.3.1输入控制电路 (15)3.3.2 状态显示电路 (16)4 系统软件设计 (17)4.1 双口RAM存储模块 (17)4.2 VGA驱动模块 (18)4.2.1 VGA时序 (18)4.2.2 VGA逐行扫描的工作原理 (19)4.3 波形显示控制模块 (21)4.3.1 波形数据存储格式 (21)4.3.2 波形图像显示 (21)4.4 键盘控制显示模块 (22)4.5 其他模块 (23)5功能调试与测试 (24)5.1 按键输入与显示 (24)5.2 系统测试 (25)6 总结及展望 (26)参考文献 (27)3基于VGA显示的逻辑分析仪致谢..................................................................................................... 错误!未定义书签。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

毕业设计(论文)开题报告

题目名称 《简易逻辑分析仪的设计》

学生姓名 专业 班级

一、选题的目的意义

随着集成电路技术的发展和计算机的应用,数字系统的实现方法也经历了由分立元件、

小规模、中规模到大规模、超大规模,直到今天的专用集成电路(ASIC). 然而其调试

和检测也越来越复杂。逻辑分析仪作为电路设计的重要检测工具在现代电路设计中也发

挥着越来越重要的作用。

本人选《简易逻辑分析仪的设计》这个课题有如下目的和意义:

1、通过查阅资料了解当前行业前沿的设计思路和当今逻辑分析仪的现状和未来的发展

方向;

2、培养自己根据要求建立方案并对方案进分析和证论的能力以及自己的计算、和绘图

能力;

3、培养自己分析问题,灵活应用所学知识解决问题并将所学的知识与现实相联系的能

力;

4、培养自己通过利用各种渠道获取自己所需知识信息的能力;

5、提高自己科技论文写作方面的能力;

6、本设计作品可用于实验室中对电路进行简单的测试,同时避免了花费大比资金购买

专用的逻辑分析仪,节约了资本。

二、国内外研究综述

逻辑分析仪是一种类似于示波器的波形测试设备,它可以监测硬件电路工作时的逻

辑电平(高或低),并加以存储,用图形的方式直观地表达出来,便于用户检测,分析电

路设计(硬件设计和软件设计) 中的错误,逻辑分析仪是设计中不可缺少的设备,通过

它,可以迅速地定位错误,解决问题,达到事半功倍的效果。

逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,最主要作用在于时序

判定。由于逻辑分析仪不像示波器那样有许多电压等级,通常只显示两个电压(逻辑1

和0),因此设定了参考电压后,逻辑分析仪将被测信号通过比较器进行判定,高于参

考电压者为High,低于参考电压者为Low,在High与Low之间形成数字波形。根据硬件

设备设计上的差异,目前市面上逻辑分析仪大致上可分为独立式(或单机型)逻辑分析

仪和需结合电脑的PC-based卡式虚拟逻辑分析仪。独立式逻辑分析仪是将所有的测试

软件、运算管理元件以及整合在一台仪器之中;卡式虚拟逻辑分析仪则需要搭配电脑一

起使用,显示屏也与主机分开。

就整体规格而言,独立式逻辑分析仪已发展到相当高标准的产品,例如采样率可达

8GHz、通道数可扩充到300个通道以上,存储深度相对也高,独立式逻辑分析仪以往价

格昂贵,从几万到数十万人民币不等,一般用户很少用得起。最近台湾OItek科技有限

公司推出的OLA2032BTM独立台式EasyDebugTM逻辑分析仪,拥有独立32数据通道,时

序达到250MHZ,状态分析和带宽高达100MHZ,存储深度最大2Mbytes,它既能独立放在

桌面侦测采集需要检测的数字信号,也可以通过高性能软件来对存储和观察捕获的波形

作进一步的分析。性价比高,基本上实现了让每个工程师都用得起。尤其在数字电路教

学中,改变了以往老师为了降低成本使用虚拟逻辑分析仪进而产生的不直观、麻烦等问

题,在同一个价格上,我们可以把台式独立逻辑分析仪很轻松地拎起来。

基于计算机接口的卡式虚拟逻辑分析仪,以较小的成本提供了相应的性能,但是卡式虚

拟逻辑分析仪也有很大缺点,它需要配备电脑才能使用,尤其数字测试中,工程师往往

会陷入一堆PCB板中,采用旋转按钮的仪器要比在屏幕上移动鼠标更加方便。技术的发

展也逐渐把示波器和逻辑分析仪的功能融合在一起,成为混合式的仪器(MSO),也称混

合信号测试仪器。

三、毕业设计(论文)所用的方法

1、首先明确所选课题的任务和要求,积极查阅资料,通过理论知识选取设备并了解

设备的各项性能指标。

2、通过实际动手实验发现问题,请教相关人员和指导老师,解决设计中所遇到的问

题。

3、根据相关的设计标准和规范图籍,使用计算机编辑文档,绘制设备布置图。

4、分析和讨论为了达到目的和目标,系统所必须具备的技术条件,并在分析讨论的

基础上对它们进行整理、归纳成文,明确地确定下来

5、通过图书馆和网络充分查找相关的设计方法和各种工具资料

6、通过查阅资料了解逻辑分析仪的现状以及未来的发展方向,从而对自己的设计有

一个清晰的认识。

四、主要参考文献与资料获得情况

1《全国大学生电子设计竞赛培训教程-电子仪器仪表设计》

2 曹琳琳,曹巧媛编著.《单片机原理及接口技术》.长沙:国防科技大学出版社,2000

3 潘松,黄继业编著.《EDA技术实用教程》.北京:科学出版社,2002

4 蒋璇,臧春华编著.《数字系统设计与PLD应用技术》.北京:电子工业出版社,2001

5 全国大学生电子设计竞赛组委会编著.《全国大学生电子设计竞赛获奖作品精选

(1994-1999)》.北京:北京理工大学出版社,2003

6 楼然苗,李光飞编著.《51系列单片机设计实例》.北京:北京航空航天大学出版社,

2003

7 张世箕, 《数据域测试及仪器》, 电子工业出版社, 1994年11月

8 [美]约输·肯尼 吴运熙、张压西、刘大可译, 《逻辑分析仪》 ,电子工业出版社,

1985年2月

9 刘国林、殷贯西,《电子测量》, 机械工业出版社,2003年1月

10 顾乃绂、孙续 ,逻辑分析仪原理与应用,人民邮电出版社,1989年5月

11 李爱华、王章,高速FIFO存储芯片IDT7207在虚拟逻辑分析仪设计中的应用,期刊

文章,(西南石油学院,四川,成都 610500)

12 张学强 秦龙勇 谢拴勤, 基于FPGA的多路模拟量、数字量采集与处理系统

13戴志坚 师奕兵 王志坚, 逻辑分析仪高速数据采集及数据窗口定位,

期刊文章,(电子科技大学自动化工程学院,成都 610054)

五、指导教师审批意见

年 月 日