半导体二极管门电路

合集下载

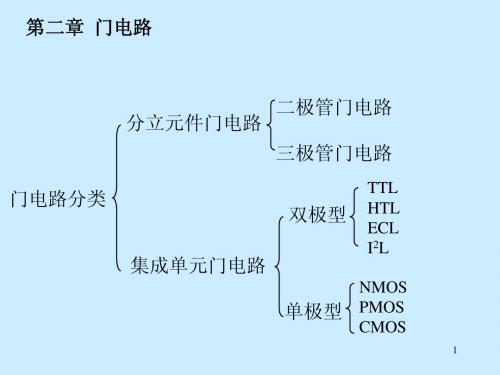

第二章门电路

D off, 假设正确 ID 0 11V 1.5V I1 I 2 2 .5 V (4 1)K

7

§2.2 半导体三极管的开关特性 一. 双极型三极管的结构 IC

IB

VBC – + + + VCE VBE – – IE

NPN Si管

8

二. 特性

1.电流:IE =IB +IC 2.工作状态: 工作状态分类 导通 截止

IC1

T2 • IE2 • Y ° T5

R3

•

IR3

IB5

N—表示N个发射极。

41

●T1的状态:

∵VB1=VBC1+VBE2+VBE5=2.1V ∴T1处于倒置状态。 I C1 I B1 N反 I B1

I B1 VCC VB1 R1

0.73mA

● T2、 T5的状态:

T2、 T5饱和VO=0.3V

45

二.TTL与非门 • R1 4K • Vcc =5V

°

R2 1.6K

•

R4 130

T4

A

B

T1

T2

• R3 1K • 倒相级

D3

• T5 Y °

输入级

输出级

46

三.负载能力分析 负载——指门电路输出端所接的其它 电路。 NO——扇出系数,表示能够驱动同类门的数目。 灌电流负载——负载电流从后级门注入前级门 负载

14

5)饱和条件及特点 条件:IB >IBS IB — 进入饱和以后的基流。 IBS—临界饱和基流。 求IB 、 IBS的步骤: Vi VBE a)I B Rb

b)I CS c)I BS VCC VCES VCC RC RC I CS

7

§2.2 半导体三极管的开关特性 一. 双极型三极管的结构 IC

IB

VBC – + + + VCE VBE – – IE

NPN Si管

8

二. 特性

1.电流:IE =IB +IC 2.工作状态: 工作状态分类 导通 截止

IC1

T2 • IE2 • Y ° T5

R3

•

IR3

IB5

N—表示N个发射极。

41

●T1的状态:

∵VB1=VBC1+VBE2+VBE5=2.1V ∴T1处于倒置状态。 I C1 I B1 N反 I B1

I B1 VCC VB1 R1

0.73mA

● T2、 T5的状态:

T2、 T5饱和VO=0.3V

45

二.TTL与非门 • R1 4K • Vcc =5V

°

R2 1.6K

•

R4 130

T4

A

B

T1

T2

• R3 1K • 倒相级

D3

• T5 Y °

输入级

输出级

46

三.负载能力分析 负载——指门电路输出端所接的其它 电路。 NO——扇出系数,表示能够驱动同类门的数目。 灌电流负载——负载电流从后级门注入前级门 负载

14

5)饱和条件及特点 条件:IB >IBS IB — 进入饱和以后的基流。 IBS—临界饱和基流。 求IB 、 IBS的步骤: Vi VBE a)I B Rb

b)I CS c)I BS VCC VCES VCC RC RC I CS

第3章门电路

&Y

4

第三章门电路

2.二极管或门

图3.2.6 二极管或门

A/V B/V Y/V

000 0 3 2.3 3 0 2.3 3 3 2.3

AB

Y

0

0

0

0

1

1

1

0

1

1

1

1

Y=A+B A

B

A

≥1

Y

Y

B

北方工业大学信息工程学院

叶青制作

5

3.3 TTL门电路

第三章门电路

集成电路(IC):在一块半导体基片上制作出一个完整的逻辑电路所 需要的全部元件和连线。使用时接:电源、输入和输出。

北方工业大学信息工程学院

叶青制作

3

第三章门电路

1.二极管与门

设:VCC=5V, VIH=3V, VIL=0V

A/V 0 0 3 3

B/V 0 3 0 3

Y/V 0.7 0.7 0.7 3.7

AB

Y

00

0

01

0

10

0

11

1

图3.2.5 二极管与门

Y=AB

A B

北方工业大学信息工程学院

YA B

叶青制作

1.电路

(5v)

EN:使能端,控制端 R1

R4 R2

VB1 0.9V 4.3V 0.9V

T4

A B

T1

T2

D3 Y 2.9V

T5 (Vo)

3.6V EN 0.2V

D

R3

3.6V

北方工业大学信息工程学院

叶青制作

31

(三)三态输出门电路(TS) 1.电路

第三章门电路

门电路 (简)资料

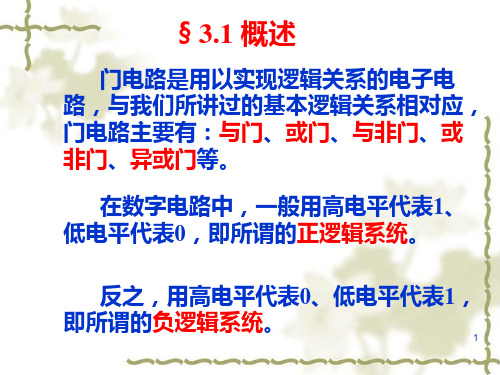

或门等。

门电路的两种输入,输出电平: 高电平、低电平。它们分别对应逻 辑电路的1,0状态。

注意:各种门电路的工作 原理,只要求一般掌握; 而各种门电路的外部特性 和应用是要求重点。

3.1 概述

2. 高低电平

高电平:数字电路中较高电平代数值的范围。

低电平:数字电路中较低电平代数值的范围。

3. 正负逻辑

3.2 半导体二极管门电路

门电路的实现 ——电子开关,用来接通或断开电路的开关器件。 1. 半导体二极管的开关特性

两种工作状态: 二极管具有单向导电性:

正向导通,反向截止,相当于一个受电压控制的 1)接通(要求其阻抗很小,相当于短路) 电子开关。 2 )断开(要求其阻抗很大,相当于开路)

3.2 半导体二极管门电路

当EN= 0时,TG导通,F=A; 当EN= 1时,TG截止,F为高阻输出。

3.3 CMOS门电路

CMOS系列及命名方法

74 FAM nn

HC( High-speed CMOS ,高速 CMOS 系列); 例: 74HC04商用高 HCT(High-speed CMOS, 前缀:74—商用系列;54—军用系列。 速CMOS 六反相 TTL compatible ,与 TTL兼 容的高速CMOS 系列); 助记符:以字母表示系列类型。 器; VHC(Very High-speed CMOS,甚高速 CMOS商用 系 74HCT00 功能数字:以数字表示电路的 列); 高速 CMOS 四 -二 VHCT: Very High-speed 逻辑功能。 CMOS, TTL compatible,与 输入与非门。 TTL兼容的甚高速CMOS 系 列)。

层做包装材料。

3.3 CMOS门电路

3门电路 (简)

门的多余输入端接地。

一般,接电源时需接上拉电阻;接地时需接下拉电阻。 典型值1-10k。 +5V 上拉电阻保持 1k

高电平

A B

F

下拉电阻保持 低电平

A B

C

F

C 1k

3.3 CMOS门电路

电路设计与安装应尽量消除噪声,保证电路稳定工作。

( 1)在每一块插板的电源线上,并接几十 μF 的低频去 耦电容和 0.01~0.047μF 的高频去耦电容,以防止 TTL 电路 的动态尖峰电流产生的干扰。 (2) 整机装置应有良好的接地系统。

表1 各种系列门电路的主要参数

表2 常用集成门电路(TTL系列)

型 号 74LS00 74LS02 74LS04 74LS05 74LS08 74LS13 74LS30 名 称 四2输入与非门 四2输入或非门 六反相器 六反相器 四2输入与门 双4输入与非门 8输入与非门 施密特触发 OC门 主要功能

1. TTL门驱动CMOS门

(1)电平不匹配

TTL门作为驱动门,它的UOH≥2.4V,UOL≤0.5V;

CMOS门作为负载门,它的UIH≥3.5V,UIL≤1V。

可见,TTL门的UOH不符合要求。

(2)电流匹配 CMOS电路输入电流几乎为零,所以不存在问题。

3.5 TTL电路与CMOS电路的接口电路

当EN= 0时,TG导通,F=A; 当EN= 1时,TG截止,F为高阻输出。

3.3 CMOS门电路

CMOS系列及命名方法

74 FAM nn

HC( High-speed CMOS ,高速 CMOS 系列); 例: 74HC04商用高 HCT(High-speed CMOS, 前缀:74—商用系列;54—军用系列。 速CMOS 六反相 TTL compatible ,与 TTL兼 容的高速CMOS 系列); 助记符:以字母表示系列类型。 器; VHC(Very High-speed CMOS,甚高速 CMOS商用 系 74HCT00 功能数字:以数字表示电路的 列); 高速 CMOS 四 -二 VHCT: Very High-speed 逻辑功能。 CMOS, TTL compatible,与 输入与非门。 TTL兼容的甚高速CMOS 系 列)。

数电第三章门电路

15

§3.4 TTL门电路

数字集成电路:在一块半导体基片上制作出一个 完整的逻辑电路所需要的全部元件和连线。 使用时接:电源、输入和输出。数字集成电 路具有体积小、可靠性高、速度快、而且价 格便宜的特点。

TTL型电路:输入和输出端结构都采用了半导体晶 体管,称之为: Transistor— Transistor Logic。

输出高电平

UOH (3.4V)

u0(V)

UOH

“1”

输出低电平

u0(V)

UOL

UOL (0.3V)

1

(0.3V)

2 3 ui(V)

1 2 3 ui(V)

阈值UT=1.4V

传输特性曲线

理想的传输特性 28

1、输出高电平UOH、输出低电平UOL UOH2.4V UOL 0.4V 便认为合格。 典型值UOH=3.4V UOL 0.3V 。

uA t

uF

截止区: UBE< 死区电压, IB=0 , IC=ICEO 0 ——C、 E间相当于开关断开。

+ucc

t

4

0.3V

3.2.3MOS管的开关特 恒流区:UGS>>Uth , UDS

性: +VDD

0V ——D、S间相当于 开关闭合。

R

uI

Uo

Ui

NMO S

uO

夹断区: UGS< Uth, ID=0 ——D、S间相当于开关断开。

3.3.4 其它门电路

一、 其它门电路

其它门电路有与非门、或非门、同或门、异或门等等,比如:

二、 门电路的“封锁”和“打开”问题

A B

&

Y

C

当C=1时,Y=AB.1=AB

§3.4 TTL门电路

数字集成电路:在一块半导体基片上制作出一个 完整的逻辑电路所需要的全部元件和连线。 使用时接:电源、输入和输出。数字集成电 路具有体积小、可靠性高、速度快、而且价 格便宜的特点。

TTL型电路:输入和输出端结构都采用了半导体晶 体管,称之为: Transistor— Transistor Logic。

输出高电平

UOH (3.4V)

u0(V)

UOH

“1”

输出低电平

u0(V)

UOL

UOL (0.3V)

1

(0.3V)

2 3 ui(V)

1 2 3 ui(V)

阈值UT=1.4V

传输特性曲线

理想的传输特性 28

1、输出高电平UOH、输出低电平UOL UOH2.4V UOL 0.4V 便认为合格。 典型值UOH=3.4V UOL 0.3V 。

uA t

uF

截止区: UBE< 死区电压, IB=0 , IC=ICEO 0 ——C、 E间相当于开关断开。

+ucc

t

4

0.3V

3.2.3MOS管的开关特 恒流区:UGS>>Uth , UDS

性: +VDD

0V ——D、S间相当于 开关闭合。

R

uI

Uo

Ui

NMO S

uO

夹断区: UGS< Uth, ID=0 ——D、S间相当于开关断开。

3.3.4 其它门电路

一、 其它门电路

其它门电路有与非门、或非门、同或门、异或门等等,比如:

二、 门电路的“封锁”和“打开”问题

A B

&

Y

C

当C=1时,Y=AB.1=AB

一二极管与门和或门电路与门电路

传输延迟时间

或门电路的传输延迟时间较短,因为其工作机制简单,不需要复杂的计算和比较过程。

或门电路的应用

开关控制

或门电路可以用于实现开关控制功能,例如控制电机正反转、灯光亮灭等。通过将或门电路的输出端连接到控制开关 ,可以实现多个开关信号的“或”逻辑控制。

数据传输

在数据传输领域,或门电路可以用于实现数据总线的读写控制。通过将多个数据信号输入到或门电路中,可以实现同 时对多个数据进行读取或写入操作。

逻辑表达式

或门电路的逻辑表达式为 Y = A + B,其中 A 和 B 为输入信号, Y 为输出信号。

或门电路的特性

输入与输出关系

或门电路的输入与输出关系是非对称的,即输出信号与输入信号不完全相同。在或门电 路中,当输入信号发生变化时,输出信号也会随之变化。

抗干扰能力强

由于或门电路的逻辑表达式为 Y = A + B,因此其抗干扰能力强。即使输入信号中存在 噪声或干扰,只要其中任一信号为高电平,输出信号仍能保持高电平。

时序逻辑

门电路还可以用于实现时序逻辑功能,如触发器、寄存器、计数器 等,广泛应用于计算机、通信等领域。

THANKS FOR WATCHING

感谢您的观看

实现逻辑加法,即当输入端中至少有 一个为高电平(1)时,输出端就为 高电平(1),否则输出端为低电平 (0)。

不同类型门电路的选择

根据逻辑功能需求选择

根据实际电路的逻辑功能需求,选择适当的门电路类型。

根据性能参数选择

比较不同类型门电路的性能参数,如功耗、响应速度、噪声容限等,选择最适合

信号选择

逻辑运算

与门电路可以用于控制电子设备的开 关,如LED灯、电机等。当所有输入 信号都为高电平时,输出信号为高电 平,设备正常工作;否则,输出信号 为低电平,设备关闭。

或门电路的传输延迟时间较短,因为其工作机制简单,不需要复杂的计算和比较过程。

或门电路的应用

开关控制

或门电路可以用于实现开关控制功能,例如控制电机正反转、灯光亮灭等。通过将或门电路的输出端连接到控制开关 ,可以实现多个开关信号的“或”逻辑控制。

数据传输

在数据传输领域,或门电路可以用于实现数据总线的读写控制。通过将多个数据信号输入到或门电路中,可以实现同 时对多个数据进行读取或写入操作。

逻辑表达式

或门电路的逻辑表达式为 Y = A + B,其中 A 和 B 为输入信号, Y 为输出信号。

或门电路的特性

输入与输出关系

或门电路的输入与输出关系是非对称的,即输出信号与输入信号不完全相同。在或门电 路中,当输入信号发生变化时,输出信号也会随之变化。

抗干扰能力强

由于或门电路的逻辑表达式为 Y = A + B,因此其抗干扰能力强。即使输入信号中存在 噪声或干扰,只要其中任一信号为高电平,输出信号仍能保持高电平。

时序逻辑

门电路还可以用于实现时序逻辑功能,如触发器、寄存器、计数器 等,广泛应用于计算机、通信等领域。

THANKS FOR WATCHING

感谢您的观看

实现逻辑加法,即当输入端中至少有 一个为高电平(1)时,输出端就为 高电平(1),否则输出端为低电平 (0)。

不同类型门电路的选择

根据逻辑功能需求选择

根据实际电路的逻辑功能需求,选择适当的门电路类型。

根据性能参数选择

比较不同类型门电路的性能参数,如功耗、响应速度、噪声容限等,选择最适合

信号选择

逻辑运算

与门电路可以用于控制电子设备的开 关,如LED灯、电机等。当所有输入 信号都为高电平时,输出信号为高电 平,设备正常工作;否则,输出信号 为低电平,设备关闭。

数字电路 第二章门电路

DA

DB B

DC

Y

C

R

–5v

第2章 2.2

由以上分析可知: 只有当A、B、C全为 低电平时,输出端才 为低电平。正好符合

或门的逻辑关系。

A

B C

>1

Y

Y= A+B+C

三、 非门电路

第2章 2.2

RA A

RB

+5V

Rc uY=0.3V 设 uA= 3.6V,T饱和导通

• Y

uY= 0.3V

T

Y= 0

3. CMOS与非门

TP1 与TP2并联,TN1 与TN2串联;

当AB都是高电平时TN1 与TN2

TP2

同时导通TP1 与TP2同时截止;

输出Y为低电平。

当AB中有一个是低电平时, B

TN1 与TN2中有一个截止,

TP1 与TP2中有一个导通, 输出Y为高电平。

A

第2章 2. 3

+VDD

TP1 Y

正逻辑:L=0,H=1 ; 负逻辑:H=0,L=1 。

2. 1 半导体二极管、三极管和 MOS管的开关特性

一、理想开关的开关特性: 1 .静态特性 2. 动态特性

二、半导体二极管的开关特性 1.静态特性:

半导体二极管的结构示意图、符号和伏安 特性

一、二极管等效模型

(b)为理想二极管+恒压源模型 (c)为理想二极管模型

当D、S间加上正 向电压后可产生 漏极电流ID 。

第2章 2. 1

UDS

。

S UGS G

D ID

N++

NN++

N型导电沟道

耗尽层

第三章 门电路

当VGS VGS ( th )下 ,i D VGS

2

恒流区

《数字电子技术基础》第五版

漏极特性曲线(分三个区域) 可变电阻区:当VDS较低(近似为0),VGS一定 , 这个电阻受VGS 控制、可变。

VDS i D 常数(电阻)

可变电 阻区

《数字电子技术基础》第五版

(3)MOS管的基本开关电路

(因为Mos管导通时内阻rDS很小, rDS <1K Ω,一般RD>> 1K Ω),

《数字电子技术基础》第五版

(4)MOS管的开关等效电路

C1—栅极的输入电容,其值约为几皮法。

(5)MOS管的几种类型 1.N沟道增强型

+VDD RD D G

《数字电子技术基础》第五版

vI

S

iD v o

当VI VIL VGS ( th ) N NMOS管截止 VO VOH VDD 当VI VIH VGS ( th ) N NMOS管导通 VO VOL 0 所以NMOS管D S间相当于一个受 VI 控制的开关。

Field-Effect Transistor

CMOS: Complementary-Symmetery

Metal-Oxide-Semiconductor

3.3 CMOS门电路 1. MOS管的开关特性

金属层

《数字电子技术基础》第五版

氧化物层 半导体层

PN结

S (Source):源极 G (Gate):栅极 D (Drain):漏极 B (Substrate):衬底

《数字电子技术基础》第五版

低电平输出特性

VOL=f(iOL )

可变电 阻区

VOL=VDS2

2

恒流区

《数字电子技术基础》第五版

漏极特性曲线(分三个区域) 可变电阻区:当VDS较低(近似为0),VGS一定 , 这个电阻受VGS 控制、可变。

VDS i D 常数(电阻)

可变电 阻区

《数字电子技术基础》第五版

(3)MOS管的基本开关电路

(因为Mos管导通时内阻rDS很小, rDS <1K Ω,一般RD>> 1K Ω),

《数字电子技术基础》第五版

(4)MOS管的开关等效电路

C1—栅极的输入电容,其值约为几皮法。

(5)MOS管的几种类型 1.N沟道增强型

+VDD RD D G

《数字电子技术基础》第五版

vI

S

iD v o

当VI VIL VGS ( th ) N NMOS管截止 VO VOH VDD 当VI VIH VGS ( th ) N NMOS管导通 VO VOL 0 所以NMOS管D S间相当于一个受 VI 控制的开关。

Field-Effect Transistor

CMOS: Complementary-Symmetery

Metal-Oxide-Semiconductor

3.3 CMOS门电路 1. MOS管的开关特性

金属层

《数字电子技术基础》第五版

氧化物层 半导体层

PN结

S (Source):源极 G (Gate):栅极 D (Drain):漏极 B (Substrate):衬底

《数字电子技术基础》第五版

低电平输出特性

VOL=f(iOL )

可变电 阻区

VOL=VDS2