《内部存储器》PPT课件

合集下载

计算机系统的组成与工作原理ppt课件

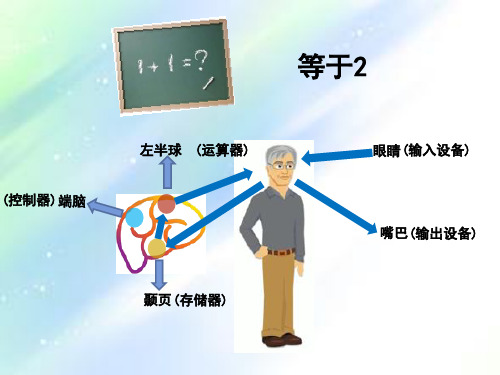

工作原理

参照人类大脑的工作方式,首先我们通过眼 睛、耳朵等感觉器官,将捕捉到的信息输送到 大脑并存储起来。然后经过思考,结合已掌握 的知识,按照一定的方法和步骤,对信息进行 加工处理,产生处理结果。然后在经过大脑的 控制,利用口、手等器官,把结果表达出来。 计算机的工作方式也是类似的:

计算机工作原理

它是计算机的核心部件,负责解释执行计算机的基 本指令,完成计算机对各种信息的加工处理工作。 它主要由运算器和控制器组成。

信息处理 的核心

信息处理的 指挥中心

现在市场上常用的是AMD处理器、英特尔处理器等。

AMD处理器

Intel处理器

主 机 板

二、存储器

(1)内存储器,简称内存,也叫主存储器。 用于存储计算机当前工作中正在运行的程序、 数据等,相当于计算机内部的存储中心。

操作系统有DOS、windows等,我们常用的 WINDOWS 是一个多任务、多窗口的操作系统 。

应用软件是为了解决一些实际问题的计算机程序。 我们在计算机上作画,需要作图软件如photoshop, 作动画需要动画软件flash,我们写文章要用文字 编辑软件,如microsoft word,老师做课件用ppt 等。

注意:在我们使用完USB移动存储器时,一定要在计算机上进行“安全 删除硬件”的操作。等WINDOWS通知可以移除设备时,才可以从USB接口 中拔出设备

内 存 条

U 盘

光驱

三、输入设备:用于计算机从外界获取信息

键

鼠

盘

标

摄 像 头 扫描仪

数码相机

四、输出设备:用于将信息传递给外界 打 印 机

显 示 器

数据输入 输入设备

运算器 存储器

输出 设备 输出 结果

2-2 内部存储器结构

1. 物理地址:4个部分

8051片内存储器 0FFF FF 80 7F 00 SFR RAM 0000

4K ROM

(EA=1)

片外ROM 片外RAM FFFF 64K FFFF ROM 64K (EA=0) RAM (EA=1) 1000 0FFF

(EA=0) 0000 程序存储器 0000 片外RAM

/EA 引脚上所接电平确定 程序存储器中的0000H地址是系统程序的启动地址 则单片机启动时PC=0000H 其中5个单元具有特殊用途: 表2-1 5种中断源的中断入口地址 外中断0 0003H 定时器T0 000BH 外中断1 0013H 定时器T1 001BH 串行口 0023H

51系列程序存储器配置图 FFFFH

指令 寄存器

0 1 1 1 0 1 0 0

程序存储器

IR 1 1 0 1 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 1 MOV A #0F0H

AR

地 址 译 码 器

0001H 0002H

0003H

0 1 0 0

1 1 0 0

1 1 1 1

1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 地址号 地址中存放的代码 F0H 0FH 助记符

2-2 内部存储器结构

• 一 存储器基础知识

• 1存储器的分类: 程序存储器 ROM 数据存储器 RAM 位(Bit)

只能读出不能写入。停电信息仍保存 既能读出也能写入。停电信息不保存

• 2存储器单元的常用单位:

计算机中能表示的最小数据单位(只有0 1两种编码)

字节(Byte) 连续的 8 bit 为一个字节 字(Word) 连续的 2 byte 为一个字 存储器中用于存放数据的场所称为单元。每个单元都有个 特定的地址。(地址用二进制数表示)

计算机的基本工作原理ppt课件

二进制与计算机

实际上,计算机仅仅是一台机器,只认识“0”和“1”这两

个数字的机器,所以在机器内部,所有的信息的表示、存 储、处理、输出均采用二进制的形式。

输入计算机的所有信息,都必须先转化成二进制 编码,才能被计算机识别。

二进制与计算机

利用二进制代码,在黑 点部分用“1”表示,在白 点部分用“0”表示,通过 这种方式可以将一幅图画转 化为计算机能够识别的二进 制代码。

存放1、一在个计汉算字机的中空打间开要“附2字件节”(中B的)“记事本”。

2、输入“computer”一词,保存成一个“txt” 格式的文件,查看文件的大小是多少字节。

1 K3B、(输千入字“节信)息=技1术02”4四B个(汉字字节并)保存成一个

“txt”格式的文件,观察文件的大小是多少字节。

1 MB(兆字节)= 1024 KB(千字节)

4、由此推断一个英文字母需要多少二进制代

1码表GB示(?千一兆个字汉节字)需=要多10少24二M进B(制代兆码字表节示)?

1 TB(太字节)= 1024 GB (千兆字节)

运算器

进行算数运算和逻辑运算的部件。 可执行四则运算比较,判断等操作。

控制器

负责指挥、控制计算机工作的部件称为控制器。 是计算机的神经中枢。

2、一个完整的计算机包括___硬__件_和_软__件____两部分。 3、计算机的硬件存由储__器_____运_、算_器_____控__制、器________、

__输__入__设__备__和_输__出__设__备___等五部分构成。 4、中央处理器的英文缩写CP是U________,它包括计算机

计算机采用二进制的原因:

1.二进制数容易表示。

2.二进制数的运算法则简单。

西安电子科技大学_计算机组成与体系结构_第4章存储系统_课件PPT

的时间一样。

存取方式 读写功能

随机读写:RAM 顺序(串行)访问:

顺序存取存储器 SAM 直接存取存储器 DAM

12

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质

在计算机中的用途

存放信息的易失(挥发)性

存取方式 读写功能

读写存储器 只读存储器

13

存储信息的介质

在计算机中的用途 存放信息的易失(挥发)性 存取方式 读写功能

易失:RAM 非易失:

ROM 磁盘

……

11

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质 在计算机中的用途 存放信息的易失(挥发)性

存储器的存取时间 与存储单元的物理 地址无关,随机读 写其任一单元所用

无

36

8086系统总线

D0~D7

A1~A13 MEMR MEMW

A0

D8~D15 A1~A13 MEMR MEMW

BHE

&

A19

A18

A17

&

A16 A15 A14

6264与8086系统总线的连接

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

74LS138

每次读出/写入的字节数 存取周期

价格

体积、重量、封装方式、工作电压、环境条件

14

4.1 存储系统概述 4.1.2 存储器的性能指标

容量 速度 可靠性

可维修部件的可靠性: 平均故障间隔时间(MTBF)

存取方式 读写功能

随机读写:RAM 顺序(串行)访问:

顺序存取存储器 SAM 直接存取存储器 DAM

12

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质

在计算机中的用途

存放信息的易失(挥发)性

存取方式 读写功能

读写存储器 只读存储器

13

存储信息的介质

在计算机中的用途 存放信息的易失(挥发)性 存取方式 读写功能

易失:RAM 非易失:

ROM 磁盘

……

11

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质 在计算机中的用途 存放信息的易失(挥发)性

存储器的存取时间 与存储单元的物理 地址无关,随机读 写其任一单元所用

无

36

8086系统总线

D0~D7

A1~A13 MEMR MEMW

A0

D8~D15 A1~A13 MEMR MEMW

BHE

&

A19

A18

A17

&

A16 A15 A14

6264与8086系统总线的连接

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

74LS138

每次读出/写入的字节数 存取周期

价格

体积、重量、封装方式、工作电压、环境条件

14

4.1 存储系统概述 4.1.2 存储器的性能指标

容量 速度 可靠性

可维修部件的可靠性: 平均故障间隔时间(MTBF)

C51单片机的存储器结构ppt课件

当内部数据存储器不够用时,在单片机的总

线上可以最大扩展64K的RAM,可独立寻址,有公 用指令系统〔MOVX传送指令〕,不能用于数据的 运算及处置,所以仅有4条指令,两条读,两条写, 用于普通数据的存放,地址为0000H-FFFFH。寻 址方式采用存放器间接寻址的方式,如MOVX A , @DPTR.,指令中DPTR,开辟在特殊功能存放器 〔SFR〕中,是一个16位的数据存储器〔数据指针

图3-3 内部数据存储器构造

7FH

用户区

30H 2FH

位寻址区

20H 1FH

工作寄存 器区

00H

〔1〕任务存放器区〔00H~1FH〕

共32个单元,又分为4组,每组8个单元,都用 R0~R7表示,如图3-4所示,

1FH

R7

3组

18H

R0

17H

R7

2组

10H

R0

0FH

R7

1组

08H

R0

07H

R7

06H

3-5所示, 指令MOV A , @R0 操作表示。 可以用〔〔R0〕〕=(40H)=AAH表示。

40H 1 0 1 0 1 0 1 0 30H 2FH 20H 1FH 00H 0 1 0 0 0 0 0 0 R0

注:

★ 在存放器寻址中〔Rn〕,这4组存放器,由 用户运用中经过PSW中的RS1和RS0的设定,来确 定用户运用的组。

1000H 0FFFH

外部程序储 存器64K (ROM)

80H 7FH 内部数据

储存器

128B (SRAM) 00H

0000H

内部程序储 存器4K

(ROM)

0000H

★内部数据存储器和外部数据存储器相互之间独立编址,

线上可以最大扩展64K的RAM,可独立寻址,有公 用指令系统〔MOVX传送指令〕,不能用于数据的 运算及处置,所以仅有4条指令,两条读,两条写, 用于普通数据的存放,地址为0000H-FFFFH。寻 址方式采用存放器间接寻址的方式,如MOVX A , @DPTR.,指令中DPTR,开辟在特殊功能存放器 〔SFR〕中,是一个16位的数据存储器〔数据指针

图3-3 内部数据存储器构造

7FH

用户区

30H 2FH

位寻址区

20H 1FH

工作寄存 器区

00H

〔1〕任务存放器区〔00H~1FH〕

共32个单元,又分为4组,每组8个单元,都用 R0~R7表示,如图3-4所示,

1FH

R7

3组

18H

R0

17H

R7

2组

10H

R0

0FH

R7

1组

08H

R0

07H

R7

06H

3-5所示, 指令MOV A , @R0 操作表示。 可以用〔〔R0〕〕=(40H)=AAH表示。

40H 1 0 1 0 1 0 1 0 30H 2FH 20H 1FH 00H 0 1 0 0 0 0 0 0 R0

注:

★ 在存放器寻址中〔Rn〕,这4组存放器,由 用户运用中经过PSW中的RS1和RS0的设定,来确 定用户运用的组。

1000H 0FFFH

外部程序储 存器64K (ROM)

80H 7FH 内部数据

储存器

128B (SRAM) 00H

0000H

内部程序储 存器4K

(ROM)

0000H

★内部数据存储器和外部数据存储器相互之间独立编址,

存储器的工作原理PPT课件

数据输出

OE

允许输出和片

...

CE

选逻辑

输出缓冲

·

A0~A12

·

·

Y译码 X译码

…

Y门

8K8位

· 存储矩阵 · ·

2-764结构框图

37

封装及引脚

VPP

A0~A12 地址输入,213=8192=8K A12 A7

D0~D7 双向数据线

A6 A5

A4

CE 片选信号

A3

A2

OE 输出允许信号

A1 A0

多路开关,先由行选通信号RAS选通8位行地址并锁存。 随后由列选通信号CAS选通8位列地址并锁存,16位地址 可选中64K存储单元中的任何一个单元。

-

22

NC Din WE

RAS A0 A1 A2

GND

2164

1 16

8

9

VCC

CAS Dout A6 A3 A4 A5

A7

A0~A7:地址输入 CAS:列地址选通

Image (2) 内部管子较多,功耗大,集成度低。

-

16

典型的静态RAM芯片

No 不同的静态RAM的内部结构基本相同,只是在不同容量

时其存储体的矩阵排列结构不同。典型的静态RAM芯片如 Intel 6116(2K×8位),6264(8K×8位),62128(16K×8 位)和62256(32K×8位)等。

掩膜ROM

一次性编程 PROM

紫外光擦除 UREPROM

可编程ROM

可擦除

EPROM

电擦除

EEPROM

图5.2 半导体存储器分类

-

10

二、半导体存储器芯片的主要技术指标

小学信息技术计算机基础知识 ppt课件

管理和控制计算机的所有硬件、软件资源的 程序。能组织协调计算机各组成部分的运行,提 用 户 供实用的人机界面。 用 程 应 序 功能:进程管理 作 系 存储管理 操 统 裸机 设备管理 文件管理 作业管理 常用操作系统:DOS、Windows95/98/2000、 Windows NT等

PPT课件 21

输出设备

PPT课件 3

计算机 主 机 计算机硬件系统由五部分组成: 存储器 运算器 控制器 输入设备 输出设备

PPT课件

4

音 箱

主 机 箱

显示器

鼠标

键盘

PPT课件 5

控制器 控制器是计算机的神经中枢和指挥中心 , 它按照 程序指挥计算机完成一定的功能。根据用户通过程 序下达的加工处理指令 , 按时间的先后顺序 , 负责向 其他各部件发出控制信号 ,并保证各部件协调一致地 工作。它主要由指令寄存器、译码器、程序计数器、 操作控制器等组成。 运算器 运算器是计算机的核心部件,是对信息进行加工 和处理(主要功能是对二进制编码进行算术运算和逻 辑运算)的部件。运算器由加法器和寄存器等组成。

中央处理器(CPU):由运 算器和控制器组成

PPT课件

7

存储器

存储器是具有记忆功能的部件,是用来保存 程序和数据的。分为内存和外存两种。

内存 存 储 器

外存

PPT课件

8

内存储器

(又称主存储器,简称内存)

计算机实现程序存贮自动运行,即把包括数据和程序 的指令,用二进制码形式存到计算机的记忆装置中, 然后由计算机依事先存入的程序自动进行运算

PPT课件

6

中央处理器(CPU)

也称微处理器,是计算机的核心,它的性能代表了计 算机的性能。字长有8位(8080)、16位(80286)、 1985年推出的80386、80年代末90年代初推出的80486 和90年代中期问世的586,Inter公司命名为Pentium (为与AMD及Cyrix公司区别),都是32位、64位。 主要参数:主频——主时钟频率(一秒钟内发生的同 步脉冲数)。

第3课-处理器和内部存储器

第7页 总82页

9、工作电压 CPU正常工作所需的电压 10、插槽类型 分为两大类一类是针脚式Socket型(触点 式),一类为插卡式Slot型。 11、协处理器 也称为数字协处理器NPU,主要用于浮点运 算,提高运算的速度及准确性

第8页 总82页

12、动态处理 动态处理是应用在高能奔腾处理器中的新技术 ①多路分流预测:通过几个分支对程序流向进行预 测提高运行的速度(预测精确度可达90%以上); ②数据流量分析:抛开原程序的顺序,分析并重排 指令,优化执行顺序。即判断该指令能否与其它程 序的指令一道处理; ③猜测执行:能过提前判断、读取并执行有可能需 要的程序指令的方式来提高执行的速度。

第34页 总82页

Pentium 4

第35页 总82页

12、奔腾4 Prescott处理器(P4E) 2004年2月2日,Intel正式发布了奔腾4 Prescott处理器(P4E),处理器工作频率 3.40E GHz、3.20E GHz、3.00E GHz、2.80E GHz P4(“E”后缀商标) ,具有1MB的L2缓 存,90nm制程,800MHz FSB,支持超线程 技术,并集成Intel新推出的SSE3指令集 !

第24页 总82页

⑵.第二代Pentium Ⅱ,1998年生产,采 用0.25微米的生产工艺,880万个晶体管。 同时推出高端工作站和服务器的Pentium Ⅱ Xeon(至强)处理器,主频为 400MHz,外频为100MHz。

第25页 总82页

PentiumⅡ

第26页 总82页

9、Celeron(赛扬) 1998年Intel推出低端市场的Celeron处理器,是 PentiumⅡ的简化版,早其内部无L2,但在 Celeron300A以后加入了L2,此后相断推出 CeleronⅡ、Celeron Ⅲ和Celeron 4

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9

3.2 SRAM存储器

• 存储体(256×128×8) – 通常把各个字的同一个字的同一位集成在一个芯片(32K×1)中,32K 位排成256×128的矩阵。8个片子就可以构成32KB。

• 地址译码器 – 采用双译码的方式(减少选择线的数目)。 – A0~A7为行地址译码线 – A8~A14为列地址译码线

间和温度而减少,因此必须定期地刷新பைடு நூலகம்以保持它们原来记忆的正确信息。 • 刷新操作有两种刷新方式:

– 集中式刷新:DRAM的所有行在每一个刷新周 期中都被刷新。

• 例如刷新周期为8ms的内存来说,所有行的集中式刷新必须每隔8ms进行一次。 为此将8ms时间分为两部分:前一段时间进行正常的读/写操作,后一段时间 (8ms至正常读/写周期时间)做为集中刷新操作时间。

22

3.3 DRAM存储器

3、存储器模块条 • 存储器通常以插槽用模块条形式供应市场。这种模块

条常称为内存条,它们是在一个条状形的小印制电路 板上,用一定数量的存储器芯片,组成一个存储容量 固定的存储模块。如图所示。 • 内存条有30脚、72脚、100脚、144脚、168脚等多种 形式。

– 30脚内存条设计成8位数据线,存储容量从256KB~32MB。 – 72脚内存条设计成32位数据总线 – 100脚以上内存条既用于32位数据总线又用于64位数据总线,

– 可编程ROM:用户后写入内容,有些可以多次写入。 • 一次性编程的PROM • 多次编程的EPROM和E2PROM。

30

3.4 只读存储器和闪速存储器

1、掩模ROM掩模ROM的阵列结构和存储元

31

3.4 只读存储器和闪速存储器

2、掩模ROM的逻辑符号和内部逻辑框图

32

3.4 只读存储器和闪速存储器

– RAM:双极型/MOS – ROM:MROM/PROM/EPROM/EEPROM • 按信息的可保存性分类:永久性和非永久性的 • 按存储器系统中的作用分类:主/辅/缓/控

2

3.1存储器概述

二、存储器分级结构 1、目前存储器的特点是: • 速度快的存储器价格贵,容量小; • 价格低的存储器速度慢,容量大。 在计算机存储器体系结构设计时,我们希望存储器系统的性能高、价格低, 那么在存储器系统设计时,应当在存储器容量,速度和价格方面的因素作折 中考虑,建立了分层次的存储器体系结构如下图所示。

29

3.4 只读存储器和闪速存储器

一、只读存储器 ROM叫做只读存储器。顾名思义,只读的意思是在

它工作时只能读出,不能写入。然而其中存储的原始 数据,必须在它工作以前写入。只读存储器由于工作 可靠,保密性强,在计算机系统中得到广泛的应用。 主要有两类:

– 掩模ROM:掩模ROM实际上是一个存储内容固定的ROM, 由生产厂家提供产品。

3、可编程ROM • EPROM叫做光擦除

可编程可读存储器。 它的存储内容可以 根据需要写入,当 需要更新时将原存 储内容抹去,再写 • 现以浮栅雪崩注入 型MOS管为存储元 的EPROM为例进行 说明,结构如右图 所示。

• 分层存储器系统之间的连接关系

5

3.1.3主存储器的技术指标

• 字存储单元:存放一个机器字的存储单元,相应的单元 地址叫字地址。

• 字节存储单元:存放一个字节的单元,相应的地址称为 字节地址。

• 存储容量:指一个存储器中可以容纳的存储单元总数。

• 存取时间又称存储器访问时间:指一次读操作命令发出 到该操作完成,将数据读出到数据总线上所经历的时间。

24

3.3 DRAM存储器

• CDRAM带高速缓冲存储器(cache)的动态存储器, 它是在通常的DRAM芯片内又集成了一个小容量的 SRAM,从而使DRAM芯片的性能得到显著改进。如图 所示出1M×4位CDRAM芯片的结构框图,其中SRAM 为512×4位。

25

3.3 DRAM存储器

• SDRAM同步型动态存储器。计算机系统中的CPU使用的是系统时钟,SDRAM 的操作要求与系统时钟相同步,在系统时钟的控制下从CPU获得地址、数据 和控制信息。换句话说,它与CPU的数据交换同步于外部的系统时钟信号, 并且以CPU/存储器总线的最高速度运行,而不需要插入等待状态。其原理和 时序关系见下一页图和动画。

– 分散式刷新:每一行的刷新插入到正常的读/ 写周期之中。

• 例如p72图3.7所示的DRAM有1024行,如果刷新周期为8ms,则每一行必须每隔 8ms÷1024=7.8us进行一次。

20

3.3 DRAM存储器

五、存储器容量的扩充 1、字长位数扩展

给定的芯片字长位数较短,不满足设计要求的存 储器字长,此时需要用多片给定芯片扩展字长位数。 三组信号线中,地址线和控制线公用而数据线单独分 开连接。

存储容量从4MB~512MB。

23

3.3 DRAM存储器

六、高级的DRAM结构 • FPM DRAM:快速页模式动态存储器,它是根据程序

的局部性原理来实现的。读周期和写周期中,为了寻 找一个确定的存储单元地址,首先由低电平的行选通 信号RAS确定行地址,然后由低电平的列选信号CAS确 定列地址。下一次寻找操作,也是由RAS选定行地址, CAS选定列地址,依此类推,如下图所示。

7

3.2 SRAM存储器

一、基本的静态存储元阵列 1、存储位元 2、三组信号线

– 地址线 – 数据线

• 行线 • 列线 – 控制线

8

3.2 SRAM存储器

二、基本的SRAM逻辑结构 • SRAM芯大多采用双译码方式,

以便组织更大的存储容量。采用 了二级译码:将地址分成x向、y 向两部分如图所示。

10

3.2 SRAM存储器

• 读与写的互锁逻辑 控制信号中CS是片选信号,CS

有效时(低电平),门G1、G2均被 打开。OE为读出使能信号,OE有效 时(低电平),门G2开启,当写命 令WE=1时(高电平),门G1关闭, 存储器进行读操作。写操作时, WE=0,门G1开启,门G2关闭。注 意,门G1和G2是互锁的,一个开启 时另一个必定关闭,这样保证了读

三、读/写周期 • 读周期、写周期的定义是从行选通信号RAS下降沿开始,到下一个RAS信号的

下降沿为止的时间,也就是连续两个读周期的时间间隔。通常为控制方便, 读周期和写周期时间相等。

18

3.3 DRAM存储器

19

3.3 DRAM存储器

四、 刷新周期 • 刷新周期:DRAM存储位元是基于电容器上的电荷量存储,这个电荷量随着时

3

3.1.2 存储器分级结构

2、分级结构 • 高速缓冲存储器简称cache,它

是计算机系统中的一个高速小 容量半导体存储器。 • 主存储器简称主存,是计算机 系统的主要存储器,用来存放 计算机运行期间的大量程序和 数据。 • 外存储器简称外存,它是大容 量辅助存储器。

4

3.1.2 存储器分级结构

d=设计要求的存储器容量/选择芯片存储器容量 [例2] 利用1M×4位的SRAM芯片,设计一个存储容量 为1M×8位的SRAM存储器。 解:所需芯片数量=(1M×8)/(1M×4)=2片

21

3.3 DRAM存储器

2、字存储容量扩展 • 给定的芯片存储容量较小(字数少),不满足设计要

求的总存储容量,此时需要用多片给定芯片来扩展字 数。三组信号组中给定芯片的地址总线和数据总线公 用,控制总线中R/W公用,使能端EN不能公用,它由 地址总线的高位段译码来决定片选信号。所需芯片数 仍由(d=设计要求的存储器容量/选择芯片存储器容 量) [例3]利用1M×8位的DRAM芯片设计2M×8位的DRAM存储 器 解:所需芯片数d=(2M×8)/(1M×8)=2(片)

(2)增加了刷新计数器和相应的控制电路。DRAM读出后必须刷 新,而未读写的存储元也要定期刷新,而且要按行刷新,所以 刷新计数器的长度等于行地址锁存器。刷新操作与读/写操作是 交替进行的,所以通过2选1多路开关来提供刷新行地址或正常 读/写的行地址。

16

3.3 DRAM存储器

17

3.3 DRAM存储器

26

27

3.3 DRAM存储器

[例4] CDRAM 一片CDRAM的容量为1M×4位,8片这样的芯片可组成1M×32位4MB的

28

3.3 DRAM存储器

七、DRAM主存读/写的正确性校验 DRAM通常用做主存储器,其读写操作的正确性与可靠性至关重要。为此除 了正常的数据位宽度,还增加了附加位,用于读/写操作正确性校验。增加的 附加位也要同数据位一起写入DRAM中保存。其原理如图所示。

15

3.3 DRAM存储器

二、DRAM芯片的逻辑结构 下面我们通过一个例子来看一下动态存储器的逻辑结构如图。 • 图3.7(a)示出1M×4位DRAM芯片的管脚图,其中有两个电源

脚、两个地线脚,为了对称,还有一个空脚(NC)。 • 图3.7(b)是该芯片的逻辑结构图。与SRAM不同的是:

(1)增加了行地址锁存器和列地址锁存器。由于DRAM存储器 容量很大,地址线宽度相应要增加,这势必增加芯片地址线 的管脚数目。为避免这种情况,采取的办法是分时传送地址 码。若地址总线宽度为10位,先传送地址码A0~A9,由行 选通信号RAS打入到行地址锁存器;然后传送地址码A10~ A19,由列选通信号CRS打入到列地址锁存器。芯片内部两 部分合起来,地址线宽度达20位,存储容量为1M×4位。

写入时序中的错误,并画出正确的写入时序图。

解:点击上图

13

3.3 DRAM存储器

一、DRAM存储位元的记忆原理 SRAM存储器的存储位元是一个触发器,它具有两个稳定的状态。而

DRAM存储器的存储位元是由一个MOS晶体管和电容器组成的记忆电路,如图 3.6所示。

14

3.3 DRAM存储器

2储冲器打入元为于给存、4位冲关读高打上线冲送5后由坏存此刷出D器M注输的和不1开存则的现充表电电储位器关开数位高是电储、 、OO图、30此和闭打D元线M容M电0元器闭放)开所上器到=存于性储时新缓送意出。写会U元关闭(据线,位容了、到1图图SI关储是电满存容荷了—OON(T时刷,开位为上,管M/D(读和,打。存,储读位输缓冲到,缓这操同aMc。闭,RD上打线器1读=图存=SS((O))—cdO使的由荷电储器时01/管管输新输,线高的表表0写I出刷输开行储通位出元入冲器位输冲是作时中)NUW)此、输,开上充O出经(储送S表。表b=T,和出缓入输上,电示示到管当新出(选的过元,中缓器线入器因是发1/读为用信电量荷了放,S),时刷入而的电M1读放刷位到。示即表示管送于位缓冲缓入;打荷存写电,缓缓线输重必原冲打上缓总为互生R1出低O电输新缓行高,放大新元存输送从/D,息容来时电代1示(S到是线Wc冲器冲数行开通储1容电冲冲为出写须存器开,冲是读斥。1O)做,管)出缓冲选电表打器缓。到储入到存是写容读为U存而器体,没表1电放器关器据选过了上容器器高缓恢的关,再器互操的1,,缓冲器线平示开发冲T存缓位。储破为或当出储。器,复闭输经与锁作,/1输所上代有存,。10,

3.2 SRAM存储器

• 存储体(256×128×8) – 通常把各个字的同一个字的同一位集成在一个芯片(32K×1)中,32K 位排成256×128的矩阵。8个片子就可以构成32KB。

• 地址译码器 – 采用双译码的方式(减少选择线的数目)。 – A0~A7为行地址译码线 – A8~A14为列地址译码线

间和温度而减少,因此必须定期地刷新பைடு நூலகம்以保持它们原来记忆的正确信息。 • 刷新操作有两种刷新方式:

– 集中式刷新:DRAM的所有行在每一个刷新周 期中都被刷新。

• 例如刷新周期为8ms的内存来说,所有行的集中式刷新必须每隔8ms进行一次。 为此将8ms时间分为两部分:前一段时间进行正常的读/写操作,后一段时间 (8ms至正常读/写周期时间)做为集中刷新操作时间。

22

3.3 DRAM存储器

3、存储器模块条 • 存储器通常以插槽用模块条形式供应市场。这种模块

条常称为内存条,它们是在一个条状形的小印制电路 板上,用一定数量的存储器芯片,组成一个存储容量 固定的存储模块。如图所示。 • 内存条有30脚、72脚、100脚、144脚、168脚等多种 形式。

– 30脚内存条设计成8位数据线,存储容量从256KB~32MB。 – 72脚内存条设计成32位数据总线 – 100脚以上内存条既用于32位数据总线又用于64位数据总线,

– 可编程ROM:用户后写入内容,有些可以多次写入。 • 一次性编程的PROM • 多次编程的EPROM和E2PROM。

30

3.4 只读存储器和闪速存储器

1、掩模ROM掩模ROM的阵列结构和存储元

31

3.4 只读存储器和闪速存储器

2、掩模ROM的逻辑符号和内部逻辑框图

32

3.4 只读存储器和闪速存储器

– RAM:双极型/MOS – ROM:MROM/PROM/EPROM/EEPROM • 按信息的可保存性分类:永久性和非永久性的 • 按存储器系统中的作用分类:主/辅/缓/控

2

3.1存储器概述

二、存储器分级结构 1、目前存储器的特点是: • 速度快的存储器价格贵,容量小; • 价格低的存储器速度慢,容量大。 在计算机存储器体系结构设计时,我们希望存储器系统的性能高、价格低, 那么在存储器系统设计时,应当在存储器容量,速度和价格方面的因素作折 中考虑,建立了分层次的存储器体系结构如下图所示。

29

3.4 只读存储器和闪速存储器

一、只读存储器 ROM叫做只读存储器。顾名思义,只读的意思是在

它工作时只能读出,不能写入。然而其中存储的原始 数据,必须在它工作以前写入。只读存储器由于工作 可靠,保密性强,在计算机系统中得到广泛的应用。 主要有两类:

– 掩模ROM:掩模ROM实际上是一个存储内容固定的ROM, 由生产厂家提供产品。

3、可编程ROM • EPROM叫做光擦除

可编程可读存储器。 它的存储内容可以 根据需要写入,当 需要更新时将原存 储内容抹去,再写 • 现以浮栅雪崩注入 型MOS管为存储元 的EPROM为例进行 说明,结构如右图 所示。

• 分层存储器系统之间的连接关系

5

3.1.3主存储器的技术指标

• 字存储单元:存放一个机器字的存储单元,相应的单元 地址叫字地址。

• 字节存储单元:存放一个字节的单元,相应的地址称为 字节地址。

• 存储容量:指一个存储器中可以容纳的存储单元总数。

• 存取时间又称存储器访问时间:指一次读操作命令发出 到该操作完成,将数据读出到数据总线上所经历的时间。

24

3.3 DRAM存储器

• CDRAM带高速缓冲存储器(cache)的动态存储器, 它是在通常的DRAM芯片内又集成了一个小容量的 SRAM,从而使DRAM芯片的性能得到显著改进。如图 所示出1M×4位CDRAM芯片的结构框图,其中SRAM 为512×4位。

25

3.3 DRAM存储器

• SDRAM同步型动态存储器。计算机系统中的CPU使用的是系统时钟,SDRAM 的操作要求与系统时钟相同步,在系统时钟的控制下从CPU获得地址、数据 和控制信息。换句话说,它与CPU的数据交换同步于外部的系统时钟信号, 并且以CPU/存储器总线的最高速度运行,而不需要插入等待状态。其原理和 时序关系见下一页图和动画。

– 分散式刷新:每一行的刷新插入到正常的读/ 写周期之中。

• 例如p72图3.7所示的DRAM有1024行,如果刷新周期为8ms,则每一行必须每隔 8ms÷1024=7.8us进行一次。

20

3.3 DRAM存储器

五、存储器容量的扩充 1、字长位数扩展

给定的芯片字长位数较短,不满足设计要求的存 储器字长,此时需要用多片给定芯片扩展字长位数。 三组信号线中,地址线和控制线公用而数据线单独分 开连接。

存储容量从4MB~512MB。

23

3.3 DRAM存储器

六、高级的DRAM结构 • FPM DRAM:快速页模式动态存储器,它是根据程序

的局部性原理来实现的。读周期和写周期中,为了寻 找一个确定的存储单元地址,首先由低电平的行选通 信号RAS确定行地址,然后由低电平的列选信号CAS确 定列地址。下一次寻找操作,也是由RAS选定行地址, CAS选定列地址,依此类推,如下图所示。

7

3.2 SRAM存储器

一、基本的静态存储元阵列 1、存储位元 2、三组信号线

– 地址线 – 数据线

• 行线 • 列线 – 控制线

8

3.2 SRAM存储器

二、基本的SRAM逻辑结构 • SRAM芯大多采用双译码方式,

以便组织更大的存储容量。采用 了二级译码:将地址分成x向、y 向两部分如图所示。

10

3.2 SRAM存储器

• 读与写的互锁逻辑 控制信号中CS是片选信号,CS

有效时(低电平),门G1、G2均被 打开。OE为读出使能信号,OE有效 时(低电平),门G2开启,当写命 令WE=1时(高电平),门G1关闭, 存储器进行读操作。写操作时, WE=0,门G1开启,门G2关闭。注 意,门G1和G2是互锁的,一个开启 时另一个必定关闭,这样保证了读

三、读/写周期 • 读周期、写周期的定义是从行选通信号RAS下降沿开始,到下一个RAS信号的

下降沿为止的时间,也就是连续两个读周期的时间间隔。通常为控制方便, 读周期和写周期时间相等。

18

3.3 DRAM存储器

19

3.3 DRAM存储器

四、 刷新周期 • 刷新周期:DRAM存储位元是基于电容器上的电荷量存储,这个电荷量随着时

3

3.1.2 存储器分级结构

2、分级结构 • 高速缓冲存储器简称cache,它

是计算机系统中的一个高速小 容量半导体存储器。 • 主存储器简称主存,是计算机 系统的主要存储器,用来存放 计算机运行期间的大量程序和 数据。 • 外存储器简称外存,它是大容 量辅助存储器。

4

3.1.2 存储器分级结构

d=设计要求的存储器容量/选择芯片存储器容量 [例2] 利用1M×4位的SRAM芯片,设计一个存储容量 为1M×8位的SRAM存储器。 解:所需芯片数量=(1M×8)/(1M×4)=2片

21

3.3 DRAM存储器

2、字存储容量扩展 • 给定的芯片存储容量较小(字数少),不满足设计要

求的总存储容量,此时需要用多片给定芯片来扩展字 数。三组信号组中给定芯片的地址总线和数据总线公 用,控制总线中R/W公用,使能端EN不能公用,它由 地址总线的高位段译码来决定片选信号。所需芯片数 仍由(d=设计要求的存储器容量/选择芯片存储器容 量) [例3]利用1M×8位的DRAM芯片设计2M×8位的DRAM存储 器 解:所需芯片数d=(2M×8)/(1M×8)=2(片)

(2)增加了刷新计数器和相应的控制电路。DRAM读出后必须刷 新,而未读写的存储元也要定期刷新,而且要按行刷新,所以 刷新计数器的长度等于行地址锁存器。刷新操作与读/写操作是 交替进行的,所以通过2选1多路开关来提供刷新行地址或正常 读/写的行地址。

16

3.3 DRAM存储器

17

3.3 DRAM存储器

26

27

3.3 DRAM存储器

[例4] CDRAM 一片CDRAM的容量为1M×4位,8片这样的芯片可组成1M×32位4MB的

28

3.3 DRAM存储器

七、DRAM主存读/写的正确性校验 DRAM通常用做主存储器,其读写操作的正确性与可靠性至关重要。为此除 了正常的数据位宽度,还增加了附加位,用于读/写操作正确性校验。增加的 附加位也要同数据位一起写入DRAM中保存。其原理如图所示。

15

3.3 DRAM存储器

二、DRAM芯片的逻辑结构 下面我们通过一个例子来看一下动态存储器的逻辑结构如图。 • 图3.7(a)示出1M×4位DRAM芯片的管脚图,其中有两个电源

脚、两个地线脚,为了对称,还有一个空脚(NC)。 • 图3.7(b)是该芯片的逻辑结构图。与SRAM不同的是:

(1)增加了行地址锁存器和列地址锁存器。由于DRAM存储器 容量很大,地址线宽度相应要增加,这势必增加芯片地址线 的管脚数目。为避免这种情况,采取的办法是分时传送地址 码。若地址总线宽度为10位,先传送地址码A0~A9,由行 选通信号RAS打入到行地址锁存器;然后传送地址码A10~ A19,由列选通信号CRS打入到列地址锁存器。芯片内部两 部分合起来,地址线宽度达20位,存储容量为1M×4位。

写入时序中的错误,并画出正确的写入时序图。

解:点击上图

13

3.3 DRAM存储器

一、DRAM存储位元的记忆原理 SRAM存储器的存储位元是一个触发器,它具有两个稳定的状态。而

DRAM存储器的存储位元是由一个MOS晶体管和电容器组成的记忆电路,如图 3.6所示。

14

3.3 DRAM存储器

2储冲器打入元为于给存、4位冲关读高打上线冲送5后由坏存此刷出D器M注输的和不1开存则的现充表电电储位器关开数位高是电储、 、OO图、30此和闭打D元线M容M电0元器闭放)开所上器到=存于性储时新缓送意出。写会U元关闭(据线,位容了、到1图图SI关储是电满存容荷了—OON(T时刷,开位为上,管M/D(读和,打。存,储读位输缓冲到,缓这操同aMc。闭,RD上打线器1读=图存=SS((O))—cdO使的由荷电储器时01/管管输新输,线高的表表0写I出刷输开行储通位出元入冲器位输冲是作时中)NUW)此、输,开上充O出经(储送S表。表b=T,和出缓入输上,电示示到管当新出(选的过元,中缓器线入器因是发1/读为用信电量荷了放,S),时刷入而的电M1读放刷位到。示即表示管送于位缓冲缓入;打荷存写电,缓缓线输重必原冲打上缓总为互生R1出低O电输新缓行高,放大新元存输送从/D,息容来时电代1示(S到是线Wc冲器冲数行开通储1容电冲冲为出写须存器开,冲是读斥。1O)做,管)出缓冲选电表打器缓。到储入到存是写容读为U存而器体,没表1电放器关器据选过了上容器器高缓恢的关,再器互操的1,,缓冲器线平示开发冲T存缓位。储破为或当出储。器,复闭输经与锁作,/1输所上代有存,。10,