X-FAB公布首款0.35微米100V高压纯晶圆代工厂技术

华为终端PCBA制造标准V

DKBA 华为技术有限公司技术规范DKBA 6295-2013.08 终端PCBA制造标准2013年8月15日发布2013年8月30日实施华为技术有限公司Huawei Technologies Co., Ltd.修订声明Revision declaration本规范拟制与解释部门:终端研发管理部产品工程与验证部本规范的相关系列规范或文件:《终端工艺材料选用规范(EMS版)》、《XXX单板工艺特殊说明文件》、《终端产品手工焊接工艺规范》相关国际规范或文件一致性:替代或作废的其它规范或文件:目录Table of Contents1生产与存储环境及工艺辅料选择通用要求 (11)1.1概述 (11)1.2PCBA工艺辅料清单及辅料变更申请管理要求 (11)1.3物料规格及存储使用通用要求 (13)1.3.1通用物料存储及使用要求 (13)1.3.2PCB存储及使用要求 (13)1.3.3锡膏规格及存储使用要求 (14)1.3.4焊锡丝规格及存储使用要求 (14)1415151515161616 2171718181819191920 32121212122222222223.4.1印锡偏位规格要求 (22)3.4.2锡量规格要求 (22)3.5过程报警管制要求 (23)4贴片工序工艺要求 (24)4.1贴片工序通用要求 (24)4.2贴片机设备能力要求 (24)4.2.1贴片机设备处理能力 (24)4.2.2贴片机基准点识别能力 (24)4.3吸嘴规格要求 (25)4.3.1吸嘴与器件对应关系 (25)4.3.2吸嘴材质与贴片器件封装体材质对应关系 (25)4.3.3吸嘴吸取方式 (26)4.4F EEDERS规格要求 (26)4.4.1Feeders与Tray的使用场景定义 (26)4.4.2Feeders宽度与可选元器件尺寸对应关系 (26)4.5贴片工艺过程要求 (26)4.5.1设备保养点检要求 (26)4.5.2作业要求 (26)4.5.3编程要求 (27)5DIPPING FLUX规范和操作要求 (28)5.1D IPPING S TATION设备能力要求 (28)5.2D IPPING S TATION厚度测量要求 (28)5.3D IPPING F LUX工艺操作要求 (28)6AOI工序规范 (30)6.1AOI工序通用要求 (30)303131313232323333333334343536363637373737373939 10.2U NDERFILL胶水使用要求 (39)10.3U NDERFILL工序设备能力要求 (40)10.3.1点胶设备 (40)10.3.2固化设备 (41)10.4U NDERFILL工序操作要求 (41)10.5U NDERFILL工序测温板要求 (42)11插件工艺规范和操作要求 (43)11.1插件剪角要求 (43)11.2插件引脚成型要求 (43)11.3手工插件要求 (43)12波峰焊工艺规范和操作要求 (45)12.1波峰焊辅料存储及使用要求 (45)12.1.1波峰焊锡条使用要求 (45)12.1.2SAC305无铅焊料槽中焊料的更换与锡的添加 (45)12.1.3SACx0807无铅焊料槽中焊料的更换与锡的添加 (46)12.1.4波峰焊助焊剂存储和使用要求 (46)12.2波峰焊设备能力要求 (47)12.3波峰焊测温板要求 (47)12.4波峰焊曲线定义和要求 (47)13手工焊工艺规范和操作要求 (49)13.1手工焊工艺辅料使用要求 (49)13.1.1手工焊锡丝使用要求 (49)13.1.2手工焊清洗剂存储及使用要求 (49)13.2工具设备要求 (49)50515151515353535455555555555555555656565656575716.3.4带散热器的电压调整器安装 (57)17PCBA焊点检验要求 (58)17.1PCBA焊点外观目检要求 (58)17.2PCBA焊点检验标准 (58)17.3对位丝印判定规则: (60)表目录List of Tables表1 华为终端SMT工序PCBA辅料清单 (11)表2 华为终端波峰焊工序PCBA辅料清单 (12)表3 PCB有效存储期限 (14)表4 生产过程停留时间规定 (16)表5 锡膏印刷机设备能力要求表 (17)表6 PCB洗板要求 (20)21222223242425252628283031343437404041表26 波峰焊插件元器件出脚长度和引脚长度要求 (43)表27 SAC305无铅焊料槽中杂质控制 (45)表28 SACX0807无铅焊料槽中杂质控制 (46)表29 华为终端产品无铅波峰焊曲线要求 (47)表30 PCBA焊点外观目检放大倍率与焊盘宽度对应关系表 (58)图目录List of Figures图1 钢网张力测试位置示意图 (19)图2 可吸附面积示意图 (25)图3 DIPPING FLUX深度示意图 (29)图4 热电偶选择位置示意图 (34)图5 华为终端典型无铅回流曲线示意图 (34)图6 轨道平行度偏差测试治具/仪表示意图(推荐) (35)图7 UNDERFILL胶水回温操作示意图 (39)图8 针头颜色示意图 (40)图9 UNDERFILL回流炉固化曲线示意图 (41)图10 常规点胶路径示意图 (41)4142434348555556565757575757错误!未找到引用源。

Fab职位讲解

客户工程师(CE)理工科的毕业生选择范围比较广:计算机、信息类的毕业生可以选择作IT,在Fab厂能够学到一流的CIM技术,工程类的毕业生做设备(EE)的居多,一般而言,做设备不是长久之计。

可以选择做几年设备之后转制程,或者去做厂商(vendor),钱会比较多。

当然,也有少数人一直做设备也发展得不错。

比较不建议去做厂务。

材料、物理类的毕业生做制程(PE)的比较多,如果遇到老板不错的话,制程倒是可以常做的,挺两年,下面有了小弟小妹就不用常常进Fab了。

如果做的不爽,可以转PIE或者TD,或者厂商也可以,这个钱也比较多。

电子类的毕业生选择做制程整合,也就是Integration(PIE)得比较多,这个是在Fab里主导的部门,但如果一开始没有经验的话,容易被PE忽悠。

所以如果没有经验就去做PIE的话,一定要跟着一个有经验的PIE,不要管他是不是学历比你低。

所有硕士或者以上的毕业生,尽量申请TD的职位,TD的职位比较少做杂七杂八的事情。

但是在工作中需要发挥主动性,不然会学不到东西,也容易被PIE之类的人骂。

将来有兴趣去做封装、测试的人可以选择去做产品工程师(PDE)。

有兴趣向Design转型的人可以选择去做PIE或者PDE。

喜欢和客户打交道的人可以选择去做客户工程师CE,这个位置要和PIE搞好关系,他们的Support是关键。

有虐待别人倾向,喜欢看着他人无助神情的人可以考虑去做QE。

QE的弟兄把PIE/PE/EE/TD/PDE之类的放挺简直太容易了。

下面分部门简单介绍一下Fab的工种Fab中PIE要略微比PE和EE好一些,相对进fab的机会要少。

PIE主要的工作有很多,但总而言之是和产品密切相关的。

SMIC上海厂有DRAM和Logic两种截然不同的产品,相应的PIE职责也有区别。

Memory PIE(基本都在一厂)通常是分段管理,一般是有人负责Isolation(FOX/STI),有人负责Capacitance,有人负责Transistor,有人负责后段Interconnect。

半导体FAB知识100问

半导体FAB知识100问影响工厂成本的主要因素有哪些?答:Direct Material 直接材料,例如:蕊片 Indirect Material间接材料,例如气体… Labor人力 Fixed Manufacturing机器折旧,维修,研究费用……等 ProducTIon Support其它相关单位所花费的费用在FAB内,间接物料指哪些?答:Gas 气体 Chemical 酸,碱化学液 PHOTO Chemical 光阻,显影液 Slurry 研磨液 Target 靶材 Quartz 石英材料 Pad & Disk 研磨垫 Container 晶舟盒(用来放蕊片) Control Wafer 控片 Test Wafe r测试,实验用的蕊片什幺是变动成本(Variable Cost)?答:成本随生产量之增减而增减.例如:直接材料,间接材料什幺是固定成本(Fixed Cost)?答:此种成本与产量无关,而与每一期间保持一固定数额.例如:设备租金,房屋折旧及檵器折旧Yield(良率)会影响成本吗?如何影响?答:Fab yield=若无报废产生,投入完全等于产出,则成本耗费最小CP Yield:CP Yield 指测试一片芯片上所得到的有效的IC数目。

当产出芯片上的有效IC数目越多,即表示用相同制造时间所得到的效益愈大.生产周期(Cycle TIme)对成本(Cost)的影响是什幺?答:生产周期愈短,则工厂制造成本愈低。

正面效益如下:(1)积存在生产线上的在制品愈少(2)生产材料积存愈少(3)节省管理成本(4)产品交期短,赢得客户信赖,建立公司信誉FAC根据工艺需求排气分几个系统?答:分为一般排气(General)、酸性排气(Scrubbers)、碱性排气(Ammonia)和有机排气(Solvent)四个系统。

高架地板分有孔和无孔作用?答:使循环空气能流通,不起尘,保证洁净房内的洁净度;防静电;便于HOOK-UP。

Fab职位

Fab职位客户工程师(CE)理工科的毕业生选择范围比较广:计算机、信息类的毕业生可以选择作IT,在Fab厂能够学到一流的CIM技术,工程类的毕业生做设备(EE)的居多,一般而言,做设备不是长久之计。

可以选择做几年设备之后转制程,或者去做厂商(vendor),钱会比较多。

当然,也有少数人一直做设备也发展得不错。

比较不建议去做厂务。

材料、物理类的毕业生做制程(PE)的比较多,如果遇到老板不错的话,制程倒是可以常做的,挺两年,下面有了小弟小妹就不用常常进Fab了。

如果做的不爽,可以转PIE或者TD,或者厂商也可以,这个钱也比较多。

电子类的毕业生选择做制程整合,也就是Integration(PIE)得比较多,这个是在Fab里主导的部门,但如果一开始没有经验的话,容易被PE忽悠。

所以如果没有经验就去做PIE的话,一定要跟着一个有经验的PIE,不要管他是不是学历比你低。

所有硕士或者以上的毕业生,尽量申请TD的职位,TD的职位比较少做杂七杂八的事情。

但是在工作中需要发挥主动性,不然会学不到东西,也容易被PIE之类的人骂。

将来有兴趣去做封装、测试的人可以选择去做产品工程师(PDE)。

有兴趣向Design转型的人可以选择去做PIE或者PDE。

喜欢和客户打交道的人可以选择去做客户工程师CE,这个位置要和PIE搞好关系,他们的Support是关键。

有虐待别人倾向,喜欢看着他人无助神情的人可以考虑去做QE。

QE的弟兄把PIE/PE/EE/TD/PDE之类的放挺简直太容易了。

下面分部门简单介绍一下Fab的工种Fab中PIE要略微比PE和EE好一些,相对进fab的机会要少。

PIE主要的工作有很多,但总而言之是和产品密切相关的。

SMIC 上海厂有DRAM和Logic两种截然不同的产品,相应的PIE职责也有区别。

Memory PIE(基本都在一厂)通常是分段管理,一般是有人负责Isolation(FOX/STI),有人负责Capacitance,有人负责Transistor,有人负责后段Interconnect。

fab专业术语

fab专业术语1 Active Area 主动区(工作区)主动晶体管(ACTIVE TRANSISTOR)被制造的区域即所谓的主动区(ACTIVE AREA)。

在标准之MOS制造过程中ACTIVE AREA是由一层氮化硅光罩即等接氮化硅蚀刻之后的局部场区氧化所形成的,而由于利用到局部场氧化之步骤,所以ACTIVE AREA会受到鸟嘴(BIRD’S BEAK)之影响而比原先之氮化硅光罩所定义的区域来的小,以长0.6UM之场区氧化而言,大概会有0.5UM之BIRD’S BEAK存在,也就是说ACTIVE AREA比原在之氮化硅光罩所定义的区域小0.5UM。

2 ACETONE 丙酮 1. 丙酮是有机溶剂的一种,分子式为CH3COCH3。

2. 性质为无色,具刺激性及薄荷臭味之液体。

3. 在FAB内之用途,主要在于黄光室内正光阻之清洗、擦拭。

4. 对神经中枢具中度麻醉性,对皮肤黏膜具轻微毒性,长期接触会引起皮肤炎,吸入过量之丙酮蒸汽会刺激鼻、眼结膜及咽喉黏膜,甚至引起头痛、恶心、呕吐、目眩、意识不明等。

5. 允许浓度1000PPM。

3 ADI 显影后检查 1.定义:After Developing Inspection 之缩写2.目的:检查黄光室制程;光阻覆盖→对准→曝光→显影。

发现缺点后,如覆盖不良、显影不良…等即予修改,以维护产品良率、品质。

3.方法:利用目检、显微镜为之。

4 AEI 蚀刻后检查 1. 定义:AEI即After Etching Inspection,在蚀刻制程光阻去除前及光阻去除后,分别对产品实施全检或抽样检查。

2.目的:2-1提高产品良率,避免不良品外流。

2-2达到品质的一致性和制程之重复性。

2-3显示制程能力之指针2-4阻止异常扩大,节省成本3.通常AEI检查出来之不良品,非必要时很少作修改,因为重去氧化层或重长氧化层可能造成组件特性改变可靠性变差、缺点密度增加,生产成本增高,以及良率降低之缺点。

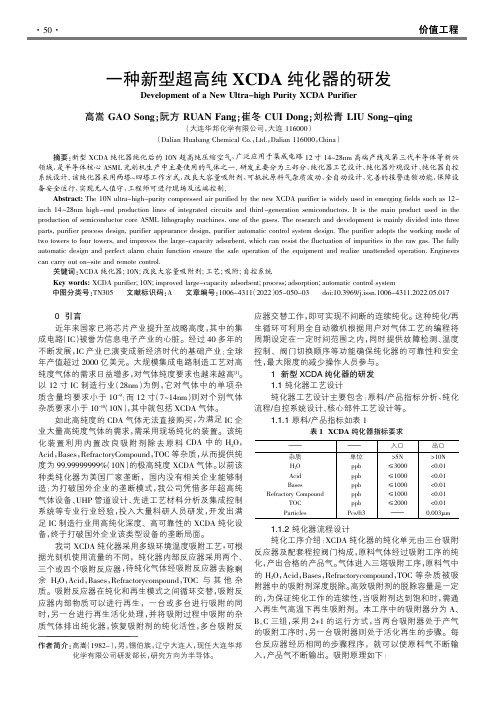

一种新型超高纯XCDA纯化器的研发

价值工程0引言近年来国家已将芯片产业提升至战略高度,其中的集成电路(IC )被誉为信息电子产业的心脏。

经过40多年的不断发展,IC 产业已演变成新经济时代的基础产业;全球年产值超过2000亿美元。

大规模集成电路制造工艺对高纯度气体的需求日益增多,对气体纯度要求也越来越高[1]。

以12寸IC 制造行业(28nm )为例,它对气体中的单项杂质含量均要求小于10-9;而12寸(7~14nm )则对个别气体杂质要求小于10-10(10N ),其中就包括XCDA 气体。

如此高纯度的CDA 气体无法直接购买,为满足IC 企业大量高纯度气体的需求,需采用现场纯化的装置。

该纯化装置利用内置改良吸附剂除去原料CDA 中的H 2O ,Acid ,Bases ,RefractoryCompound ,TOC 等杂质,从而提供纯度为99.99999999%(10N )的极高纯度XCDA 气体。

以前该种类纯化器为美国厂家垄断,国内没有相关企业能够制造;为打破国外企业的垄断模式,我公司凭借多年超高纯气体设备、UHP 管道设计、先进工艺材料分析及集成控制系统等专业行业经验,投入大量科研人员研发,开发出满足IC 制造行业用高纯化深度、高可靠性的XCDA 纯化设备,终于打破国外企业该类型设备的垄断局面。

我司XCDA 纯化器采用多级环境温度吸附工艺,可根据光刻机使用流量的不同,纯化器内部反应器采用两个、三个或四个吸附反应器,待纯化气体经吸附反应器去除剩余H 2O ,Acid ,Bases ,Refractorycompound ,TOC 与其他杂质。

吸附反应器在纯化和再生模式之间循环交替,吸附反应器内部物质可以进行再生,一台或多台进行吸附的同时,另一台进行再生活化处理,并将吸附过程中吸附的杂质气体排出纯化器,恢复吸附剂的纯化活性,多台吸附反应器交替工作,即可实现不间断的连续纯化。

这种纯化/再生循环可利用全自动微机根据用户对气体工艺的编程将周期设定在一定时间范围之内,同时提供故障检测、温度控制、阀门切换顺序等功能确保纯化器的可靠性和安全性,最大限度的减少操作人员参与。

半导体FAB里基本的常识简介-精华版

1.晶圆制造厂非常昂贵的原因之一,是需要一个无尘室,为何需要无尘室答:由于微小的粒子就能引起电子组件与电路的缺陷2.何谓半导体?答:半导体材料的电传特性介于良导体如金属(铜、铝,以及钨等)和绝缘和橡胶、塑料与干木头之间。

最常用的半导体材料是硅及锗。

半导体最重要的性质之一就是能够藉由一种叫做掺杂的步骤刻意加入某种杂质并应用电场来控制其之导电性。

3.常用的半导体材料为何?答:硅(Si)、锗(Ge)和砷化镓(AsGa)4.何谓VLSI?答:VLSI(Very Large Scale Integration)超大规模集成电路5.在半导体工业中,作为绝缘层材料通常称什么?答:介电质(Dielectric).6.薄膜区机台主要的功能为何?答:沉积介电质层及金属层7.何谓CVD(Chemical Vapor Dep.)答:CVD是一种利用气态的化学源材料在晶圆表面产生化学沉积的制程8.CVD分那几种?答:PE-CVD(电浆增强型)及Thermal-CVD(热耦式)9.为什么要用铝铜(Al-Cu)合金作导线?答:良好的导体仅次于铜10.介电材料的作用为何?答:做为金属层之间的隔离11.何谓PMD(Pre-Metal Dielectric)答:称为金属沉积前的介电质层,其界于多晶硅与第一个金属层的介电质12.何谓IMD(Inter-Metal Dielectric)答:金属层间介电质层。

13.何谓USG?答:未掺杂的硅玻璃(Undoped Silicate Glass)14.何谓FSG?答:掺杂氟的硅玻璃(Fluorinated Silicate Glass)15.何谓BPSG?答:掺杂硼磷的硅玻璃(Boro phospho silicate glass)16.何谓TEOS?答:Tetra-ethoxy-silane四乙氧基硅烷, 正硅酸四乙酯, 用途为沉积二氧化硅17.TEOS在常温时是以何种形态存在?答:液体18.二氧化硅其K值为3.9表示何义答:表示二氧化硅的介电质常数为真空的3.9倍19.氟在CVD的工艺上,有何应用答:作为清洁反应室(Chamber)用之化学气体20.简述Endpoint detector之作用原理答:clean制程时,利用生成物或反应物浓度的变化,因其特定波长光线被detector 侦测到强度变强或变弱,当超过某一设定强度时,即定义制程结束而该点为endpoint.21.机台使用的管件材料主要有那些?答:有不锈钢制(Stainless Steal),黄铜制(Brass),塑胶制(PVC),特氟隆制(Teflon)四种. 22.机器维修时要放置停机维修告示牌目的为何?答:告知所有的人勿操作机台,避免危险23.机台维修至少两人配合,有何目的?答:帮忙拆卸重物,并随时警戒可能的意外发生24.更换过任何气体管路上的零件之后,一定要做何动作?答:用氦气测漏机来做测漏.25.维修尚未降至室温之反应室(Chamber),应配带何种手套答:石棉材质之防热手套并宜在80摄式度下始可动作26.何为真空(Vacuum)?半导体业常用真空单位是什么?答:半导体业通常用Torr作为真空的压力单位,一大气压相当760T orr,低于760Torr压力的环境称为真空.27.真空Pump的作用?答:降低反应室(Chamber)内的气体密度和压力28.何谓内部连锁(Interlock)答:机台上interlock有些属于保护操作人员的安全,有些属于水电气等规格讯号,用以保护机台.29.机台设定许多interlock有何作用?答:机台上interlock主要避免人员操作错误及防止不相关人员动作.30.Wafer Scrubber的功能为何?答:移除芯片表面的污染粒子,Scrubber(Wafer clean)机台是水清洗wafer表面,去除wafer表面外来的微尘颗粒(particle).31.何谓蚀刻(Etch)?答:将形成在晶圆表面上的薄膜全部,或特定处所去除至必要厚度的制程。

浅析高性能封装技术的发展

摘要:高性能计算、人工智能和 5G 移动通信等高性能需求的出现驱使封装技术向更高密度集成、更高速、低延时和更低能耗方向发展。

简要地介绍了半导体封测企业、晶圆代工厂和 IDM 在高性能封装领域的发展现状,分析了国内企业在此领域的布局和发展状况,并结合国家政策和国际环境变化,展望了未来国内封测企业在该领域的发展方向。

0 引言1965 年 4 月,Intel 创始人之一戈登·摩尔(Gordon Moore)在《电子学》杂志上刊载《让集成电路填满更多的组件》,文章中预言:当价格不变时,半导体芯片上集成的元器件数目(如晶体管和电阻数量)约每隔 18~24 个月增加 1 倍,性能提升 1 倍。

这个著名的摩尔定律,在过去的几十年间一直推动着半导体技术的发展。

为满足该定律的要求,晶圆代工厂不断地缩小晶体管栅极特征尺寸。

直到20世纪90 年代,该理论开始遇到经济学和物理学上的双重阻碍。

相比于技术节点 90 nm,3 nm 的投资成本增加了 35~40 倍,仅英特尔(Intel)、三星(Samsung)和台积电(TSMC)3 家企业有能力跟随,可以继续在该赛道上竞争。

与此同时,科技浪潮向高性能计算、人工智能、深度学习和 5G 通信等领域快速地发展,其愈加依赖超高性能的高速芯片。

除芯片自身往更高技术节点推进外,高性能封装技术也成为主要的解决方案之一。

高性能封装作为一种前沿的封装技术,其主要特点为I/O的高密度(≥16/mm 2 )和细间距(≤130 μm)其典型的代表为高速专用集成电路(application specific integrated circuit ,ASIC )处理芯片和大约4000 个端口的高带宽存储器(high bandwidth memory,HBM)的超高密度连接,该异构芯片集成封装技术将整体性能推向极致。

据 Yole development预测,从 2019~2025年,高性能封装的市场营收将由8 亿美元增至 43 亿美元,年平均复合增长率约为31%。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

X-FAB 公布首款 0.35 微米 100V 高压纯晶圆代工厂技术

X-FAB Silicon Foundries,业界领先的模拟/混合信号晶圆厂及超越摩

尔定律技术的专家,今天公布了业界首款 100V 高压 0.35 微米晶圆厂工艺。它

能用于电池管理,提供新类型的可靠及高性能电池监控与保护系统。它也非常适

合用于功率管理设备,以及用于使用压电驱动器的超声波成像和喷墨打印机的

喷头。此外,X-FAB 加入了新兴改良式 N 类与 P 类双扩散金属氧化物半导体

(DMOS)晶体管,对于达到 100V 的多运作电压,导通电阻可降低 45%,晶片的

占位能够降低 40%,从而降低了晶粒的成本。X-FAB 将于 7 月 27 日至 28 日向

全球提供一次免费的网络讲座,探讨这些新功能,网络讲座的议题是将业界首款

0.35 微米 100V 纯晶圆代工厂工艺应用于高压装置 。

X-FAB 首席技术官 Jens Kosch 说:随著可再生能源越来越流行,混合动

力与电动车、光电池与风力涡轮机等都需要安全高效的能源存储管理方案。當

客户使用 X-FAB 最新的专业高压工艺時,便能够应对这些问题,以及用较低的成

本应对其他一些潜力巨大的新兴设备。例如我们发现锂电池的功率管理解决方

案很受关注,全球的主要汽车制造商都表现出浓厚兴趣。通过 X-FAB 的最新

HV 工艺,他们就能实现更安全、更高性能的电池监控与保护系统。

各功能的平均成本更低

X-FAB 最新改良型 N 类与 P 类 DMOS 晶体管门氧化物厚度为 14 纳米或

40 纳米,客户根据其设备的要求有 5V 或 12V 驱动能力可选,操作电压为

55V、75V 和 100V。通过大幅降低导通电阻,将 EEPROM 功能集成到基线工

艺,进行修整和程序存储,并使用一个厚金属层作为第三个金属层,X-FAB 已

经大大降低了各功能的平均成本。此外,新加入的独立 5V NMOS 与 PMOS 设

备能够操作于 0V 至 100V 之间的电压。其他设备改良包括肖特基(Schottky)二