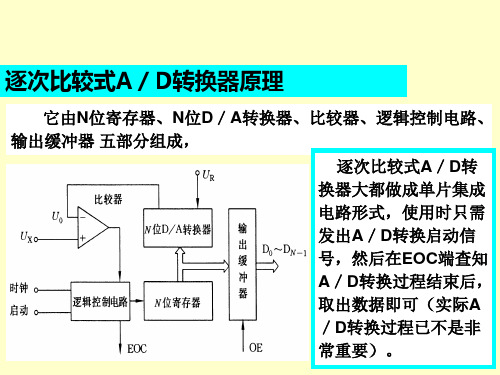

逐次逼近式AD转换原理

逐位逼近式AD转换原理图一个n位AD转换器的模数转换表达式

2、采样定理

采样频率越高,采样信号 y*(t)越接近原信号 y(t),但若采样频率过高,在实时控制系统中将会 占用大量时间在采样上,从而失去了实时控制的机 会。为了使采样信号y*(t)既不失真,又不会因频率 太高而浪费时间,我们可依据香浓采样定理。 香浓定理指出:为了使采样信号y*(t)能完全 复现原信号y(t),采样频率f 至少要为原信号最高 有效频率fmax的2倍,即f 2fmax。实际应用中,常 取f (5-10)fmax。

A/D转换器的转换精度可以用绝对误差和 相对误差来表示。

所谓绝对误差,是指对应于一个给定数字量 A/D转换器的误差,其误差的大小由实际模拟量输 入值和理论值之差来度量。绝对误差包括增益误 差,零点误差和非线性误差等。 相对误差是指绝对误差与满刻度值之比, 一般用百分数来表示,对A/D转换器常用最低有效 值的位数LSB来表示,1LSB = 1/2n 。

①传感器 — 将非电量转换为电信号。

②多路开关(MUX) — 分时切换各路 模拟量与采样/保持器的通路。

系统 ③放大器(IA)— 多为程控放大器, 对模拟信号进行放大。 配置

④采样/保持器(S/H)—保持模拟信号 电压。 ⑤A/D转换器— 将模拟信号转换为数字 信号。 ⑥接口电路 — 将数字信号进行整形电 平调整。

图7-2-2 同时采集

2、分时采集式

每采样一次便进行一次A/D转换并送 入内存后方才对下一采样点采样。具有 通用性、传感器与仪表放大器匹配灵活, 但对MUX的精度要求很高,因为输入的模 拟量往往是μV级的。如图7-2-3所示为 分时采集框图。

图7-2-3 分时采集

3、高速采集式

对多个模拟信号的同时实时测量很 有必要。在各个输入信号以一个公共点 为参考点时,公共点可能与IA和ADC的参 考点处于不同电位而引入干扰电压UN, 从而造成测量误差。如图7-2-4所法为高 速采框图。

AD转换器原理(逐次比较式、双积分式)

T1 T2 Ui Ur

(2.3)

2.3式所明:T2与输入电压的平均值 U i 成正比 设时钟周期为T0,计数器容量为N1,则T1=N1To、T2=N2To,2.3式可改写为

N1 N2 Ui Ur

(2.4)

2.4式所明:N2与输入电压的平均值 U i 成正比( N2 ∝ U i )

N2 ∝ Ui关系的演示

阶段T1结束,积分器输出

1 U 01 RC

t2

t1

U i dt

T1 Ui RC

(2.1)

3.定值积分阶段T2:在 t2 时刻令S1断开的同时,使与Ui极性相反的基准电 压接入积分器。本例设Ui为正值,则令S3闭合,于是积分器开始对基准电压UR 定值积分,积分器输出从U01值向零电平斜变,同时,计数器也重新从零计数, 当积分输出达到零电平时刻(即t3),比较器翻转,此时控制电路令计数器关门, 计数器保留的计数值为N2。定值积分阶段T2结束时,积分器输出电平为零, 则有

2.定时积分阶段----第一次积分,S1接通 特点:定时积分T1固定, UO1∝(正比于) Ui 双积分式A/D转换器原理概述

3.定值积分阶段----第二次积分,S3/S4接通 特点:定值积分(反向),N2∝UO1∝Ui

(假定输入电压增加为2Ui)

①

积分器输出电压还是负向 积分,积分时间T1不变, 但是,斜率将增加一倍。

在T2期间,积分器反向 积分的斜率不变(因UR不 变),但是,返回到零点的 时间T2将增加一倍。 由于T2增加一倍,因而 在T2期间的计数值N2也 将增加一倍。 N2T0

②

③

1.预备阶段Leabharlann ---复零,S4接通双积分式A/D转换器原理概述

STC12C5A60S2中的AD转换

STC12C5A60S2中的AD转换逐次逼近原理AD 里面包含da,当输入电压Vin时,da的最高位是1,即为0.5Vref与输入信号比较,如果输入大于0.5Vref则比较器输出为1,同时da的最高位为1,反之DA最高位则为0,通过8次比较后得到8个01数据即完成ad转换。

现在说下程序中用到stc12单片机两个寄存器ADC_CONTR;主要用来配置ad启动的工作模式;还有个result的寄存器程序中的注意点:配置完ADC_CONTR后要延时4个时钟周期先把程序附上#include "stc12.h"#include "intrins.h"#include "ad.h"uint ad;#define ADC_POWER 0X80 //ADC最高位给adc部分供电,类似于片选#define ADC_START 0X08 //模数转换启动控制位#define ADC_FLAG 0x10 //ad转换需要时间,这个是转换完成标志位#define ADC_SPEEDLL 0X00 //540 clock#define ADC_SPEEDL 0X20 //360 clock#define ADC_SPEEDH 0X40 //180 clock#define ADC_SPEEDHH 0X60 //90 clockuchar ADCresult(uchar aa) //这里的参数是哪个口来ad转换{P1ASF=0X01; //这里的选择和用哪一个P1口作为ad采样ADC_CONTR=ADC_POWER|ADC_SPEEDLL|ADC_START|aa;//ADC_CONTR=0X88|aa;_nop_();_nop_();_nop_();_nop_();//设置ADC_CONTR寄存器后需加4个CPU时钟周期的延时,才能保证值被写入ADC_CONTR寄存器while (!(ADC_CONTR & ADC_FLAG)); //等待ADC_CONTR,这里的ADC_FLAG相当于一个常数,不是寄存器里面的某个位//while(!ADC_FLAG);//ADC_FLAG=0;ADC_CONTR &= ~ADC_FLAG; //Close ADC 将标志位清零等待下次硬件置1ad=(ADC_RES<<2)+ADC_RESL; //打开10位AD采集功能如果用8位AD 屏掉这句把下一句改为Vo=(float)(ADC_RESL)*500/256; 即可//ADC_RES结果寄存器的高2位;ADC_RES结果寄存器的低8位ad=(float)(ad)*5*100/1024; //Return ADCresult(为显示整数,这里将电压值扩大了十倍)//10位AD采集即2的10次方满值为1024 这里用1024表示5伏的电压//那么用采集到的数量值除以1024 在乘以5 得到的值就是采集的电压数值//这里又*100 是为了扩大100倍显示小数位//ADC_RES*(5/256)为采集的电压值然后扩大10倍便于计算return ad;}这里只是个ad.c源文件,这里有几个问题想说一下1.怎么知道是10位还是8位的ad结果;你可以在ADCresult(uchar aa)最前面加一条AUXR1&=0x04;什么意思呢,转换结果的低2位放在ADC_RES,高8位ADC_RESL 中2为什么不用//while(!ADC_FLAG);//ADC_FLAG=0;这两条因为ADC_FLAG相当于常量前面用宏定义而头文件里只有ADC_CONTR的地址映射;但是如果在头文件中用sbit ADC_FLAG=ADC_CONTR^4会出现错误,具体原因还不清楚先说到这吧。

AD芯片ADC0809

0809是逐次逼近式转换芯片,所以在介绍此芯片之前, 先学习逐次逼近式A/D转换原理。

A/D转换芯片与 CPU 接口连接需要注意的问题

(1)启动信号:电平启动和脉冲启动 (2)转换结束与转换数据的读取: — 程序查询方式 — 中断方式 — CPU等待方式 — 固定的迟延程序方式

在中断方式下的A/D转换,程序设计比较简单。在主程 序,只要一条输出指令就可以启动A/D转换。假设A/D转换 器的端口号为PROTAD,则执行指令: O这个指令中AL的内容无关紧 要,执行这个指令主要是为了产生一个写脉冲以启动A/D转 换器。转换结束后,A/D芯片会产生一个转换结束信号 (EOC),此信号产生中断请求,并连接到8259A的IR0, 再通过8259A向CPU发出中断请求,CPU响应后,便转去 执行中断处理程序。该中断处理程序就是完成读取转换结 果,其主要是一条输入指令: IN AL , PORTAD 这条指令在执行时,使三态输出门打开,从而CPU获得数 据。

START: LEA BX, DATA CONV: OUT 37H,AL ; 启动转换 TEST: IN AL ,66H ;输入状态 AND AL ,80H ;检测DONE标记 JZ TEST ;未完成,等待 IN AL, 65H ;输入转换后的数据 MOV [BX], AL ;存入内存 RET ;结束

结果表示逐次逼近型AD转换器原理框图

比较判断

8g<13g 12g<13g

砝码去留

留 留

结果表示

1 1

3

4

8g+4g+2g

8g+4g+1g

14g>13g

13g=13g

去

留

0

1

上页

下页

返回

第 7章

逐次逼近型A/D转换器原理框图

输出数字量

输 出 寄存器 节 拍 脉 冲 发 生 器 模拟信号输入 电 压 比 较 器

CP

逐次逼 近寄存器

D/A

拍 时钟 脉 脉冲 冲 发 生 器

C

C0 C1 C2 C3

0 • C3 • C 0

GND D9 D8 D7 D6 D5

4

5 6 7 8

RF UREF UDD D0 D1 D2 D3 D4

引脚功能 Iout1、Iout2:电流输出端 GND:接地端 D9~D0:数字信号输入端 UDD:电源输入端,5 ~ 10V

UREF:基准电源,–10V ~ +10V

RF:反馈信号输入端

CC7520 外部引脚图

上页

下页

返回

第 7章

CC7520 D/A转换器应用电路

UREF

15

UDD

14 16

D0 D1 D9 ……

13 12

CC7520

4 3

1

2

_ +

+

U0

UREF UO= – 210

(D9 29+D8 28+…+D121+D020)

上页 下页 返回

第 7章

程控三角波/方波发生器

AD转换

模拟电压输入 1LSB

模拟电压输入 1/2LSB

5

3、偏移误差

偏移误差是指输入信号为零时,输出信号不为零的 值,所以有时又称为零值误差。假定ADC没有非线 性误差,则其转换特性曲线各阶梯中点的连线必定 是直线,这条直线与横轴相交点所对应的输入电压 值就是偏移误差。

积分器输出

VIN

时钟

T1 T T2

t

3

三、A/D转换器的主要技术指标 1、分辨率 ADC的分辨率是指使输出数字量变化一个 相邻数码所需输入模拟电压的变化量。常用 二进制的位数表示。例如12位ADC的分辨率 就是12位,或者说分辨率为满刻度FS的 1/2 1 2 。一个10V满刻度的12位ADC能分辨输 入电压变化最小值是10V×1/ 2 1 2 =2.4mV。

ADC_CONTR寄存器

ADC_RES、 ADC_RESL寄存器

ADC中断控制寄存器

ADC典型应用电路

电压基准源

ADC实现按键输入功能

10VIN 20VIN AG

CE STS

-5V~+5V -10V~+10V

23

采用双极性输入方式,可对±5V或±10V的模拟信号

进行转换。当AD574A与80C31单片机配置时,由于 AD574A输出12位数据,所以当单片机读取转换结果 时,应分两次进行:当A0=0时,读取高8位;当A 0=1时,读取低4位。

需三组电源:+5V、VCC(+12V~+15V)、

VEE(-12V~-15V)。由于转换精度高,所 提供电源必须有良好的稳定性,并进行充分滤波, 以防止高频噪声的干扰。 低功耗:典型功耗为390mW。

电气检测技术(新9)AD转换原理

25

1) ai为输入数字量,接CPU的DBUS。可选用 不同的代码,常用的DAC采用二进制码。

2)触发器构成的缓冲寄存器(锁存器),锁存 CPU送来的数据。得到和暂存对应的输出电压。

压分辨率为5V/255≈20mV;10位DAC的分辨率为 5V/1023≈5mV。 位数越多,分辩率越高,转换的精度也越高。

2

测量系统用ADC的主要类型:

1、适用于数字仪器、仪表的ADC; 这类产品多半设计成BCD码输出,转换速度 一般较低(每秒转换十几次)。

2、适用测量系统作模/数接口部件的ADC。 这类产品的转换速度较高,多半以二进制代码 (含双极性代码)输出,常设计成带有三态 输出锁存器,能方便实现与微处理器直接接口。

18

3、应用

产品种类多,转换能力有很大的差异; 有8Bit、10Bit、12Bit、14Bit、16Bit等。 在这些不同转换能力的ADC中,又包括有并行输 出的ADC,以及输出为串行的ADC。 常见的8Bit的有NS公司的ADC0801、DC0802、 ADC0803、ADC0804系列及ADC0808、 ADC0809系列 10Bit有AD公司的AD574,MAXIM公司 MAX1425、MAX1426 12Bit有AD公司的AD7888,MAXIM公司 MAX170、MAX172

有些DAC芯片内无缓冲寄存器,此时须外接, 如74LS273、373等锁存器。

26

3) 模拟开关按输入的数字量接通或断开解码 网相应支路的电流或电压;对它的要求比接通或 断开开关量的电子开关更高。希望动作快;接通 电阻很小,断开电阻很大,且稳定性好。在DAC 中有电压型开关和恒流型电流开关之分。

结果表示逐次逼近型AD转换器原理框图

上页

下页

返回

第 7章

*7.3 模拟开关和采样-保持电路

7.3.1 模拟开关 7.3.2 采样-保持(S/H)电路

上页

下页

返回

第 7章

7.3.1 模拟开关

模拟开关用于传输模拟信号,它主要由控制电 路和开关电路两部分组成。 构成方式:双极型晶体管电路 MOS场效应晶体管

主要介绍由CMOS传输门构成的模拟开关和集 成多路模拟开关。

拍 时钟 脉 脉冲 冲 发 生 器

C

C0 C1 C2 C3

0 • C3 • C 0

2

•

• •

• •

SD J

K RD

Q1 C

1 0

•

比较器

+ +

C1

0 •

•

SD J

C0 0

K RD

Q2 C

•

•

SD J

K RD

Q3 • C

四 1 0 位 D/A 1 0 转 换 1 器

U0

U+ 0 1

1

U+ 0 1

Ui=5.52V J K

+ A2 + UO2

UREF

D9 D8 D7 D0

15 4 5 6

+15V

14 16

DZ

_ +

C

R2 20k R1

CC7520

3

1

2

A1 +

UO1

பைடு நூலகம்……

13

U01

上页

下页

返回

第 7章

7.2 模/数(A/D)转换器

概述 7.2.1 逐次逼近型A/D转换器

*7.2.2 双积分型A/D转换器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、逐次逼近式AD转换器与计数式A/D转换类似,只是数字量由“逐次逼近寄存器SAR”产生。

SAR使用“对分搜索法”产生数字量,以8位数字量为例,SAR首先产生8位数字量的一半,即B,试探模拟量Vi的大小,若Vo>Vi,清除最高位,若Vo<Vi,保留最高位。

在最高位确定后,SAR又以对分搜索法确定次高位,即以低7位的一半y1000000B(y为已确定位) 试探模拟量Vi的大小。

在bit6确定后,SAR以对分搜索法确定bit5位,即以低6位的一半yy100000B(y为已确定位) 试探模拟量的大小。

重复这一过程,直到最低位bit0被确定,转换结束。

转换过程:

(1)首先发出“启动信号”信号S。

当S由高变低时,“逐次逼近寄存器SAR”清0,DAC输出Vo=0,“比较器”输出1。

当S变为高电平时,“控制电路”使SAR开始工作。

(2)SAR首先产生8位数字量的一半,即B,试探模拟量的Vi大小,若Vo>Vi,“控制电路”清除最高位,若Vo<Vi,保留最高位。

(3)在最高位确定后,SAR又以对分搜索法确定次高位,即以低7位的一半y1000000B(y为已确定位) 试探模拟量Vi的大小。

在bit6确定后,SAR以对分搜索法确定bit5位,即以低6位的一半yy100000B(y为已确定位) 试探模拟量Vi的大小。

重复这一过程,直到最低位bit0被确定。

(4)在最低位bit0确定后,转换结束,“控制电路”发出“转换结束”信号EOC。

该信号的下降沿把SAR的输出锁存在“缓冲寄存器”里,从而得到数字量输出。

从转换过程可以看出:启动信号为负脉冲有效。

转换结束信号为低电平。

?

?

我觉得,这有点像数学中的二分法,如给一个数a,先用8'b1000000(设为b)与a相比较,如果a大于b,则保留最高位1,即原来的范围变成了0-7'b1111111(第8位已确认)。

之后的过程都是这样,重复执行就可以了。

根据以上理论,举个例子,例如满量程应该是5V,所以,第一次DA输出,输入电压与比较,输入电压大,故而取之间,即最高位保留1。

然后在新的范围内取中间电压,即,依此类推。