ASIC设计 混合信号集成电路设计指南思维导图

合集下载

第7章 ASIC逻辑综合

从上图可以看出,综合是将逻辑电路的寄存器 传输级表现形式转换成为门级网表的表现形式。综 合的输入是寄存器传输级电路描述,综合的输出是 门级网表。寄存器传输级电路描述是对门级网表的 抽象,门级网表是采用实际的逻辑库单元对寄存器 传输级电路的实现。 门级网表主要包含两个部分:第一个部分是实 现逻辑功能的基本逻辑单元及它们之间的连接方式; 第二个部分是这些逻辑单元的时序关系。

asic逻辑综合71综合原理和思想72可综合代码的编写规范73综合步骤74综合的若干问题及解决71综合原理和思想综合简介在集成电路设计领域综合是指设计人员使用高级设计语言对系统逻辑功能的描述在一个包含众多结构功能性能均已知的逻辑元件的逻辑单元库的支持下将其转换成使用这些基本的逻辑单元组成的逻辑网络结构实现

综合策略分为两种:

一种是自上而下(Top-Down), 一种是自下而上(Bottom-Up)。 这两种综合策略适合的目录组织结构分别如下 图所示。

2、 选择和设置逻辑单元库

综合工具利用逻辑单元库中的逻辑器件将 RTL逻辑描述文件进行编译和优化,转换成门级 电路。选择和设置逻辑单元库是综合过程开始的 前提。

文件扩展名

数据类型 设计源代码 扩展名 .v .vhd .edif .con .scr 描述 Veirlog VHDL EDIF 约束条件 脚本文件

综合脚本 报告和日志 设计数据库

.rpt

.log

报告文件

日志文件

.db

Synopsy库文件

在文件的组织过程中,为了对文件进行有效的 控制,简化文件的使用和查找,必须采用一定的文 件目录结构,将文件一一对应放置。文件目录结构 的选择和采用的综合策略有关。

(2)模块划分应注意模块的复用性。可复用的模 块设计可以减轻模块整合和测试的工作量。模块的复 用性设计应注意模块接口的标准化和模块内部的参数 化。 (3)模块的输出信号采用寄存器方式输出。输出 信号采用寄存器方式输出能够使模块综合时输入的信 号延时估计更加容易,也有易于子模块综合出较好的 结果。 (4)将功能上相关联的组合逻辑尽可能放入一个 模块中,在自下而上的综合过程中,综合工具能够很 好地处理模块内部的时序优化问题,而处于模块边缘 的组合逻辑分布在不同的逻辑模块中会导致时序预估 不准确,从而增加了综合的复杂程度。如下图所示。

西交大专用集成电路ASIC课程chap05_Syn

微电子研究所

Chap05 P.10

可综合的 Verilog描述(3)

支持的运算符 (Operator)

位运算: ~, &, |, ^, ~^, ^~ 归约运算: &, |, ^, ~&, ~|, ~^, ^~ 移位: <<, >> 条件运算: ?: 连接运算符: {, }

微电子研究所

Chap05 P.11

微电子研究所

Chap05 P.5

综合在 ASIC设计 流程中的步骤

微电子研究所

Chap05 P.6

可综合风格的 Verilog描述

如果逻辑输出在任何时候都直接由当前输入组合决定,则为 组合逻辑 。 如果逻辑暗示存储则为 时序逻辑 。如果输出在任何给定时刻 不完全由输入的状态决定,则暗示存储。

通常综合输出不会只是一个纯组合或纯时序逻辑。 一定要清楚所写的源代码会产生什么类型输出,并能够反 过来确定为什么所用的综合工具产生这个输出,这是非常重 要的。

for循环、 while 循环、 loop循环 disable 语句

微电子研究所

Chap05 P.12

可综合的 Verilog描述(5)

不支持的 Verilog 语句

defparam 语句 initial repeat delay control event control fork …… join wait deassign force release

可综合的 Verilog描述(4)

支持的 Verilog 行为描述语句

阻塞过程赋值 (blocking procedure assignments) non-blocking procedure assignments begin … end 顺序块 If … else 语句 case/casez/casex 语句 (在item 中允许出现 z和?, 不允许出现 x,casez 和casex 完全一样 )

西安交通大学 专用集成电路ASIC 课件 chap03_ASICLib

西安交通大学微电子学系

Chap03 P.5

晶体管寄生电容(2)

交叠电容: CGSOV、CGDOV和 CGBOV; 栅电容: CGS、CGD和CGB; 结电容: CBD和CBS 由底面结电容、侧墙 电容和沟道边缘侧墙 电容组成。 大部分电容都和栅、 源、漏上加的电压有 关。

西安交通大学微电子学系

Chap03 P.6

目的:synthesis子学系

Chap03 P.19

Library文件格式——综合及STA

描述标准单元特征数据的文本文件,可以由 library compiler编译成二进制格式(db格式和 ddc格式)。 参考:synopsys的帮助文档。 参考:

西安交通大学微电子学系

Chap03 P.10

晶体管寄生电容(7)

西安交通大学微电子学系

Chap03 P.11

输入压摆率对延时的影响

时间测量点,输入变化30%,输出变化70%。

transition_time 1.000e-10 2.000e-10 3.000e-10 4.000e-10 5.000e-10 6.000e-10 1.000e-09 2.000e-09 tdf_in1 9.457e-11 1.210e-10 1.405e-10 1.857e-10 2.014e-10 2.219e-10 3.067e-10 4.803e-10 tdr_in1 1.600e-10 2.044e-10 2.448e-10 2.888e-10 3.296e-10 3.804e-10 5.235e-10 9.332e-10 tdf_in2 8.640e-11 1.228e-10 1.483e-10 1.727e-10 1.610e-10 2.310e-10 3.102e-10 5.219e-10 tdr_in2 1.237e-10 1.661e-10 2.242e-10 2.558e-10 2.830e-10 3.258e-10 4.626e-10 8.466e-10

ASIC设计流程PPT学习教案

• 在Primetime中进行静态时序分析。 • 在Design Compiler中进行设计优化。 • 设计的详细布线。 • 从详细布线设计中提取出实际时间延时信息

。 • 将提取出的实际时间延时信息反标注到

Design Compiler或者Primetime中。

第13页/共50页

• 使用Primetime进行版图后的静态时序分析。 • 在 Design Compiler中进行设计优化(如需要)

公司 布局布线工具: Dracula, Diva Cadence 公司 静态时序分析: Prime Time Synopsys 公司 测试: DFT Compile Synopsys 公司

第15页/共50页

3.2 ASIC开发流程步骤详细描述

在实际工作中,不同的设计团队可能拥有 不同的ASIC设计开发流程,但是这些不同的开 发流程只是在对设计流程的各个阶段命名时有 一些细微的差别。总的来说,ASIC设计的必要 步骤是缺一不可的。一个ASIC芯片的设计必须 要有一个团结合作的团队才能够完成。

第1页/共50页

集成电路设计与制造的主要流 程系 框架

统 需 求

设计

掩膜版

单晶、外 延材料

芯片制 造过程

芯片检测 封装 测试

第2页/共50页

3.1 ASIC设计流程介绍

下面我们来介绍ASIC设计的基本流程。 设计过程可分五个阶段: 第一阶段:项目策划 第二阶段:总体设计 第三阶段:详细设计和可测性设计 第四阶段:时序验证与版图设计 第五阶段:加工与完备

第8页/共50页

第五阶段:加工与完备 任务:联系生产加工,准备芯片的样片测试和应用 准备。 流程:工艺设计与生产--芯片测试--芯片应用。 输出:用户使用说明书。

。 • 将提取出的实际时间延时信息反标注到

Design Compiler或者Primetime中。

第13页/共50页

• 使用Primetime进行版图后的静态时序分析。 • 在 Design Compiler中进行设计优化(如需要)

公司 布局布线工具: Dracula, Diva Cadence 公司 静态时序分析: Prime Time Synopsys 公司 测试: DFT Compile Synopsys 公司

第15页/共50页

3.2 ASIC开发流程步骤详细描述

在实际工作中,不同的设计团队可能拥有 不同的ASIC设计开发流程,但是这些不同的开 发流程只是在对设计流程的各个阶段命名时有 一些细微的差别。总的来说,ASIC设计的必要 步骤是缺一不可的。一个ASIC芯片的设计必须 要有一个团结合作的团队才能够完成。

第1页/共50页

集成电路设计与制造的主要流 程系 框架

统 需 求

设计

掩膜版

单晶、外 延材料

芯片制 造过程

芯片检测 封装 测试

第2页/共50页

3.1 ASIC设计流程介绍

下面我们来介绍ASIC设计的基本流程。 设计过程可分五个阶段: 第一阶段:项目策划 第二阶段:总体设计 第三阶段:详细设计和可测性设计 第四阶段:时序验证与版图设计 第五阶段:加工与完备

第8页/共50页

第五阶段:加工与完备 任务:联系生产加工,准备芯片的样片测试和应用 准备。 流程:工艺设计与生产--芯片测试--芯片应用。 输出:用户使用说明书。

第四章 EDA技术与可编程ASIC的设计实现

第四章 EDA技术与可编程ASIC的设计实现

4.1.2 ASIC及其分类

ASIC(Application Specific Integrated Circuits, 专用集成电路)

是相对于标准逻辑、通用存储器、 通用微处理器等电路而言的。 短周期交货的全定制或半定制集成电路。 ASIC 从20世纪 60 年代提出概念,到 20 世纪 80年代后期随着 半导体集成电路工艺技术、支持技术、设计技术和测试评价技 术的发展而得到充分发展。尤以设计专用性、成本低、开发周 芯片体积小和重量轻等各方面的优势, 很快发展起来。 用ASIC 取代中小规模集成电路来组成电子系统或整机已成为热潮,目 前在集成电路市场中的ASIC占有率已达1/3。

艺联合制作出电路。

第四章 EDA技术与可编程ASIC的设计实现 集成电路按功能可分为数字集成电路、 模拟集成电路(线 性集成电路和非线性集成电路)、微波集成电路和专用集成电路

(ASIC)。 所谓的数字集成电路就是传递、 加工、处理数字信

号的集成电路。数字集成电路可分为通用数字集成电路和专用 集成电路。通用数字集成电路是指那些用户众多、使用领域广 泛、 标准型的电路。专用集成电路是指为特定的用户、某种专 门或特别的用途而设计的电路。 具体分类如下:

第四章 EDA技术与可编程ASIC的设计实现

PLD

简 单 的 PLD,如 PLA 、 PROM、复 杂 的 PLD(Complex PLD, P AL、 GAL等 CPLD)

电可擦除的 PLD(EPLD)

现场可编程 门 阵 列 FPGA

图 4-1 可编程逻辑器件分类示意图

第四章 EDA技术与可编程ASIC的设计实现

第四章 EDA技术与可编程ASIC的设计实现 4.2.2 FPGA和CPLD的比较 FPGA和CPLD是半定制芯片的杰出代表。它们兼容了PLD

第2章 ASIC设计基础

1、全定制设计简述

全定制ASIC是利用集成电路的最基本设计 方法(不使用现有库单元),对集成电路中所 有的元器件进行精工细作的设计方法。全定制 设计可以实现最小面积,最佳布线布局、最优 功耗速度积,得到最好的电特性。该方法尤其 适宜于模拟电路,数模混合电路以及对速度、 功耗、管芯面积、其它器件特性(如线性度、 对称性、电流容量、耐压等)有特殊要求的场 合;或者在没有现成元件库的场合。

• 什么是集成电路? 把组成电路的元件、器件以及相互间的 连线放在单个芯片上,整个电路就在这个芯片 上,把这个芯片放到管壳中进行封装,电路与 外部的连接靠引脚完成。 • 什么是集成电路设计? 根据电路功能和性能的要求,在正确选择 系统配臵、电路形式、器件结构、工艺方案和 设计规则的情况下,尽量减小芯片面积,降低 设计成本,缩短设计周期,以保证全局优化, 设计出满足要求的集成电路。

MGA门阵列可以分为: • 通道式门阵列-基本单元行与行之间留有固定 的布线通道,只有互连是定制的。 • 无通道门阵列(门海)-无预留的布线区,在 门阵列掩膜层上面布线。 • 结构式门阵列-结合CBIC和MGA的特点,除了 基本单元阵列外,还有内嵌的定制功能模块。芯片 效率高,价格较低,设计周期短。 由于MGA的门阵基本单元是固定的,不便于实 现存储器之类的电路。在内嵌式门阵列中,留出一 些IC区域专门用于实现特殊功能。利用该内嵌区域 可以设计存储器模块或其它功能电路模块。

表1-1 集成电路不同发展阶段的特征参数主要特征 主要特征 元件数/片 特征线宽 μm 氧化层厚 nm 结深 μm 硅片直径 inch SSI

<102

MSI

102-103

LSI

103-105

VLSI

105-107

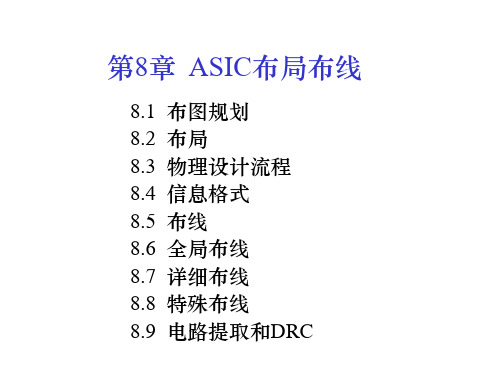

第8章 ASIC布局布线

布图规划紧接着系统划分,是在ASIC上安排电 路模块的第一步。很多因素需要在布图规划时考虑: 最小化模块间的连接长度和信号延迟;安排固定模块 及重新调整可变模块使其占有最小管芯面积;组织模 块间的互连区域;规划电源,时钟和I/O配线。有些 因素可以由CAD工具自动处理,有些仍然需要人为干 预。布局接着布图规划,而且比较自动化。它包括在 可变模块内组织好逻辑单元阵列。优化的判据可以是 最小化互连面积、最小化互连总长度或性能。一共有 两种主要的布局算法;基于最小割或本征值方法。因 为亚微米CMOS工艺的互连延迟比门的延迟更大,所 以互连的规划就显得越来越重要。我们不是在完全结 束综合后再布图规划和布局,而是将综合与布图规划 /布局工具结合起来以达到精确的时序估计。

自动布局布图规划? 布图规划是将电路放置在一枚专用集成电路芯片 上的第一部。其输入文件是一个层次式的网表文件, 来自与前端设计或系统分片的输出。层次式网表的内 容包括: • 功能块之间的互连; • 功能块中逻辑单元的端点。 布图规划设计是将功能块安排在ASIC芯片上, 是ASIC的逻辑表征对应于物理表征。

另一种方法:是全局布线器考虑到已经布好在各个通 道中的互连数目。这样的全局布线是顺序相关的——也就 是说布线是顺序执行的,网络处理的顺序会影响结果。选 代改进或模拟退火算法都可以用在顺序相关和顺序无关算 法的解中。和系统划分以及布局实施过程相同:对已有的 结果逐次改变,随机地一次对一条互连路径进行移动。 和一次处理一个网络的顺序全局布线方法不同,层次 式布线每次处理一层上的所有网络。因为不用同时处理芯 片所有的网络,通过把芯片分层进行划分可以使全局布线 问题更易控制。由于每次只考虑一层,因此使问题变得简 单了。有两种方法可以遍历所有的层次。从整个芯片或最 上层开始向下一层进行,直至逻辑单元.这是自上而下的 方法。自下而上的方法是从最底层开始先对最小的面积进 行布线。

西安交通大学 专用集成电路ASIC 课件 chap07_phyDesign

微电子学系

Chap07 P.15

Placement Problem

Input:

•A set of cells and their complete information (a cell library). •Connectivity information between cells (netlist information).

statistical wire-load models Wirelength in placement

微电子学系

Chap07 P.14

Constraint of Placement

Area Would like to pack all the modules very tightly Wire length (half-perimeter of the net bbox) Minimize the average wire length Would result in tight packing of the modules with high connectivity Overlap Could be prohibited by the moves, or used as penalty Keep the cells from overlapping (moves cells apart) Timing Not a 1-1 correspondent with wire length minimization, but consistent on the average Congestion Measure of routability Would like to move the cells apart