施密特触发器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS 施密特触发器的仿真

实验目的:

①掌握HSPICE 仿真软件的使用;

②掌握CMOS 施密特触发器的原理,绘制CMOS 施密特触发器的VTC ,并求V M+和V M-; 实验原理:

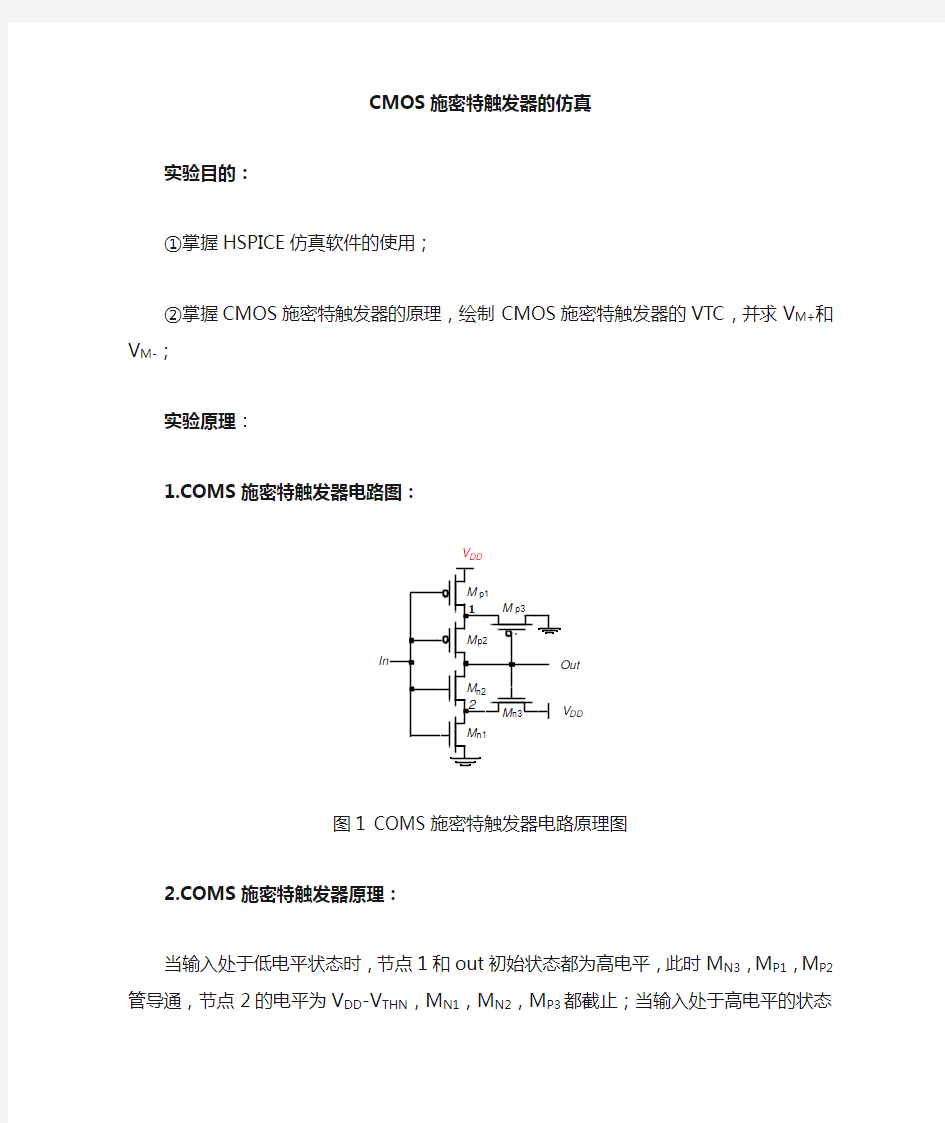

S 施密特触发器电路图:

In V DD

V DD

Out M n1M n2M p2

M p1

M n3M p321

图1 COMS 施密特触发器电路原理图

S 施密特触发器原理:

当输入处于低电平状态时,节点1和out 初始状态都为高电平,此时M N3,M P1,M P2管导通,节点2的电平为V DD -V THN ,M N1,M N2,M P3都截止;当输入处于高电平的状态时,节点2和out 初始状态都为低电平,此时M P3,M N1,M N2管导通,节点1的电平为V THP ,M P1,M P2,M N3都截止。当输入由低电平向高电平转换时,导通的M N3作为上拉网络的一部分,其作用可以等效于增大上拉网络晶体管的W ,所以具有更高的开关阈值;同理,当输入由高电平向低电平转换时,导通的M P3作为下拉网络的一部分,其作用可以等效于增大了下拉网络晶体管的W ,所以具有更低的开关阈值。

实验内容:

实验采用的软件为HSPICE C-2009.09,工艺库文件为MM180_LVT18_V113.LIB (0.18um )。选取的PMOS 管的尺寸为W=0.72um ,L=0.18um ;NMOS 管的尺寸为W=0.36um ,L=0.18um 。

1.理论推导V M+和V M-:

当输入由低电平向高电平转换时,最初只有MN3导通,当输入电压大于MN1的阈值电压以后,MN2导通,此后节点2的电压将随V IN 的升高而逐渐降低,当V IN -V 2大于MN2的阈值电压以后,输出被下拉至低电平,此时的V IN 可以认为是V M-,根据KCL 列出节点2的节点电流方程,我们可以解出V M-的表达式。我们假设MN1和MN3两个管子都工作在饱和区,并且忽

略背栅效应和沟道长度调制效应。

同理可以推到出V M+为:

我们取,,;可以求得V M-=1.25V,V M+=0.55V

2.软件仿真验证:

HSPICE电路网表代码如下:

Schmitt trigger

.lib 'C:\avanti\MM180_LVT18_V113.LIB' TT

mp1 1 in vdd vdd P_LV_18_MM w=0.72um l=0.18um

mp2 out in 1 vdd P_LV_18_MM w=0.72um l=0.18um

mp3 1 out gnd vdd P_LV_18_MM w=0.72um l=0.18um

mn1 2 in gnd gnd N_LV_18_MM w=0.36um l=0.18um

mn2 out in 2 gnd N_LV_18_MM w=0.36um l=0.18um

mn3 2 out vdd gnd N_LV_18_MM w=0.36um l=0.18um

vin in gnd dc

vdd vdd gnd dc 1.8

.dc vin 0 1.8 10m

.dc vin 1.8 0 10m

.end

分析下图的电压传输特性曲线,我们可以得到V M-=1.040V,V M+=0.631V;

图2 CMOS施密特触发器的电压传输特性曲线(VTC)

实验结论:

理论推导过程未考虑背栅效应和沟道长度调制效应,并且对于和

采用了经验估计值,存在较大的误差。实际结果以仿真结果为准。