PCIe总线实现了一种叫做Quality of Service(QoS)的机制

pcie规范

pcie规范PCIe(Peripheral Component Interconnect Express)是一种高速串行总线规范,用于在计算机系统中连接各种外部设备和扩展卡。

PCIe是一种基于总线结构的互联技术,它提供了更高的带宽和更快的数据传输速度,以满足现代计算需求日益增长的需求。

本文将详细介绍PCIe规范,包括其历史、特点、工作原理以及应用领域。

PCIe的历史可以追溯到1992年,当时英特尔、IBM和康柏就开始开发PCI(Peripheral Component Interconnect)总线规范,用于取代传统的ISA和VLB总线。

PCI总线规范在1993年发布,迅速成为标准计算机接口,并在20世纪90年代普及开来。

然而,随着计算机性能的不断提升和多媒体、网络等应用的广泛应用,PCI总线的带宽和性能已经无法满足需求。

为了提供更高的带宽和更快的数据传输速度,PCI-SIG(PCI Special Interest Group)于2004年发布了PCI Express规范,即PCIe 1.0版本。

PCIe采用了全新的串行总线结构,以替代传统的并行总线。

相较于PCI总线,PCIe具有更高的数据传输速度、更低的延迟、更高的带宽和更好的可伸缩性。

PCIe的特点主要体现在以下几个方面:1. 高速传输:PCIe提供了多个版本,每个版本都有不同的数据传输速率。

当前最常见的PCIe 3.0版本,具有每条通道8 Gbps的传输速度,每条通道相当于一个全双工的高速通道。

2. 可伸缩性:PCIe采用点对点连接的拓扑结构,每个设备都有一个独立的通道,与其他设备无冲突。

这种可伸缩性使得PCIe可以支持大量的设备以及更复杂的系统架构。

3. 低延迟:由于PCIe采用了串行传输,相较于并行总线具有更低的延迟,能够更快地处理数据。

4. 热插拔支持:PCIe支持热插拔特性,即可以在计算机运行时插入或拔出设备,而不需要重启计算机。

(完整版)xilinxPCIE2.0接口EP端设计总结,推荐文档

1.PCIE说明PCIE协议定义了多种设备:根复合体(Root Complex),交换器(Switch),端点(Endpoingt),断就(Port),PCIE到PCI/PCI-X的桥(Bridge)等。

根复合体是将CPU和主存储器连接到PCIE 线路结构上的设备,能带包CPI启动PCIE事务和访问主存储器;交换器可以将任务由一个端口路由到另一个端口,在系统中用于多设备的互联,具体的路由方法包括ID路由,地址路由,隐含路由;Endpoint是指一个世纪的设备(请求者或完成者);port是设备与链路的接口;Bridge 则是用来实现PCIE设备与PCI/PCI-X设备之间的连接,实现两种不同协议之间的相互转换。

PCIE核在多种模式中使用包来互换信息。

包是在事务和数据链层中形成来从发送端到接收端的信息传递。

必要的信息被添加到传输的包中。

在接收结束,接收单元的每一层处理接收到的包,提取相关的信息并发送包到下一层。

接收到的包是从他们物理层发送到数据链层和事务层的。

PCIe 规范对于设备的设计采用分层的结构,有事务层、数据链路层和物理层组成,各层有都分为发送和接收两功能块。

PCIe的事务层是协议的最上层,其主要功能是根据应用层提供的信息生成相应的请求包传递给数据链路层,并且处理由数据链路层发来的包,将其转换成应用层能识别的信息,协助数据链路层完成信用管理,实现协议规定的配置事务,IO事务,存储事务和消息事务。

在设备的发送部分,首先根据来自设备核和应用程序的信息,在事务层形成事务层包(TLP),储存在发送缓冲器里,等待推向下层;在数据链路层,在TLP 包上再串接一些附加信息,这些信息是对方接收TLP 包时进行错误检查要用到的;在物理层,对TLP 包进行编码,占用链路中的可用通道,从查封发送器发送出去。

事务层包(TLP),数据链路层包(DLLP),物理层(PLP)产生于各自所在层,最后通过电或光等介质和另一方通讯。

PCIe基本原理

xx

xx

Transaction

Link

xx

PIPE

Logical

Electrical Mechanical

Physical Interface (PIPE)

为什么PCIe的工程设计难度要大得多呢?图4显示了在高速设计方案中这些问题的实例以及标准的FR4 电路板材料对于信号的影响度。此图左侧显示了一个1.25 Gbps数据流和一个5 Gbps数据流的二进制眼 图,并对应于通过26英寸的标准FR4电路板材料进行传输。右侧的对应二进制眼图表明,目的地处的信 号性能出现了衰减。而1.25 Gbps数据流在这种传输路程中保存得非常完好,但5 Gbps眼图的大小和清 晰度均出现了显著的衰减,这是因为低成本FR4基底材料以及互连线材料在大于1 GHz的频率下所发生的 介电损失现象而造成的。

• 端点通常驻留在应用内,用于在系统中将应用连接到PCIe网络。端点具有请求和完成PCIe事务处理的 功能。此系统内的端点数量通常多于其它任何类型的PCIe组件。

• 桥接器用于将PCIe与其它PCI总线标准(如PCI/PCI-X)相连接,适用于那些同时采用了这些体系架构 与PCIe的系统。

PCIe协议规格

转向PCIe主要是为了实现显著增强系统吞吐量、扩容性和灵活性的目标,同时还要降低制造成本,而这 些都是基于总线的传统互连标准所达不到的。PCI Express标准在设计时着眼于未来,并且能够继续演 进,从而为系统提供更大的吞吐量。第一代PCIe规定的吞吐量是每秒2.5千兆比特(Gbps),第二代规 定的吞吐量是5.0 Gbps,而最近公布PCIe 3.0标准已经支持8.0 Gbps的吞吐量。在PCIe标准继续充分利 用最新技术来提供不断加大的吞吐量的同时,采用分层协议也便于PCI向PCIe的演进,并保持了与现有 PCI应用的驱动程序软件兼容性。

什么是计算机网络QoS请解释几种常见的QoS技术

什么是计算机网络QoS请解释几种常见的QoS技术计算机网络的发展与普及使得人们可以更加便捷地进行信息传输和网络通信。

然而,网络连接质量的变化和波动会导致网络性能的不稳定,例如延迟、带宽不足和丢包等问题。

为了解决这些问题,计算机网络引入了QoS(Quality of Service,服务质量)技术,旨在提供更好的用户体验和网络性能。

QoS是指在网络中提供满足用户要求的服务质量的能力。

它通过有效管理网络资源和优化传输策略,以保证不同应用或服务在网络中能够得到适当的带宽、低延迟和可靠的连接。

下面将重点介绍几种常见的QoS技术。

1. IntServ(Integrated Services,综合服务)IntServ是一种基于资源预留的QoS技术。

它使用了传统的电路交换思想,即在通信建立之前,先为特定应用程序分配一定的网络资源。

IntServ适用于对延迟和带宽要求较高的应用,如视频会议和实时音频传输。

然而,IntServ难以适应大规模网络的需求,资源预留的方式在大规模网络中管理起来较为困难。

2. DiffServ(Differentiated Services,差异化服务)DiffServ采用了分层次的QoS策略,即将网络流量按照不同的优先级进行分类处理。

它为网络中的不同流量提供了不同等级的服务质量保证,包括实时流量和非实时流量。

DiffServ将网络流量划分为多个类别,并为每个类别分配不同的优先级,然后根据优先级进行调度和传输。

DiffServ相对于IntServ来说,更适用于大规模网络,能够更好地满足网络的可扩展性需求。

3. MPLS(Multi-Protocol Label Switching,多协议标签交换)MPLS是一种在数据链路层和网络层之间建立路径的技术。

通过引入标签交换的方式,MPLS可以对数据包进行快速转发和路由选择,以提高网络传输效率和降低延迟。

MPLS可以采用基于DiffServ的QoS 策略,为网络中的不同流量提供不同等级的服务质量。

采用Flow Control机制的PCIe总线

采用Flow Control机制的PCIe总线

PCIe总线设计之初,主要是针对于音频和视频传输等这些对时间要求特别敏感的应用的。

为了保证这些特殊应用的数据包能够得到优先发送,PCIe Spec中为每一个包都分配了一个优先级,通过TLP的Header中的3位(即TC,Traffic Class)。

如下图所示:

TC值越大,表示优先级越高,对应的包也就会得到优先发送。

一般来说,支持QoS(Quality of Service)的PCIe总线系统,对于每一个TC值都会有一个独立Virtual Channel(VC)与之对应。

这个Virtual Channel实际上就是一个Buffer,用于缓存数据包。

注:当然也有那些只有一个VC Buffer的,此时不管包的TC值如何,都只能缓存在同一个VC Buffer中,自然也就没有办法保证按优先级传输了。

这样的PCIe设备称之为不支持QoS的PCIe设备。

一个简单的QoS的例子如下图所示:。

PCIE非透明桥应用

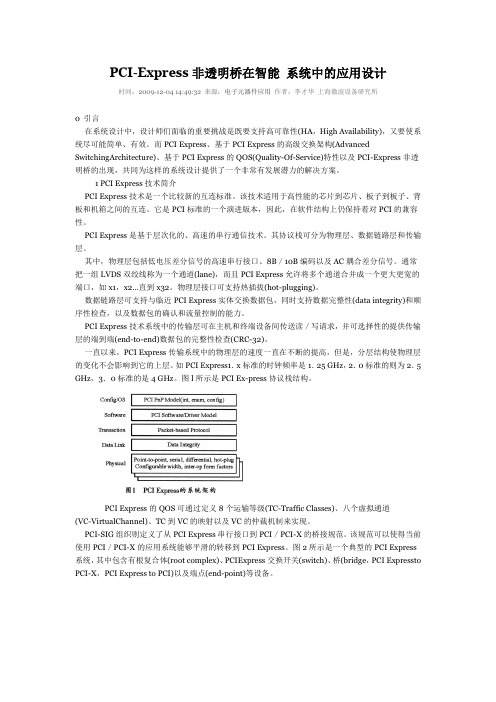

PCI-Express非透明桥在智能系统中的应用设计时间:2009-12-04 14:49:32 来源:电子元器件应用作者:李才华上海微波设备研究所0 引言在系统设计中,设计师们面临的重要挑战是既要支持高可靠性(HA,High Availability),又要使系统尽可能简单、有效。

而PCI Express、基于PCI Express的高级交换架构(Advanced SwitchingArchitecture)、基于PCI Express的QOS(Quality-Of-Service)特性以及PCI-Express非透明桥的出现,共同为这样的系统设计提供了一个非常有发展潜力的解决方案。

1 PCI Express技术简介PCI Express技术是一个比较新的互连标准。

该技术适用于高性能的芯片到芯片、板子到板子、背板和机箱之间的互连。

它是PCI标准的一个演进版本,因此,在软件结构上仍保持着对PCI的兼容性。

PCI Express是基于层次化的、高速的串行通信技术。

其协议栈可分为物理层、数据链路层和传输层。

其中,物理层包括低电压差分信号的高速串行接口、8B/10B编码以及AC耦合差分信号。

通常把一组LVDS双绞线称为一个通道(lane),而且PCI Express允许将多个通道合并成一个更大更宽的端口,如x1,x2…直到x32。

物理层接口可支持热插拔(hot-plugging)。

数据链路层可支持与临近PCI Express实体交换数据包,同时支持数据完整性(data integrity)和顺序性检查,以及数据包的确认和流量控制的能力。

PCI Express技术系统中的传输层可在主机和终端设备间传送读/写请求,并可选择性的提供传输层的端到端(end-to-end)数据包的完整性检查(CRC-32)。

一直以来,PCI Express传输系统中的物理层的速度一直在不断的提高,但是,分层结构使物理层的变化不会影响到它的上层。

PCIe总线基础及FPGA设计实战

PCI Express总线基础及FPGA设计实战1. PCI Express基础PCIe总线是基于PCI总线发展起来的,很多基本概念都来自于PCI总线,有必要在介绍PCIe之前了解PCI总线。

1.1 PCI基础PCI总线作为处理器系统的局部总线,其主要目的是为了连接外部设备,而不是作为处理器系统的系统总线连接Cache和主存储器。

PCI总线作为系统总线的延伸,其设计考虑了许多与处理器相关的内容,孤立的研究PCI总线并不可取,因此需要将PCI作为存储器系统的一个部分来研究。

1.1.1 几个重要概念1)PCI总线空间与处理器空间隔离PCI设备具有独立的地址空间,即PCI总线地址空间,该空间与存储器地址空间通过HOST 主桥隔离。

处理器需要通过HOST主桥才能访问PCI设备,而PCI设备需要通过HOST主桥才能方位主存储器。

要注意区分存储器地址空间和PCI总线地址。

在一个处理器系统中,存储器域、PCI总线域与HOST主桥的关系如下图。

图中的处理器系统由一个CPU、一个DRAM控制器和两个HOST主桥组成。

在这个处理器系统中,包含CPU域、DRAM域、存储器域和PCI总线域地址空间。

其中HOST主桥x和HOST 主桥y分别管理PCI总线x域与PCI总线y域。

CPU访问PCI设备,必须通过HOST主桥进行地址转换,而PCI设备访问存储器设备,也需要HOST主桥进行地址转换。

HOST主桥的一个重要作用就是将存储器访问的存储器地址转换成PCI总线地址。

CPU域地址空间是指CPU所能直接访问的地址空间集合。

DRAM域地址空间是指DRAM控制器所能访问的地址空间集合,又称为主主存储器域。

存储器域是CPU域和DRAM域的集合。

存储器域包括CPU内部的通用寄存器、存储器映射寻址的寄存器、主存储器空间和外部设备空间。

在Intel的x86处理系统中,外部设备空间与PCI总线域地址空间等效。

因为在x86处理器系统中,使用PCI总线同一管理全部外部设备。

pcie总线通信原理

pcie总线通信原理PCIe(Peripheral Component Interconnect Express)是一种高速串行计算机扩展总线标准,被广泛应用于计算机系统中,用于处理器与各种外围设备(如显卡、硬盘、网卡等)之间的通信。

PCIe总线采用点对点链路串行通信的方式,相比较旧的并行总线(如PCI、AGP等),具有更高的带宽、更低的延迟和更小的功耗等优点。

PCIe总线的通信原理主要包括以下几个方面:1. 拓扑结构PCIe总线采用树状拓扑结构,其中根复杂器(Root Complex)作为根节点,与处理器直接连接。

根复杂器通过交换机(Switch)与各个端点(Endpoint)相连,每个端点即代表一个外围设备。

2. 链路层PCIe总线的链路层定义了两个通信实体之间的低级通信协议,包括数据包的封装与解封装、流控、序列化与并行化等。

PCIe链路分为不同的速率等级(Gen1/Gen2/Gen3/Gen4等),速率越高,带宽越大。

3. 事务层事务层定义了设备之间的通信语义,包括读/写操作、消息传递等。

PCIe事务包括Memory、IO、Configuration等多种类型,支持多种通信模式。

4. 电源管理PCIe总线支持多种电源管理机制,如主动和被动省电策略、链路状态管理等,可根据功耗需求动态调节链路的工作状态,提高能效。

5. 热插拔PCIe总线支持热插拔,即在系统运行期间插拔外围设备,无需重启计算机。

这依赖于PCIe的枚举机制、电源控制和错误管理等功能。

6. 虚拟化PCIe支持硬件虚拟化,单个物理设备可划分为多个虚拟设备,供不同的虚拟机访问,提高资源利用效率。

PCIe总线通过点对点串行通信、高速链路、优化的事务层、先进的电源管理和虚拟化等机制,为现代计算机系统提供了高效、灵活、低功耗的外围设备通信途径,推动了计算机硬件的持续发展。

一种支持VC交叉的OTN板卡设计

第8卷第2期2019军3月Vol.8No.2网络新媒体技术Mar.2019•实用技术•一种支持VC交叉的OTN板卡设计冯子悦I毛晓波$潘庆雯I('武汉邮电科学研究院武汉4300742烽火通信科技股份有限公司武汉430073)摘要:随着现代网络技术的不断演进、通信技术的迅速发展,传统的SDH设备因为容量小、集成度低等一系列问题从而面临着退网。

但是对于高价值小颗粒的业务,SDH依然是必然之选。

面对这种现状,本文从硬件设计和软件架构这两方面,介绍了一种相关的融合了VC交叉的支路盘设计方案.该方案能够利用现有OTN设备资源,无需更换线路盘.以做到对现有网络的最小修改'通过测试发现,该板卡在业务满配时能够正常工作,保护倒换时间可达到少于50ms的要求,满足现网业务需求关键词:SDH,OTN,VC交叉An OTN Board Design Supporting VC CrossoverFENG Ziyue',MAO Xiaobo2,PAN Qingwen'(1Wuhan Research Institute of Posts and Telecommunications,Wuhan,430073,China,2Fiberhome Telecommunication Technologies Co.,Ltd.,Wuhan,430073,China)Abstract:With the continuous evolution of modern network technology and the rapid development of communication technology,traditional SDH equipment faces network retreat due to a series of problems such as small capacity and low integration,but for high-value small-granule business,SDH is still the inevitable choice.Faced with this situation,this paper introduces a related tributary disk design that combines VC crossover from the aspects of hardware design and software architecture.This solution can utilize existing OTN e-(juipment resources without replacing the linecard.To achieve minimal modifications to existing networks.The test found that the board can work normally when the service is fully configured,and the protection switching time can reach50ms,accords with the needs of the existing network services.Keywords:SDH,OTN,VC crossovero引言随着信息时代的发展,目前各大运营商的业务平台(数据、交换平台)所需业务颗粒越来越大,整个传输网络有扁平化的趋势,目前单一的同步数字体系(synchronous digital hierarchy,SDH)设备所面临的主要问题是:①SDH设备容量较低,现有的设备基本处于低于10Gbit/s的速率,最大容量也仅为40Gbit/s(STM-256)且使用较少,对光纤资源造成浪费;②占用资源高,设备的集成度较低,占用的机房、设备槽位较多;③现网的大部分业务已经不再使用SDH作为其承载平台,逐渐面临退网⑴。

qos的名词解释

qos的名词解释Quality of Service(服务质量)通常简称为QoS。

它是指网络中数据传输的优先级和保证性能。

在如今信息爆炸的数字时代,网络已经渗透到了我们生活的方方面面。

从电子邮件、社交媒体、在线购物到在线游戏和视频会议,我们对网络的依赖越来越大。

因此,QoS成为了确保网络资源分配公平、高效和可靠的关键概念之一。

首先,QoS的目标是为了提供具有差异化的服务。

举个例子,当你观看高清视频或者进行视频通话时,你很可能不希望画面一直出现卡顿或者延迟。

而当你仅发送简单的文字消息时,网络的传输速度则可以更低一些。

通过对不同类型的数据流进行分类和标记,QoS确保了高优先级的数据包能够更快速地传输、低优先级的数据包则具有较低的延迟。

其次,QoS通过限制、调度和优化网络流量来保证可靠性。

在网络拥塞的情况下,数据包可能会丢失或被延迟。

为了避免这种情况,QoS利用流量控制和拥塞控制机制,确保网络中的流量保持在可接受的范围内。

此外,QoS还可以通过选择最佳路径、合理分配带宽和优先传输重要数据等手段,提高网络的稳定性和可靠性。

QoS也允许网络管理员根据不同用户或应用的需求进行资源管理。

例如,在一个企业网络中,员工可能需要更高的带宽和较低的延迟来进行日常工作。

而在同一网络中,访客的需求则可能不同。

通过为不同用户或应用分配适当的带宽和传输优先级,QoS可以满足不同需求,并确保网络资源的公平共享。

此外,QoS对于支持即时通信和语音服务非常重要。

在语音通话或在线会议中,实时性是最关键的因素之一。

没有人愿意经历到对方声音卡顿或断断续续的情况。

QoS通过优先传输语音数据包和在必要时丢弃较低优先级的数据包,以确保语音通话的质量不受影响。

这在医疗、金融和紧急救援等领域尤为重要,因为在关键时刻,每一秒钟都可能关系到生命的安全。

尽管QoS在提供高质量网络体验方面发挥了重要作用,但它也面临着一些挑战。

首先,网络拓扑的复杂性和规模使得实现QoS变得更加困难。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCIe 总线实现了一种叫做Quality of Service(QoS)

的机制

前面的文章中介绍过,为了保证视频、音频等数据得到优先传输,PCIe

总线实现了一种叫做Quality of Service(QoS)的机制。

QoS 可以满足视频、音频等对Latency 和实时性(Isochronous)要求比较高(一般不可以被打

断)的应用需求。

QoS 主要通过VC(Virtual Channel)和TC(Traffic Class)来实现。

VC 的相关寄存器位于PCIe 配置空间的扩展部分(PCIe Extended Capability Space),如下图所示:

前面的文章中介绍过,每一个VC 都有独立的Buffer,某一个VC Buffer

满了并不会影响其他VC 的使用。

但是只靠VC 并不能实现QoS 中的优先级

的功能,这还需要TC(Traffic Class)的支持。

TC 的值由TLP Header 中的Byte1 的bit[6:4]定义,如下图所示。

显然TC 值的范围为0~7,值越大优先级

越高,默认为0(优先级最低)。

在初始化的时候,PCIe 驱动程序会为每一种

类型的包分配好合适的TC 值(优先级)。

如果PCIe 驱动程序没有找到PCIe Extended Capability Space,则认为该设备只有一个VC,即VC0。

此时再为每一个TLP 分配不同的TC 值,显然是

没有意义的。

因此会默认采用TC0/VC0 组合,即不支持QoS 功能。

换一句。