第5章 时序逻辑电路习题解答

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

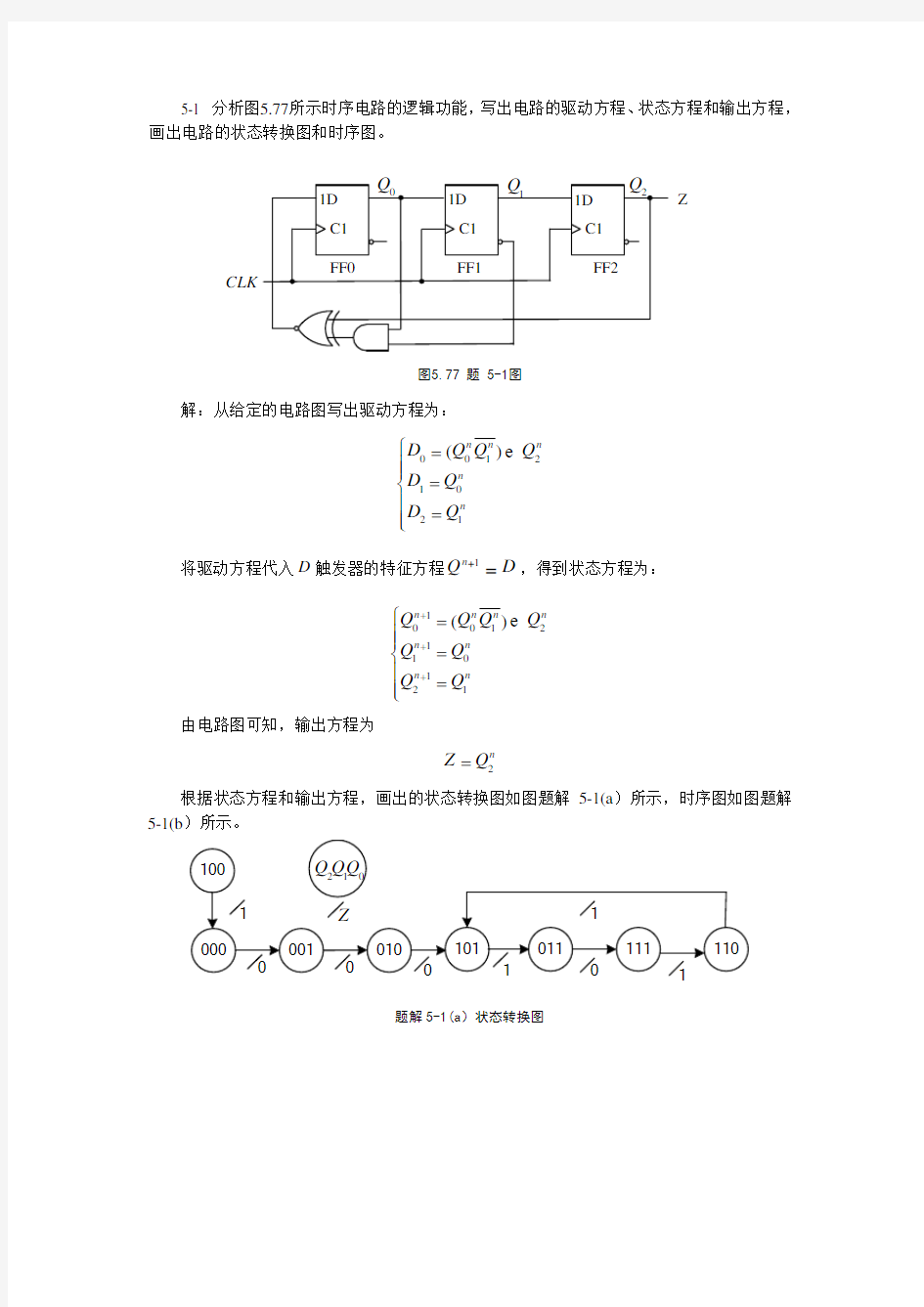

5-1 分析图5.77所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

CLK

Z

图5.77 题 5-1图

解:从给定的电路图写出驱动方程为:

0012

10

21()n n n n

n D Q Q Q D Q D Q ⎧=⎪⎪=⎨⎪

=⎪⎩

e 将驱动方程代入D 触发器的特征方程D Q

n =+1

,得到状态方程为:

10012110

12

1()n n n n n n

n n Q Q Q Q Q Q Q Q +++⎧=⎪⎪=⎨⎪=⎪⎩e 由电路图可知,输出方程为

2

n

Z Q =

根据状态方程和输出方程,画出的状态转换图如图题解5-1(a )所示,时序图如图题解5-1(b )所示。

题解5-1(a )状态转换图

1

Q 2/Q Z

Q

题解5-1(b )时序图

综上分析可知,该电路是一个四进制计数器。

5-2 分析图5.78所示电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。A 为输入变量。

Y

A

图5.78 题 5-2图

解:首先从电路图写出驱动方程为:

()

0110101()n n n n n

D AQ D A Q Q A Q Q ⎧=⎪

⎨==+⎪⎩

将上式代入触发器的特征方程后得到状态方程

()

1011

10101()n n n n n n n

Q AQ Q A Q Q A Q Q ++⎧=⎪

⎨==+⎪⎩

电路的输出方程为:

01n n

Y AQ Q =

根据状态方程和输出方程,画出的状态转换图如图题解5-2所示

Y

A

题解5-2 状态转换图

综上分析可知该电路的逻辑功能为:

当输入为0时,无论电路初态为何,次态均为状态“00”,即均复位;

当输入为1时,无论电路初态为何,在若干CLK 的作用下,电路最终回到状态“10”。

5-3 已知同步时序电路如图5.79(a)所示,其输入波形如图5.79 (b)所示。试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图,并说明该电路的功能。

X

(a) 电路图

1234CLK

5678

X

(b)输入波形 图5.79 题 5-3图

解:电路的驱动方程、状态方程和输出方程分别为:

0010110001101101

1, ,n n n n n n n n n n

J X K X J XQ K X

Q X Q XQ X

Q XQ Q XQ XQ XQ Y XQ ++⎧==⎪⎨==⎪⎩⎧=+=⎪⎨

⎪=+=+⎩= 根据状态方程和输出方程,可分别做出11

10,n n Q Q ++和Y 的卡诺图,如表5-1所示。由此

做出的状态转换图如图题解5-3(a)所示,画出的时序图如图题解5-3(b )所示。

表5.1 状态转换表

Y

X

5-3(a) 状态转换图

X

1Q Q Y

题解5-3(b )时序图

综上分析可知:当输入X 为序列110时,输出Y =1,因此,该电路是110序列检测器。

5-4 试画出用4片74LS194A 组成16位双向移位寄存器的逻辑图。74LS194A 的功能表见

表5.9。

解:见图题解5-4。

题解5-4 电路图

5-5 在图5.80所示的电路中,若两个移位寄存器中的原始数据分别为A 3A 2A 1A 0=1100,B 3B 2B 1B 0=0001,CI 的初值为0,试问经过4个CLK 信号作用以后两个寄存器中的数据如何?这个电路完成什么功能?

CLK

图5.80 题 5-5图

解:经过4个CLK 信号后,两个寄存器里的数据分别为:

1101000111000123=

+=A A A A ,00000123=B B B B

这是一个4位串行加法器电路。

5-6 分析图5.81的计数器电路,画出电路的状态转换图,说明这是多少进制的计数器。十六进制计数器74161的功能表如表5.13所示。

计计计计1

计

图5.81 题 5-6图

解:图 5.81所示的电路,是用异步置零法构成的十进制计数器,当计数进入

1010

0123=Q Q Q Q 状态,与非门译码器输出低电平置零信号,立刻将74161置成

00000123=Q Q Q Q 状态,由于10100123=Q Q Q Q 是一个过渡状态,不存在稳定状态的循

环中,所以电路按1001~0000这十个状态顺序循环,从而构成十进制计数器。

5-7 分析图5.82的计数器电路,在M =0和M =1时各为几进制?计数器74160的功能表与表5.13相同。

计计

Y

图5.82 题 5-7图

解:图5.82所示的电路,是用同步置数法将74160接成的可变模计数器。

在M =1时,当电路进入状态10010123=Q Q Q Q 以后,0=LD ,下一个CLK 到达时,将01000123=D D D D 置入电路中,使01000123=Q Q Q Q ,然后再从0100继续做加法计数。因此,电路按1001~0100这六个状态顺序循环,从而构成六进制计数器。

同理。在M =0,电路将按1001~0010这八个状态顺序循环,故形成八进制计数器。

5-8 图5.83电路时可变模计数器。试分析当控制变量A 为0和1时电路各为几进制计数器。74161的功能表见表5.13。

计计计计

1

图5.83 题 5-8图

解:这是用同步置数法接成的可控进制计数器。在A =1时,计数器计为

10110123=Q Q Q Q 后,给出0=LD 信号,下一个CLK 到来时计数器被置成00000123=Q Q Q Q ,故是一个十二进制计数器。在A =0时,计数器计为1001

0123=Q Q Q Q 后,给出0=LD 信号,下一个CLK 到来时,计数器被置成00000123=Q Q Q Q ,故构成十进制计数器。

5-9 十六进制计数器74161的功能表如表5.13所示,试以74161设计一个可控进制计数器,当输入控制变量M =0时工作在五进制,M =1时工作在十五进制。请标出计数器输入端和