ModelSim Verilog仿真实例附程序

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ModelSim Verilog仿真实例

FPGA 2010-04-28 11:41:09 阅读268 评论0 字号:大中小

收藏来自:/Blog/cns!F504AD3E4821141E!289.entry ModelSim Verilog仿真实例

最近在学习Verilog HDL,编辑了几个简单的实例用ModelSIm仿真。现在把使用ModelSim的一个仿真实例记录下来,算是入门级的。

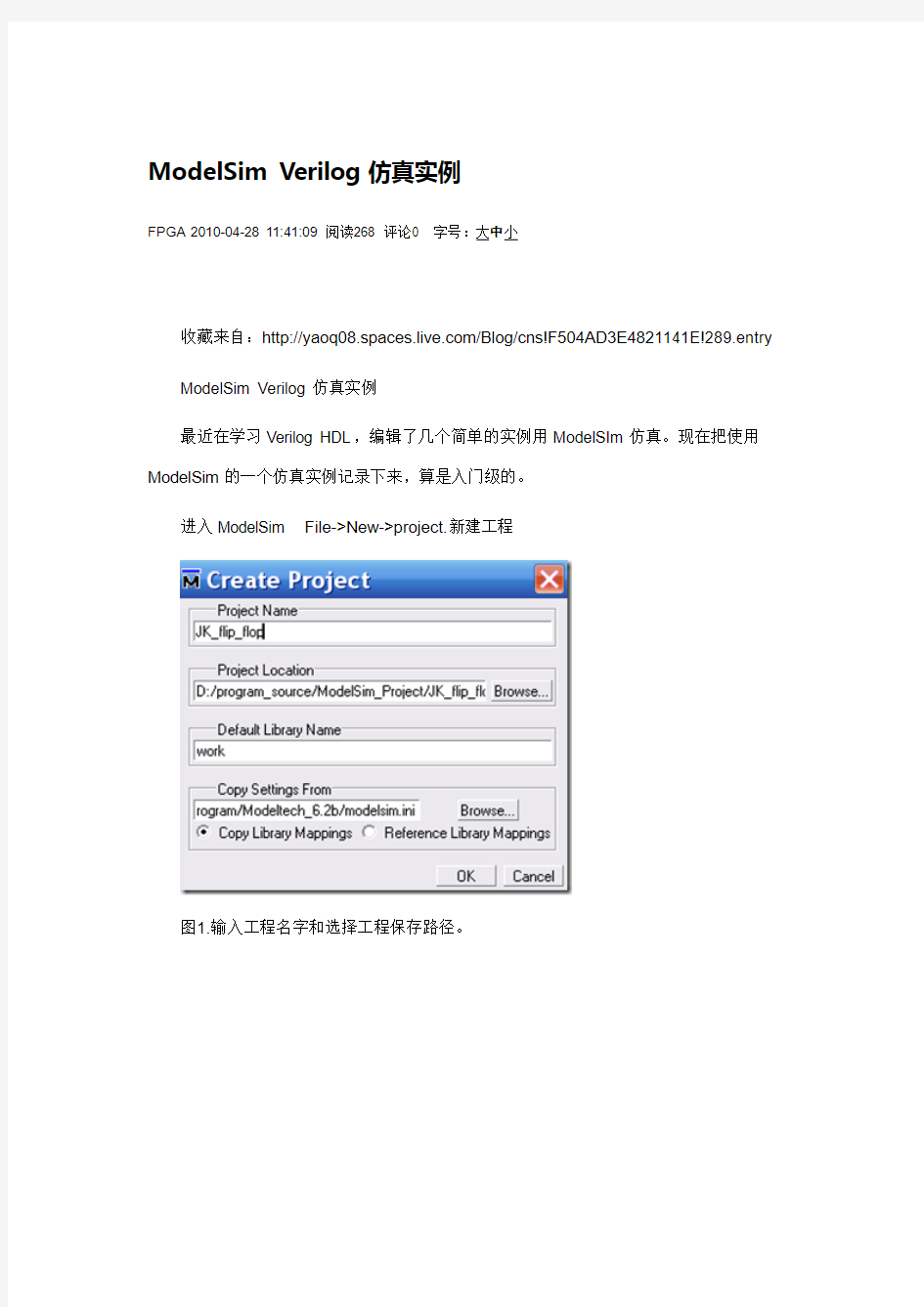

进入ModelSim File->New->project.新建工程

图1.输入工程名字和选择工程保存路径。

图2.创建新的源文件或者添加已经编辑好的文件。

添加JK_flip_flop.v文件之后,在Workspace栏中会显示出来,双击文件就可以编辑了。

编辑完之后在Workspace右键选中文件,compile->compile all,或者点击工具条上的图标。

如果在Transcript会出现# Compile of JK_flip_flop_tb.v was successful.的提示

现在编辑Testbench文件,同样新建一个源文件,File->source->Verilog. 跳出编辑窗口

在菜单栏中选中Source->show Language Templates,然后在Language T emplates 中撞击Create Testbench,

图3.Testbench创建向导

然后在work下面选中JK_flip_flop,点击next,再点击Finish。根据自己的设计添加内容。

图4.添加内容

编辑完之后进行编译。同编译JK_flip_flop一样。或者在菜单栏中compile->compile all,在Transcipt窗口中显示编译成功。

开始仿真

菜单栏Stimulate->start Stimulation,

图5.仿真选项设置

然后选中work下面的JK_flip_flop_tb点击OK。尤其要注意的是不要选中Enable optimization。否则很容易会把仿真的输入信号给优化掉。

图6.连接输出波形文件

然后在工具栏中点击run,或者菜单栏中,stimulaite-run-run all,开始仿真,如下图。

图7.仿真波形。

附源文件:

/******************************************************** 文件名:JK_flip_flop.v

描述:主从Jk触发器Verilog HDL描述

作者:KiKi

mail:yq000cn@

时间:2009年2月22日晚

********************************************************/

`timescale 1ns/1ns

module JK_flip_flop(J,K,Clk,Q,Qbar);

input J,K,Clk;

output Q,Qbar;

reg Q;

assign Qbar=~Q;

always @(negedge Clk)

begin

case({J,K})

2'b00:Q=Q;

2'b01:Q=1;

2'b10:Q=0;

2'b11:Q=~Q;

default:Q=1'bx;

endcase

end

endmodule

/******************************************************** 文件名:JK_flip_flop_tb.v

描述:JK_flip_flop.v的测试文件

作者:KiKi

mail:yq000cn@

时间:2009年2月22日晚

********************************************************/ module JK_flip_flop_tb ;

wire Q ;

wire Qbar ;

reg Clk ;

reg J ;

reg K ;

initial

begin

J=0;

K=0;

Clk=0;

end

always

#2 Clk=!Clk;

always

begin

#6 J<=0;

#8 K<=0;

#16 J<=1;

#26 K<=1;

#36 J<=0;

#500 $stop; end

JK_flip_flop

DUT (

.Q (Q ) ,

.Qbar (Qbar ) ,

.Clk (Clk ) ,

.J (J ) ,

.K (K ) ); endmodule