CEC networking using STM32F100xx value line microcontrollers

stm32f10x启动文件及注释中文翻译

**这里是STM32比较重要的头文件我愛你的吻123原創講解 QQ:1746430162****************************************************************************** * @file stm32f10x.h ST 标准的头文件* @author MCD Application Team 微控制器开发小组。

* @version V3.5.0 版本* @date 11-March-2011 2011年3月11* @brief CMSIS Cortex-M3 Device Peripheral Access Layer Header File.(CMSIS:Cortex Microcontroller Software Interface Standard) 是 Cortex-M 处理器系列的与供应商无关的硬件抽象层。

* This file contains all the peripheral register's definitions, bits* definitions and memory mapping for STM32F10x Connectivity line,* High density, High density value line, Medium density,* Medium density Value line, Low density, Low density Value line* and XL-density devices.* 这个文件包含了芯片STM32F10X(接口增强型)内部的寄存器定义,位定义,内存地址变换定义,还有一些相应的高密度,低密度产品线的设备。

* The file is the unique include file that the application programmer* is using in the C source code, usually in main.c. This file contains:* - Configuration section that allows to select:* - The device used in the target application* - To use or not the peripherals drivers in application code(i.e.* code will be based on direct access to peripherals registers* rather than drivers API), this option is controlled by* "#define USE_STDPERIPH_DRIVER"* - To change few application-specific parameters such as the HSE* crystal frequency* - Data structures and the address mapping for all peripherals* - Peripheral's registers declarations and bits definition* - Macros to access peripheral registers hardware*这个文件在应用程序中是至关重要的头文件,它是用C代码编写而成。

STM32F10功能模块

STM32F10功能模块STM32F10是STMicroelectronics(意法半导体)推出的一系列32位ARM Cortex-M3内核的微控制器产品。

它们在嵌入式系统应用中广泛使用,具有强大的性能和丰富的功能模块。

下面将详细介绍一些STM32F10的主要功能模块:1. Cortex-M3内核:2.存储器:STM32F10系列微控制器具有非常丰富的存储器资源。

它们通常包括闪存和RAM存储器。

闪存存储器用于存储程序代码和数据,而RAM存储器用于存储变量和堆栈数据。

不同型号的STM32F10可以有不同大小的存储器,从几十KB到几百KB不等。

3.时钟和时钟控制:STM32F10微控制器内置了多种时钟源,以满足不同应用的需求。

它们通常包括内部RC振荡器、外部晶体振荡器和PLL(锁相环)等。

时钟控制器模块可以配置和控制系统时钟的频率,并且可以根据需要切换不同的时钟源。

4.GPIO(通用输入输出):STM32F10微控制器具有大量的GPIO引脚,用于连接外部设备。

GPIO模块可以配置不同的引脚作为输入或输出,并且可以设置中断功能,以便实时响应外部事件。

此外,GPIO模块还支持上拉或下拉电阻,以适应不同的外部设备连接需求。

5.UART(异步串行通信接口):STM32F10微控制器集成了多个UART模块,用于实现串口通信。

每个UART通道都有自己的发送和接收缓冲区,并且可以配置不同的波特率、数据位数、校验位和停止位等参数。

UART模块还支持硬件流控制,以提高通信的可靠性。

6.SPI(串行外设接口)和I2C(串行外设接口):SPI和I2C是常用的串行通信协议,用于与外部设备进行通信。

STM32F10微控制器集成了多个SPI和I2C接口,以支持与各种外设(如传感器、显示器等)的数据交换。

这些接口具有配置灵活、高速传输和多主机支持等特性。

7.ADC(模数转换器):STM32F10微控制器通常内置多个ADC模块,用于模拟信号的转换。

STM32中文参考手册 80

互联型产品的复位和时钟控制(RCC) STM32F10xxx参考手册图11时钟树

1.当HSI被用于作为PLL时钟的输入时,系统时钟能得到的最大频率是36MHz。

2.对于内部和外部时钟源的特性,请参考相应产品数据手册中“电气特性”章节。

高级时钟控制器拥有3个PLL,为使用外部晶体或振荡器提供了高度的灵活性,使得核心和外设能够工作在最高的频率,同时保证以太网和全速的USB OTG能够有合适的时钟。

一个单一的25MHz晶体可以为整个系统和所有包括以太网和全速USB OTG的外设提供时钟。

为了实现高质量的音频性能,可以使用一个音频晶体;这样,I2S的主时钟可以产生所有从8kHz至96kHz之间的标准采样频率,而误差小于0.5%。

更多关于以太网、全速USB OTG和/或I2S(音频)时钟配置的需求,请参考互联型产品数据手册的“附录A 应用框图”。

用户可通过多个预分频器配置AHB、高速APB(APB2)和低速APB(APB1)域的频率。

AHB和APB2域的最大频率是72MHz。

APB1域的最大允许频率是36MHz。

除去以下情况,所有外设的时钟都是从系统时钟(SYSCLK)得到:

● Flash存储器编程接口时钟始终是HSI时钟。

80/754

参照2009年12月 RM0008 Reference Manual 英文第10版本译文仅供参考,如有翻译错误,请以英文原稿为准。

请读者随时注意在ST网站下载更新版本。

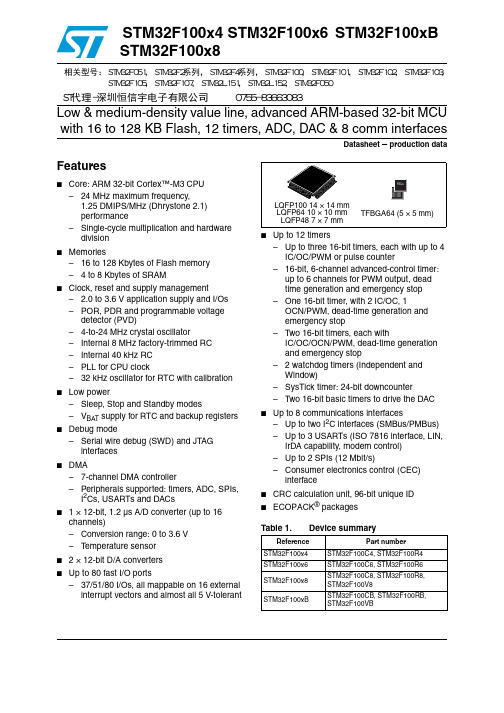

STM32F100英文规格书

■

■

■

■ ■

■

Table 1.

2.1 2.2 Device overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.2.1 2.2.2 2.2.3 2.2.4 2.2.5 2.2.6 2.2.7 2.2.8 2.2.9 2.2.10 2.2.11 2.2.12 2.2.13 2.2.14 2.2.15 2.2.16 2.2.17 2.2.18 2.2.19 2.2.20 2.2.21 2.2.22 2.2.23 2.2.24 2.2.25 ARM® Cortex™-M3 core with embedded Flash and SRAM . . . . . . . . . 14 Embedded Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 CRC (cyclic redundancy check) calculation unit . . . . . . . . . . . . . . . . . . 14 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . 14 External interrupt/event controller (EXTI) . . . . . . . . . . . . . . . . . . . . . . . 15 Clocks and startup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Boot modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Power supply schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 RTC (real-time clock) and backup registers . . . . . . . . . . . . . . . . . . . . . . 17 Timers and watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 I²C bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Universal synchronous/asynchronous receiver transmitter (USART) . . 19 Serial peripheral interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 HDMI (high-definition multimedia interface) consumer electronics control (CEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 GPIOs (general-purpose inputs/outputs) . . . . . . . . . . . . . . . . . . . . . . . . 20 Remap capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 ADC (analog-to-digital converter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 DAC (digital-to-analog converter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Serial wire JTAG debug port (SWJ-DP) . . . . . . . . . . . . . . . . . . . . . . . . . 21

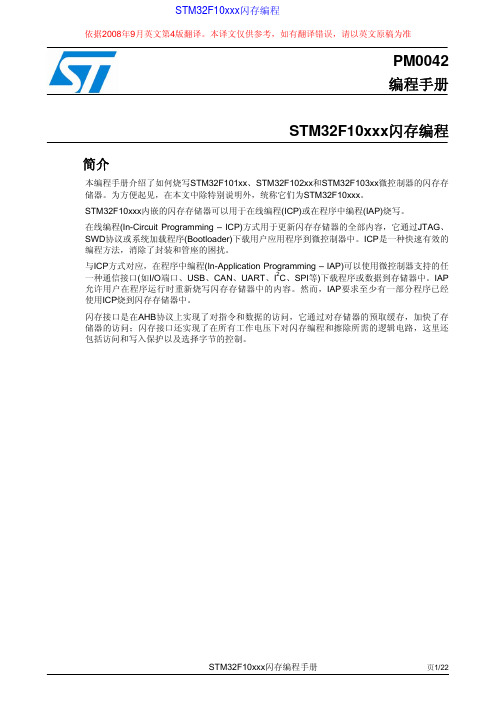

【PM0042】STM32F10xxx闪存编程参考手册

STM32F100xx SWD 在线编程参考指南

ApplicationNoteAN05220079 V1.00 Date: 2014/10/23 STM32F100xx SWD 在线编程参考指南广州致远电子股份有限公司目录1. STM32F100xx简介 (1)2. AK100Pro简介 (2)3. 准备条件 (4)3.1准备STM32F100VC目标板 (4)3.2安装KFlashPro软件 (4)3.3连接STM32F100VC目标板至AK100Pro-4P (5)4. 基本烧写 (7)4.1创建工程 (7)4.2参数配置 (7)4.2.1硬件选择 (7)4.2.2主要设置 (8)4.2.3附加设置 (9)4.2.4程序烧写 (9)4.3烧写配置 (10)4.4进行烧写 (11)5. 高级烧写 (12)5.1量产烧写配置 (13)5.2加密与解密 (14)5.2.1加密 (14)5.2.2解密 (15)6. 技术支持 (16)7. 订购信息 (17)1. STM32F100xx简介STM32F100xx 系列是ST公司推出的一款基于ARM高性能Cortex-M3 32位RISC内核微控制器,工作频率为24MHz。

STM32F100xx系列主要用于应用控制和用户界面、电机驱动、医疗和手持式设备、PC和游戏机外设、GPS平台、工业应用、PLC、逆变器、打印机、扫描仪、警报系统、视频对讲和HVAC。

其内部结构框图如图1.1(来源于芯片手册)所示。

AK100pro-4P支持STM32F100xx 系列JTAG/SWD在线编程,本文档以对STM32F100VC操作为例子,介绍使用AK100pro-4P通过SWD编程接口烧写STM32F100xx 系列微控制器的内部Flash。

图 1.1 High-density STM32F100xx 结构框图2. AK100Pro简介AK100Pro是广州致远电子股份有限公司开发的专业型量产在线编程器,增强型的AK100Pro-4P能同时实现4个通道同时在线编程,为工厂量产烧写提供完善的解决方案。

Stm32f10x固件库3.5使用指南

stm32f10x_rtc.c stm32f10x_sdio.c stm32f10x_spi.c

RTC 模块的固件函数 SD 接口的固件函数 SPI 接口的固件函数

stm32f10x_tim.c

定时器的固件函数

stm32f10x_usart.c stm32f10x_wwdg.c

USART 的固件函数 窗口开门狗的固件函数

1

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

珠联璧合

xlzhu@

STM32F10x 库 3.5 使用指南

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

3.1 Libraries 目录结构

Libraries 由 CMSIS 标 准 ( Cortex MicroController Software Interface Standard ) 和 STM32F10x_StdPeriph_Driver(标准外设驱动)构成。

FSMC 接口的固件函数

stm32f10x_gpio.c

GPIO 模块的固件函数

stm32f10x_i2c.c stm32f10x_iwdg.c stm32f10x_pwr.c

I2C 模块的固件函数 独立开门狗的固件函数 电源/功耗控制的固件函数

stm32f10x_rcc.c

复位和时钟控制的固件函数

高密度产品,FLASH 大于 128K 互联性高密度产品

startup_stm32f10x_ld.s

低密度产品,FLASH 小于 64K

startup_stm32f10x_ld_vl.s

低密度互联性产品

startup_stm32f10x_md.s startup_stm32f10x_md_vl.s

第1章STM32F10X系统介绍

第1章STM32F10X系统介绍STM32F10X 是一款由意法半导体(STMicroelectronics)推出的32位ARM Cortex-M3 微控制器系列。

该系列具有高性能和低功耗的特点,广泛应用于工业控制、汽车电子、家用电器、医疗设备等领域。

STM32F10X 系列采用了先进的微控制器技术,结合了ARM Cortex-M3 内核的强大处理能力和低功耗特性。

它具有高达72MHz 的处理器频率,并且内置了丰富的外设和功能模块,如多个通用定时器、I/O 端口、通用串行总线接口(USART)、SPI 接口、I2C 接口等。

此外,它还支持多种存储介质,如闪存、SRAM 以及嵌入式模拟存储器。

在系统结构上,STM32F10X系列采用了多层总线架构。

它由处理器总线、AHB总线和APB总线组成,这些总线分别用于连接处理器核心、内存和外设。

这种层次化的总线结构使得系统具有高灵活性和可扩展性,能够满足不同应用场景的需求。

值得一提的是,STM32F10X 系列采用了意法半导体独有的ART (Adaptive Real-Time)加速器技术。

该技术能够提高嵌入式应用的实时性能和性能效率,通过优化指令和数据缓存访问,显著提高数据处理速度和系统响应速度。

综上所述,STM32F10X系列是一款高性能、低功耗的32位微控制器,具有强大的处理能力和丰富的外设。

它在工业控制、汽车电子、家用电器等领域得到广泛应用,并且配备了丰富的调试和开发工具,极大地简化了软件开发过程。

随着意法半导体不断推出新的版本和增加新的功能模块,STM32F10X系列将继续为嵌入式系统的设计者和开发者提供更多新的选择和解决方案。

stm32f10x参考手册

STM32F10x参考手册第一版STM32F10x参考手册1文档中的约定 (1)1.1寄存器描述中使用的缩写列表 (1)2存储器和总线构架 (2)2.1系统构架 (2)2.2存储器组织 (3)2.3存储器映像 (4)2.3.1外设存储器映像 (5)2.3.2嵌入式SRAM (6)2.3.3位段 (6)2.3.4嵌入式闪存 (6)2.4启动配置 (8)3电源控制(PWR) (9)3.1电源 (9)3.1.1独立的A/D转换器供电和参考电压 (9)3.1.2电池备份 (9)3.1.3电压调节器 (10)3.2电源管理器 (10)3.2.1上电复位(POR)和掉电复位(PDR) (10)3.2.2可编程电压监测器(PVD) (10)3.3低功耗模式 (11)3.3.1降低系统时钟 (12)3.3.2外部时钟的控制 (12)3.3.3睡眠模式 (12)3.3.4停止模式 (13)3.3.5待机模式 (14)3.3.6低功耗模式下的自动唤醒(AWU) (15)3.4电源控制寄存器 (16)3.4.1电源控制寄存器(PWR_CR) (16)3.4.2电源控制/状态寄存器 (17)3.5PWR寄存器映像 (18)4复位和时钟控制 (19)4.1复位 (19)4.1.1系统复位 (19)4.1.2电源复位 (19)4.2时钟 (20)4.2.1HSE时钟 (22)4.2.2HSI时钟 (22)4.2.3PLL (23)4.2.4LSE时钟 (23)4.2.5LSI时钟 (23)4.2.6系统时钟(SYSCLK)选择 (24)4.2.7时钟安全系统(CSS) (24)4.2.8RTC时钟 (24)4.2.9看门狗时钟 (24)4.2.10时钟输出 (25)4.3RCC寄存器描述 (26)4.3.1时钟控制寄存器(RCC_CR) (26)4.3.2时钟配置寄存器(RCC_CFGR) (27)4.3.3时钟中断寄存器 (RCC_CIR) (29)4.3.4APB2外设复位寄存器 (RCC_APB2RSTR) (32)4.3.5APB1外设复位寄存器 (RCC_APB1RSTR) (33)4.3.6AHB外设时钟使能寄存器 (RCC_AHBENR) (35)4.3.7APB2外设时钟使能寄存器(RCC_APB2ENR) (36)4.3.8APB1外设时钟使能寄存器(RCC_APB1ENR) (37)4.3.9备份域控制寄存器 (RCC_BDCR) (39)4.3.10控制/状态寄存器 (RCC_CSR) (40)4.4RCC寄存器映像 (43)5通用和复用功能I/O(GPIO和AFIO) (44)5.1GPIO功能描述 (44)5.1.1通用I/O(GPIO) (45)5.1.2单独的位设置或位清除 (45)5.1.3外部中断/唤醒线 (46)5.1.4复用功能(AF) (46)5.1.5软件重新映射I/O复用功能 (46)5.1.6GPIO锁定机制 (46)5.1.7输入配置 (46)5.1.8输出配置 (47)5.1.9复用功能配置 (48)5.2GPIO寄存器描述 (50)5.2.1端口配置低寄存器(GPIOx_CRL) (x=A..E) (50)5.2.2端口配置高寄存器(GPIOx_CRH) (x=A..E) (51)5.2.3端口输入数据寄存器(GPIOx_IDR) (x=A..E) (52)5.2.4端口输出数据寄存器(GPIOx_ODR) (x=A..E) (52)5.2.5端口位设置/复位寄存器(GPIOx_BSRR) (x=A..E) (53)5.2.6端口位复位寄存器(GPIOx_BRR) (x=A..E) (53)5.2.7端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) (54)5.3复用功能I/O和调试配置(AFIO) (55)5.3.1把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1 (55)5.3.2BXCAN复用功能重映射 (55)5.3.3JTAG/SWD复用功能重映射 (55)5.3.4定时器复用功能重映射 (56)5.3.5USART复用功能重映射 (57)5.3.6I2C 1 复用功能重映射 (58)5.3.7SPI 1复用功能重映射 (58)5.4AFIO寄存器描述 (59)5.4.1复用重映射和调试I/O配置寄存器(AFIO_MAPR) (60)5.4.2外部中断配置寄存器1(AFIO_EXTICR1) (62)5.4.3外部中断配置寄存器2(AFIO_EXTICR2) (62)5.4.4外部中断配置寄存器3(AFIO_EXTICR3) (63)5.4.5外部中断配置寄存器4(AFIO_EXTICR4) (63)5.5GPIO 和AFIO寄存器地址映象 (64)5.5.1GPIO寄存器地址映象 (64)5.5.2AFIO寄存器地址映象 (65)6中断和事件 (66)6.1嵌套向量中断控制器(NVIC) (66)6.1.1系统嘀嗒(SysTick)校准值寄存器 (66)6.1.2中断和异常向量 (66)6.2外部中断/事件控制器(EXTI) (68)6.2.1主要特性 (68)6.2.2框图 (69)6.2.3唤醒事件管理 (69)6.2.4功能说明 (69)6.2.5外部中断/事件线路映像 (71)6.3EXTI 寄存器描述 (72)6.3.1外部中断/事件寄存器映像 (75)7DMA 控制器(DMA) (76)7.1简介 (76)7.2主要特性 (76)7.3功能描述 (77)7.3.1DMA处理 (77)7.3.2仲裁器 (77)7.3.3DMA 通道 (78)7.3.4错误管理 (79)7.3.5DMA请求映像 (79)7.4DMA寄存器 (82)7.4.1DMA中断状态寄存器(DMA_ISR) (82)7.4.2DMA中断标志清除寄存器(DMA_IFCR) (82)7.4.3DMA通道x配置寄存器(DMA_CCRx)(x = 1...7).. (83)7.4.4DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1...7) (85)7.4.5DMA通道x外设地址寄存器(DMA_CPARx)(x = 1...7).. (85)7.4.6DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1...7).. (85)7.5DMA寄存器映像 (86)8实时时钟(RTC) (88)8.1简介 (88)8.2主要特性 (88)8.3功能描述 (88)8.3.1概述 (88)8.3.2复位过程 (90)8.3.3读RTC寄存器 (90)8.3.4配置RTC寄存器 (90)8.3.5RTC标志的设置 (90)8.4RTC寄存器描述 (91)8.4.1RTC控制寄存器高位(RTC_CRH) (91)8.4.2RTC控制寄存器低位(RTC_CRL) (92)8.4.3RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) (93)8.4.4RTC预分频分频因子寄存器(RTC_DIVH / RTC_DIVL) (94)8.4.5RTC计数器寄存器 (RTC_CNTH / RTC_CNTL) (95)8.4.6RTC闹钟寄存器(RTC_ALRH/RTC_ALRL) (95)8.5RTC寄存器映像 (97)9备份寄存器(BKP) (98)9.1简介 (98)9.2特性 (98)9.3侵入检测 (98)9.4RTC校准 (98)9.5BKP寄存器描述 (99)9.5.1备份数据寄存器x(BKP_DRx) (x = 1 ... 10) (99)9.5.2RTC时钟校准寄存器(BKP_RTCCR) (99)9.5.3备份控制寄存器(BKP_CR) (99)9.5.4备份控制/状态寄存器(BKP_CSR) (100)9.6BKP寄存器映像 (101)10独立看门狗(IWDG) (103)10.1简介 (103)10.1.1硬件看门狗 (103)10.1.2寄存器访问保护 (103)10.1.3调试模式 (104)10.2IWDG寄存器描述 (104)10.2.1键寄存器(IWDG_KR) (104)10.2.2预分频寄存器(IWDG_PR) (105)10.2.3重装载寄存器(IWDG_RLR) (106)10.2.4状态寄存器(IWDG_SR) (106)10.3IWDG寄存器映像 (107)11窗口看门狗(WWDG) (108)11.1简介 (108)11.2主要特性 (108)11.3功能描述 (108)11.4如何编写看门狗超时程序 (109)11.5调试模式 (110)11.6寄存器描述 (111)11.6.1控制寄存器(WWDG_CR) (111)11.6.2配置寄存器(WWDG_CFR) (111)11.6.3状态寄存器(WWDG_SR) (112)11.7WWDG寄存器映像 (113)12高级控制定时器(TIM1) (114)12.1简介 (114)12.2主要特性 (114)12.3框图 (115)12.4功能描述 (116)12.4.1时基单元 (116)12.4.2计数器模式 (117)12.4.3重复向下计数器 (125)12.4.4时钟选择 (126)12.4.5捕获/比较通道 (129)12.4.6输入捕获模式 (131)12.4.7PWM输入模式 (132)12.4.8强置输出模式 (132)12.4.9输出比较模式 (133)12.4.10PWM 模式 (134)12.4.11互补输出和死区插入 (136)12.4.12使用刹车功能 (138)12.4.13在外部事件时清除OCxREF信号 (139)12.4.14六步PWM的产生 (140)12.4.15单脉冲模式 (141)12.4.16编码器接口模式 (143)12.4.17定时器输入异或功能 (144)12.4.18与霍尔元件的接口 (145)12.4.19定时器和外部触发的同步 (146)12.4.20定时器同步 (149)12.4.21调试模式 (149)12.5TIM1寄存器描述 (150)12.5.1控制寄存器1(TIM1_CR1) (150)12.5.2控制寄存器2(TIM1_CR2) (151)12.5.3从模式控制寄存器(TIM1_SMCR) (153)12.5.4DMA/中断使能寄存器(TIM1_DIER) (154)12.5.5状态寄存器(TIM1_SR) (156)12.5.6事件产生寄存器(TIM1_EGR) (157)12.5.7捕获/比较模式寄存器1(TIM1_CCMR1) (158)12.5.8捕获/比较模式寄存器2(TIM1_CCMR2) (161)12.5.10计数器(TIM1_CNT) (165)12.5.11预分频器(TIM1_PSC) (165)12.5.12自动重装载寄存器(TIM1_ARR) (165)12.5.13周期计数寄存器(TIM1_RCR) (166)12.5.14捕获/比较寄存器1(TIM1_CCR1) (166)12.5.15捕获/比较寄存器2(TIM1_CCR2) (167)12.5.16捕获/比较寄存器3(TIM1_CCR3) (167)12.5.17捕获/比较寄存器(TIM1_CCR4) (168)12.5.18刹车和死区寄存器(TIM1_BDTR) (168)12.5.19DMA控制寄存器(TIM1_DCR) (170)12.5.20连续模式的DMA地址(TIM1_DMAR) (170)12.6TIM1寄存器图 (171)13通用定时器(TIMx) (173)13.1概述 (173)13.2主要特性 (173)13.3框图 (174)13.4功能描述 (175)13.4.1时基单元 (175)13.4.2计数器模式 (176)13.4.3时钟选择 (183)13.4.4捕获/比较通道 (185)13.4.5输入捕获模式 (187)13.4.6PWM输入模式 (187)13.4.7强置输出模式 (188)13.4.8输出比较模式 (188)13.4.9PWM 模式 (189)13.4.10单脉冲模式 (191)13.4.11在外部事件时清除OCxREF信号 (193)13.4.12编码器接口模式 (193)13.4.13定时器输入异或功能 (195)13.4.14定时器和外部触发的同步 (195)13.4.15定时器同步 (198)13.4.16调试模式 (202)13.5TIMx寄存器描述 (203)13.5.2控制寄存器2(TIMx_CR2) (205)13.5.3从模式控制寄存器(TIMx_SMCR) (206)13.5.4DMA/中断使能寄存器(TIMx_DIER) (207)13.5.5状态寄存器(TIMx_SR) (209)13.5.6事件产生寄存器(TIMx_EGR) (211)13.5.7捕获/比较模式寄存器1(TIMx_CCMR1) (212)13.5.8捕获/比较模式寄存器2(TIMx_CCMR2) (215)13.5.9捕获/比较使能寄存器(TIMx_CCER) (216)13.5.10计数器(TIMx_CNT) (218)13.5.11预分频器(TIMx_PSC) (218)13.5.12自动重装载寄存器(TIMx_ARR) (218)13.5.13捕获/比较寄存器1(TIMx_CCR1) (219)13.5.14捕获/比较寄存器2(TIMx_CCR2) (220)13.5.15捕获/比较寄存器3(TIMx_CCR3) (220)13.5.16捕获/比较寄存器(TIMx_CCR4) (221)13.5.17DMA控制寄存器(TIMx_DCR) (221)13.5.18连续模式的DMA地址(TIMx_DMAR) (222)13.6TIMx寄存器图 (223)14控制器局域网(bxCAN) (225)14.1简介 (225)14.2主要特点 (225)14.3总体描述 (225)14.3.1CAN 2.0B内核 (226)14.3.2控制、状态和配置寄存器 (226)14.3.3发送邮箱 (226)14.3.4接收过滤器 (226)14.3.5接收FIFO (227)14.4工作模式 (228)14.4.1初始化模式 (228)14.4.2正常模式 (228)14.4.3睡眠模式(低功耗) (228)14.4.4测试模式 (229)14.4.5静默模式 (229)14.4.6环回模式 (229)14.4.7环回静默模式 (230)14.5功能描述 (230)14.5.1发送处理 (230)14.5.2时间触发通信模式 (232)14.5.3接收管理 (232)14.5.4标识符过滤 (234)14.5.5报文存储 (238)14.5.6出错管理 (239)14.5.7位时间特性 (239)14.6中断 (241)14.7寄存器访问保护 (243)14.8CAN 寄存器描述 (243)14.8.1控制和状态寄存器 (243)14.8.2邮箱寄存器 (255)14.8.3CAN过滤器寄存器 (260)14.9bxCAN寄存器列表 (264)15I2C接口 (267)15.1介绍 (267)15.2主要特点 (267)15.3概述 (268)15.4功能描述 (269)15.4.1I2C从模式 (269)15.4.2I2C主模式 (271)15.4.3错误条件 (274)15.4.4SDA/SCL线控制 (275)15.4.5SMBus (275)15.4.6DMA请求 (277)15.4.7包错误校验(PEC) (278)15.5中断请求 (279)15.6I2C寄存器描述 (281)15.6.1控制寄存器1(I2C_CR1) (281)15.6.2控制寄存器2(I2C_CR2) (283)15.6.3自身地址寄存器1 (I2C_OAR1) (284)15.6.4自身地址寄存器2(I2C_OAR2) (285)15.6.5数据寄存器(I2C_DR) (285)15.6.6状态寄存器1(I2C_SR1) (285)15.6.7状态寄存器2 (I2C_SR2) (288)15.6.8时钟控制寄存器(I2C_CCR) (289)15.6.9TRISE寄存器(I2C_TRISE) (290)15.7I2C寄存器地址映象 (291)16串行外设接口(SPI) (292)16.1简介 (292)16.2主要特征 (292)16.3功能描述 (292)16.3.1概述 (292)16.3.2SPI从模式 (295)16.3.3SPI主模式 (296)16.3.4单向通信 (297)16.3.5状态标志 (297)16.3.6CRC计算 (298)16.3.7利用DMA的SPI通信 (299)16.3.8错误标志 (299)16.3.9中断 (300)16.4SPI寄存器描述 (300)16.4.1SPI控制寄存器1(SPI_CR1) (300)16.4.2SPI控制寄存器2(SPI_CR2) (302)16.4.3SPI 状态寄存器(SPI_SR) (303)16.4.4SPI 数据寄存器(SPI_DR) (304)16.4.5SPI CRC多项式寄存器(SPI_CRCPR) (304)16.4.6SPI Rx CRC寄存器(SPI_RXCRCR) (305)16.4.7SPI Tx CRC寄存器(SPI_TXCRCR) (305)16.5SPI 寄存器地址映象 (306)17USART收发器(USART) (307)17.1介绍 (307)17.2概述 (308)17.2.1框图 (309)17.2.2USART 特征描述 (310)17.2.3发送器 (310)17.2.4接收器 (312)17.2.5分数波特率的产生 (315)17.2.617.2.6 多处理器通信 (316)17.2.7校验控制 (317)17.2.8LIN(局域互联网)模式 (318)17.2.9USART 同步模式 (320)17.2.10单线半双工通信 (322)17.2.11智能卡 (322)17.2.12IrDA SIR ENDEC 功能块 (324)17.2.13利用DMA连续通信 (325)17.2.14硬件流控制 (326)17.3中断请求 (327)17.4USART寄存器描述 (329)17.4.1状态寄存器(USART_SR) (329)17.4.2数据寄存器(USART_DR) (330)17.4.3波特比率寄存器(USART_BRR) (331)17.4.4控制寄存器1 (USART_CR1) (331)17.4.5控制寄存器2(USART_CR2) (333)17.4.6控制寄存器3(USART_CR3) (335)17.4.7保护时间和预分频寄存器(USART_GTPR) (336)17.5USART寄存器地址映象 (338)18USB全速设备接口(USB) (339)18.1导言 (339)18.2主要特征 (339)18.3方框图 (339)18.4功能描述 (340)18.4.1USB功能模块描述 (341)18.5编程中需要考虑的问题 (342)18.5.1通用USB设备编程 (342)18.5.2系统复位和上电复位 (342)18.5.3双缓冲端点 (346)18.5.4同步传输 (347)18.5.5挂起/恢复事件 (348)18.6USB寄存器描述 (350)18.6.1通用寄存器 (350)18.6.2端点寄存器 (355)18.6.3缓冲区描述表 (358)18.7USB寄存器映像 (361)19模拟/数字转换(ADC) (363)19.1介绍 (363)19.2主要特征 (363)19.3引脚描述 (365)19.4功能描述 (365)19.4.1ADC开关控制 (365)19.4.2ADC时钟 (365)19.4.3通道选择 (365)19.4.4单次转换模式 (366)19.4.5连续转换模式 (366)19.4.6时序图 (367)19.4.7模拟看门狗 (368)19.4.8扫描模式 (368)19.4.9注入通道管理 (369)19.4.10间断模式 (369)19.5校准 (370)19.6数据对齐 (371)19.7可编程的通道采样时间 (371)19.8外部触发转换 (371)19.9DMA请求 (372)19.10双ADC模式 (372)19.10.1同时注入模式 (374)19.10.2同时规则模式 (374)19.10.3快速交替模式 (375)19.10.4慢速交替模式 (375)19.10.5交替触发模式 (376)19.10.6独立模式 (377)19.10.7混合的规则/注入同步模式 (377)19.10.8混合的同步规则+交替触发模式 (377)19.10.9混合同步注入+交替模式 (378)19.11温度传感器 (378)19.12中断 (379)19.13ADC寄存器描述 (381)19.13.1ADC状态寄存器(ADC_SR) (381)19.13.2ADC控制寄存器1(ADC_CR1) (382)19.13.3ADC控制寄存器2(ADC_CR2) (384)19.13.4ADC采样时间寄存器1(ADC_SMPR1) (387)19.13.5ADC采样时间寄存器2(ADC_SMPR2) (387)19.13.6ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) (388)19.13.7ADC看门狗高阀值寄存器(ADC_HTR) (388)19.13.8ADC看门狗低阀值寄存器(ADC_LRT) (388)19.13.9ADC规则序列寄存器1(ADC_SQR1) (390)19.13.10ADC规则序列寄存器2(ADC_SQR2) (390)19.13.11ADC规则序列寄存器3(ADC_SQR3) (391)19.13.12ADC注入序列寄存器(ADC_JSQR) (391)19.13.13ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4) (392)19.13.14ADC规则数据寄存器(ADC_DR) (392)19.14ADC寄存器地址映像 (394)20调试支持(DBG) (396)20.1概况 (396)20.2ARM参考文献 (397)20.3SWJ调试端口(serial wire and JTAG) (397)20.3.1JTAG-DP和SW-DP切换的机制 (397)20.4引脚分布和调试端口脚 (398)20.4.1SWJ调试端口脚 (398)20.4.2灵活的SWJ-DP脚分配 (398)20.4.3JTAG脚上的内部上拉和下拉 (399)20.4.4利用串行接口并释放不用的调试脚作为普通I/O口 (400)20.5STM32F10x JTAG TAP 连接 (400)20.6ID 代码和锁定机制 (401)20.6.1MCU DEVICE ID编码 (401)20.6.2TMC TAP (401)20.6.3Cortex-M3 TAP (401)20.6.4Cortex-M3 JEDEC-106 ID代码 (401)20.7JTAG调试端口 (402)20.8SW调试端口 (403)20.8.1SW协议介绍 (403)20.8.2SW协议序列 (403)20.8.3SW-DP状态机(Reset, idle states, ID code) (404)20.8.4DP和AP读/写访问 (404)20.8.5SW-DP寄存器 (405)20.8.6SW-AP寄存器 (405)20.9对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口) (405)20.10内核调试 (406)20.11调试器主机在系统复位下的连接能力 (407)20.12FPB (Flash patch breakpoint) (407)20.13DWT(data watchpoint trigger) (407)20.14ITM (instrumentation trace macrocell) (408)20.14.1概述 (408)20.14.2时间戳包,同步和溢出包 (408)20.15MCU调试模块(MCUDBG) (409)20.15.1低功耗模式的调试支持 (409)20.15.2支持定时器和看门狗和bxCAN的调试 (409)20.15.3调试MCU配置寄存器 (410)20.16TPIU (trace port interface unit) (411)20.16.1导言 (411)20.16.2跟踪引脚分配 (412)20.16.3TPUI格式器 (414)20.16.4TPUI帧异步包 (414)20.16.5同步帧包的发送 (415)20.16.6同步模式 (415)20.16.7异步模式 (415)20.16.8TRACECLKIN在STM32F10x内部的连接 (415)20.16.9TPIU寄存器 (416)20.16.10配置的例子 (416)20.17DBG寄存器地址映象 (417)STM32F10x参考手册第一版文档中的约定1 文档中的约定1.1 寄存器描述中使用的缩写列表在对寄存器的描述中使用了下列缩写:read / write (rw) 软件能读写此位。

STM32F10x参考手册参考手册参考手册参考手册

关于如何进入停止模式,详见表 3-4。 在停止模式下,通过设置电源控制寄存器(PWR_CR)的 LPDS 位使内部调节器进入低功耗 模式,能够降低更多的功耗。

如果正在进行 Flash 编程,直到对内存访问完成,系统才进入停止模式。 如果正在进行对 APB 的访问,直到对 APB 访问完成,系统才进入停止模式。 可以通过对独立的控制位进行编程,可选择以下功能:

表3-4 停止模式

进入

退出 唤醒延时

在以下条件下执行WFI或WFE指令: – 设置Cortex-M3系统控制寄存器中的SLEEPDEEP位 – 清除电源控制寄存器(PWR_CR)中的PDDS位 – 通过设置PWR_CR中LPDS位选择电压调节器的模式 注:为了进入停止模式,所有的外部中断的请求位(挂起寄存器(EXTI_PR))和RTC的闹 钟标志都必须被清除,否则停止模式的进入流程将会被跳过,程序继续运行。

STM32F10x 参考手册

第一版

电源控制(PWR)

3 电源控制(PWR)

3.1 电源

STM32 的工作电压(VDD)为 2.0~3.6V。通过内置的电压调节器提供所需的 1.8V 电源。 当主电源 VDD 掉电后,通过 VBAT 脚为实时时钟(RTC)和备份寄存器提供电源。

3.1.1

图3-1 电源框图 独立的 A/D 转换器供电和参考电压

如果应用中没有使用外部电池,VBAT 必须连接到 VDD 引脚上。

注意:在 VDD 上升阶段(tRSTTEMPO),VBAT 和 VDD 之间的电源开关仍会保持连接在 VBAT。当 VDD 快速上升且达 到稳定状态,当 VBAT 低于 VDD−0.6V 时,电流通过 VDD 和 VBAT 之间的二极管流入到 VBAT。关于 tRSTTEMPO 可参考数据手册中的相关部分。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AN3127Application noteCEC networkingusing STM32F100xx value line microcontrollersIntroductionSTM32F100xx value line microcontrollers feature a high-definition multimedia interfaceconsumer electronics control (HDMI™-CEC) controller peripheral that supports the HDMI-CEC v1.3a protocol. The HDMI-CEC controller provides a hardware support of this protocol,and it supports the whole set of features offered with CEC devices.This application note describes the CEC protocol software and hardware implementationbased on the HDMI-CEC controller. A real application example is also provided to illustratethe software implementation.October 2010Doc ID 16896 Rev 21/36Contents AN3127Contents1High-definition multimedia interface, consumerelectronics control (HDMI-CEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71.1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71.2Frame description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71.3Bit timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81.4Device connectivity and addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91.4.1CEC communication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91.4.2Enhanced DDC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101.4.3Hot plug detect (HPD) signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111.4.4Physical address discovery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111.4.5Discovery algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.4.6Logical addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131.4.7Logical address allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131.5STM32F100xx’s HDMI-CEC controller . . . . . . . . . . . . . . . . . . . . . . . . . . . 141.5.1Main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151.5.2HDMI-CEC advanced features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162Hardware environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182.1HDMI connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182.1.1I2C bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192.2Hardware connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223Firmware description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233.1Package directories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233.2Firmware architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244Value line evaluation board CEC demonstration . . . . . . . . . . . . . . . . . 274.1CEC demonstration overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274.2Device type selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294.3Physical address discovery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294.4Logical address allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294.5Checking the connected devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304.6Displaying CEC send/receive information on the LCD . . . . . . . . . . . . . . . 30 2/36Doc ID 16896 Rev 2AN3127Contents4.6.1Receive information subscreen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 314.6.2Send information subscreen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 5Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 6Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35Doc ID 16896 Rev 23/36List of tables AN3127 List of tablesTable 1.Logical addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Table 2.HDMI connector pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Table 3.STM32F100xx and HDMI-CEC connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table 4.High-level functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Table 5.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 4/36Doc ID 16896 Rev 2AN3127List of figures List of figuresFigure 1.CEC frame format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 2.Message structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 3.Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 4.Bit timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5.Follower acknowledge (ACK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 6.CEC and DDC line connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7.Addresses within a HDMI cluster . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 8.Physical address discovery algorithm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 9.System exits Stop mode when data reception starts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 10.HDMI cable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 11.Application schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 12.Electrical schematic proposal for STM32100B-EVAL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 13.Electrical schematic proposal for STM32100E-EVAL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 14.Example of a hardware connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 15.Package directory structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 16.Firmware architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 17.CEC demonstration flowchart. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Figure 18.Device type selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Figure 19.Physical and logical addresses display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Figure 20.CEC menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Figure 21.Receive flowchart. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Figure 22.Receive information subscreen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Figure 23.Send flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Figure 24.Select CEC command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33Doc ID 16896 Rev 25/36AN3127Glossary of termsBroadcast message: a message sent to logical address 15 that all devices are expected toreceive.Destination: the target device for a CEC message.Follower: a device that has just received a CEC message and is required to respond to it.Initiator: the device that is sending, or has just sent, a CEC message and, if appropriate, iswaiting for a follower to respond.Logical address: a unique address assigned to each device.Menu-providing device: a non-display device that may render a menu on TV.Playback device: a device that has the ability to play media, like a DVD player.Recording device: a device that has the ability to record a source such as an internal tuneror an external connection.Source device: a device that is currently providing an AV stream via HDMI.Tuner device: a device that contains a tuner, e.g. an STB (set-top box) or a recordingdevice.TV: a device with a HDMI input that has the ability to display the input HDMI signal.Generally it has no HDMI output.CEC: consumer electronics control.DDC: display data channel.E-DDC: enhanced display data channel.EDID: extended display identification data.E-EDID: enhanced extended display identification data.HDMI: high-definition multimedia Interface.(HDMI) source: a device with a HDMI output.(HDMI) sink: a device with a HDMI input.6/36Doc ID 16896 Rev 21 High-definition multimedia interface, consumerelectronics control (HDMI-CEC)1.1 IntroductionConsumer electronics control (CEC) is the appendix supplement 1 to the HDMI (high-definition multimedia interface) standard.It is a protocol that provides high-level control functions between all of the variousaudiovisual products in a given environment. It is specified to operate at low speeds withminimum processing and memory overhead.For more details, refer to the high-definition multimedia interface specification available from.description1.2 FrameThe CEC bus is a single-wire protocol that can connect up to 10 audiovisual devices throughstandard HDMI cabling.All transactions on the CEC line consist of an initiator and one or more followers. Theinitiator is responsible for sending the message structure and the data. The follower is therecipient of any data and is responsible for setting any acknowledgement bits.A message is conveyed in a single frame that consists of a start bit followed by a headerblock and, optionally, an opcode and a variable number of operand blocks. Figure1 shows aCEC frame format.Doc ID 16896 Rev 27/368/36Doc ID 16896 Rev 2Figure 3.BlocksAll these blocks are made of an 8-bit payload (most significant bit transmitted first) followedby an end-of-message (EOM) bit and an acknowledge (ACK) bit.The EOM bit is set in the last block of a message and kept cleared in all others. If a messagecontains additional blocks after the EOM, these blocks should be ignored. The EOM bit maybe set in the header block to “ping” other devices and make sure that they are active.The acknowledge bit is always brought to high impedance by the initiator. It can therefore bedriven low by either the follower that has read its own address in the header, or the followerthat needs to reject a broadcast message.The header consists of the source logical address field, and the destination logical addressfield. Note that the address 0xF is specially used for broadcast messages.1.3 Bit timingThe format of the start bit is unique and identifies the start of a message. It should bevalidated by its low duration and its total duration.All remaining data bits in the message, after the start bit, have a consistent timing. The high-to-low transition at the end of the data bit is the start of the next data bit except for the finalbit where the CEC line remains high.Figure 4 shows the timings of the start bit and the different data bits.%/-!#+$%34).!4)/.; =).)4)!4/2; =(EADER BLOCK %/-!#+$!4!; =/PCODE /PERAND BLOCK AIDoc ID 16896 Rev 29/36CEC Figure 5 shows an example bit with both initiator and follower where the follower mayassert the bit to logical 0 to acknowledge a data block. The initiator outputs a logical 1, thusallowing the follower to change the CEC state by pulling the control line low for the durationof the safe sample period.1.4 Device connectivity and addressing1.4.1 CEC communicationBy definition the HDMI system architecture consists of sources and sinks. A given device may have one or more HDMI input(s) and output(s). Each HDMI input on the device shouldfollow all the rules for a HDMI sink and each HDMI output should follow all the rules for aHDMI source.The DDC is used for configuration and status exchange between a single source and asingle sink. The optional CEC protocol provides high-level control functions between all ofthe various audiovisual products in a user’s environment.Figure 6.CEC and DDC line connectionsFigure 7.Addresses within a HDMI clusterDDC1.4.2 EnhancedThe enhanced DDC described in this section is defined in VESA “ENHANCED DISPLAYDATA CHANNEL STANDARD Version 1 (September 2, 1999)”. All sinks are required tosupport these enhanced DDC features. If the E-EDID structure of a sink is longer than 256bytes, it should support the segment pointer.TimingData is synchronized with the SCL signal and timing should comply with the Standard Modeof the I2C specification (100kHz maximum clock rate).The I2C bus is a standard two-wire (clock and data) serial databus protocol. Refer to the I2Cspecification for details.Note that a HDMI sink may hold off the DDC transaction by stretching the SCL line duringthe SCL-low period following the Acknowledge bit as permitted by the I2C specification. AllHDMI sources should delay the DDC transaction while the SCL line is being held low.Data transfer protocolsThe source should use I2C commands to read information from a sink’s E-EDID with a slaveaddress.In Enhanced DDC, a segment pointer is used to address the E-EDID outside the 256 bytesnormally addressable by the 0xA0/0xA1 addresses. The Enhanced DDC protocol sets thesegment pointer before the remainder of the DDC command.10/36Doc ID 16896 Rev 2Segment pointerEnhanced DDC allows access to up to 32 Kbytes of data. This is accomplished using acombination of the 0xA0/0xA1 address pair and a segment pointer. For each value of thesegment pointer, 256 bytes of data are available at the 0xA0/0xA1 address pair. Anunspecified segment pointer references the same data as when the segment pointer is zero.Each successive value of the segment pointer allows access to the next two blocks of E-EDID (128 bytes each). The value of the segment pointer register cannot be read since it isreset at the completion of each command.Enhanced DDC sinkThe sink should be Enhanced DDC read compliant.The sink should be capable of responding with EDID 1.3 data and up to 255 extensionblocks, each 128 bytes long (up to 32 Kbytes of E-EDID memory) whenever the hot plugdetect (HPD) signal is asserted.The sink should be capable of providing E-EDID information over the Enhanced DDCchannel whenever the +5V power signal is provided. The information should be availablewithin 20ms after the +5V power signal is provided.Enhanced DDC sourceThe source should use Enhanced DDC protocols.It should be capable of reading EDID 1.3 data at DDC address 0xA0.The source reads Enhanced EDID extension data at DDC address 0xA0 using segmentpointer 0x60.1.4.3 Hot plug detect (HPD) signalA HDMI sink should not assert high voltage levels on its HPD pin when the E-EDID is notavailable for reading. This requirement should be fulfilled at all times, even if the sink ispowered off or in standby. The HPD pin may be asserted only when the +5V power linefrom the source is detected. This ensures that the HPD pin is not asserted before the thirdmake of the connector.A source may use a high voltage level HPD signal to initiate the reading of E-EDID data. Itdoes not indicate whether the sink is powered, or whether the HDMI input on the sink isselected or active.A HDMI sink should indicate any change to the contents of the E-EDID by driving a lowvoltage level pulse on the HPD pin. This pulse should last at least 100ms.1.4.4 Physical address discoveryIn order to allow CEC to address specific physical devices, all have a physical address. Thebus connectivity is worked out whenever the hot plug detect (HPD) signal is de-asserted bythe physical address discovery process. That process uses only the DDC/EDID (displaydata channel/extended display identification data) mechanism. Starting from the CEC rootdevice which takes address 0b0000 (normally the TV), all sinks and repeaters, whetherCEC-capable or not, determine the address their source device should take, and make itavailable in the source address field of the EDID vendor-specific data blockDoc ID 16896 Rev 211/36(EDID_EXT_VSDB_B0-1). Thereby, except for the root device, all devices have the physicaladdress stored in the EDID of their connected sink.The physical address of each node is determined through the physical address discoveryprocess. This process is dynamic in that it automatically adjusts physical addresses asrequired as devices are physically or electrically added or removed from the device tree.All sinks and repeaters should perform the steps of physical address discovery andpropagation even if those devices are not CEC-capable. Sources are not required todetermine their own physical address unless they are CEC-capable.All addresses are 4 digits long allowing for a 5-device-deep hierarchy. All are identified in theform of n.n.n.n in the following description.A sink or repeater that is acting as the CEC root device generates its own physical address:0.0.0.0. The source or repeater reads its physical address from the EDID of the connectedsink. The CEC line may be connected to only one HDMI output so a device with multipleHDMI outputs will read its physical address from the EDID on the CEC-connected output.Each sink and repeater is responsible for generating the physical address of all sourcedevices connected to that device by appending a port number onto its own physical addressand placing that value in the EDID for that port.algorithm1.4.5 DiscoveryThe following algorithm is used to allocate the physical address of each device wheneverHPD is de-asserted, or upon power-up:Figure 8.Physical address discovery algorithm$ISABLE ASSERTION OF (0$ TO ALL SOURCE DEVICES)F ) AM #%# ROOT3ET MY?ADDRESS TO%LSE7AIT FOR (0$ FROM SINK1UERY SINK FOR MY?ADDRESS OF MY CONNECTION4HE DEVICE SHALL RETAIN THIS PHYSICAL ADDRESS UNTIL(0$ IS REMOVED OR THE DEVICE IS POWERED OFF%ND IF)F DEVICE HAS CONNECTIONS FOR SOURCE DEVICES THEN,ABEL ALL POSSIBLE CONNECTIONS TO SOURCE DEVICESUNIQUELY STARTING FROM CONNECTION?LABEL TO THENUMBER OF SOURCE INPUT CONNECTIONS)F DEVICE HAS SEPARATE %$)$S FOR EACH SOURCE CONNECTIONTHEN)F MY?ADDRESS ENDS WITH THEN3ET EACH SOURCE?PHYSICAL?ADDRESS TO MY?ADDRESSWITH THE FIRST BEING REPLACED WITHCONNECTION?LABEL%LSE I E BEYOND THE FIFTH LAYER OF THE TREE3ET EACH SOURCE?PHYSICAL?ADDRESS TO & & & &%ND IF%LSE3ET EACH SOURCE?PHYSICAL?ADDRESS TO MY?ADDRESS%ND IF7RITE SOURCE?PHYSICAL?ADDRESS TO ($-) 63$" IN %$)$ FOREACH SOURCE CONNECTION%ND IF!LLOW (0$ TO BE ASSERTED FOR SOURCE DEVICESAI12/36Doc ID 16896 Rev 2Doc ID 16896 Rev 213/36Whenever a new physical address (other than F .F .F .F) is discovered, a CEC device should:●allocate the logical address (see Section 1.4.7: Logical address allocation )●report the association between its logical and physical addresses by broadcasting <Report Physical Address>This process allows any node to create a map of physical connections to logical addresses.1.4.6 L ogical addressingApart from the physical address, each device appearing on the control signal line has aunique logical address. This address defines a device type as well as being a uniqueidentifier. This address is 0 for a TV set with physical address 0b0000 and 14 or even 15otherwise. It is defined in the CEC_OAR register and in the upper nibble of the first byte ofthe transmitted message. All CEC devices therefore have both a physical and a logicaladdress, whereas non-CEC devices only have a physical address.1.4.7 Logical address allocationNote that a logical address should only be allocated when a device has a valid physicaladdress (i.e. not F .F .F .F), at all other times a device should take the ‘Unregistered’ logicaladdress (15).Only the device at physical address 0.0.0.0 may take logical address TV (0). A TV at anyother physical address will take the ‘free use’ (14) address. If address 14 is alreadyallocated it will take the ‘unregistered’ address (15).Table 1.Logical addressesAddress Device0TV1Recording device 12Recording device 23Tuner 14Playback device 15Audio system6Tuner 27Tuner 38Playback device 29Recording device 310Tuner 411Playback device 312Reserved13Reserved14Free use15Unregistered (as initiator address) broadcast (as destinationaddress)Reserved addresses should not be used at present and are reserved for future extensionsto this specification.Where more than one possible logical address is available for the given device type (e.g.Tuner 1, Tuner 2, etc.), an address allocation procedure should be carried out by a newlyconnected device. The device takes the first allocated address for that device type andsends a <Polling Message> to the same address (e.g. Tuner 1 -->Tuner 1). If the <PollingMessage> is not acknowledged, then the device stops the procedure and retains thataddress.If the first address is acknowledged, then the device takes the next address for that devicetype and repeats the process (e.g. Tuner 2 .. Tuner 2). Again, if the message is notacknowledged, the device keeps that address.This procedure continues until all possible ‘type-specific’ addresses have been checked; ifno ‘type-specific’ addresses are available the device should take the unregistered address(15). Note that several physical devices might be sharing this address.A device may lose its logical address when it is disconnected or switched off. However, itmay remember its previous logical address, so that the next time it is connected or switchedon, it can begin the polling process at its previous logical address and try each otherallowable logical address in sequence before taking the unregistered address. For exampleif an STB that was previously allocated address Tuner 2 is reconnected, it would poll Tuner2, Tuner 3, T uner 4 and Tuner 1 before taking the unregistered address.If a device loses its physical address at any time (e.g. it is unplugged) then its logicaladdress should be set to unregistered (15).1.5 STM32F100xx’s HDMI-CEC controllerThe STM32F100xx’s HDMI-CEC controller provides a hardware support of the CECprotocol.14/36Doc ID 16896 Rev 2features1.5.1 Main●Supports HDMI-CEC v1.3a●Supports the whole set of features offered with CEC (devices may use all or only someof these features, depending on functionality):–One touch play - a device may be played and become the active source bypressing a single button.–System standby - enables devices to be set on standby by pressing a singlebutton.–Preset transfer - the presets of a device can be autoconfigured to match those of the TV.–One touch record - used to make recordings by pressing a single button.–Timer programming - any device can program a timer to start/stop audio/video recording.–System information - allows devices to autoconfigure their language and country settings.–Deck control - allows a device to control and interrogate a playback device.–Tuner control - allows a device to control the tuner of another device.–Vendor-specific commands - allow vendor-defined commands to be used.–OSD display - allows a device to display text using the on-screen display of the TV.–Device menu control - allows a device to control the menu of another device.–Routing control - enables control of CEC switches for the streaming of a newsource device.Doc ID 16896 Rev 215/36featuresadvanced1.5.2 HDMI-CECThe STM32 HDMI-CEC controller provides an easy platform to build CEC firmwareapplications:●dedicated address register containing up to 15 CEC device addresses●Programmable high-resolution prescaler (14 bit) to obtain a 50µs time base (HDMIspecification resolution)●advanced arbitration mechanism using SFT (signal free time) and header arbitration●dedicated transmission and reception flags (TBTRF and RBTF) with interrupt capability●error handling in a single dedicated register: bit timing errors, bit period errors,message errors and error bit generation–Tx block transfer finished error (TBTFE)–Line error (LINE)–Block acknowledge error (ACKE)–Start bit error (SBE)–Rx block transfer finished error (RTBFE)–Bit period error (BPE)–Bit timing error (BTE)●error-free mode to allow safe communication with non-tolerant CEC devices. Thismode can be selected using a dedicated configuration bit.●Rx digital filtering●CEC controller built around a flexible state machine to ensure safe communication,switching between the Tx and Rx modes, and easy error handling. There are 6 states:Disabled, Idle, RX, TX, RX_ERROR and TX_ERROR. Please refer to the referencemanual (RM0041) available from for more details.●Wakeup-from-Stop source, with no data loss: the CEC line can be used as a wakeupevent from the Stop mode. The STM32 Wakeup system is fast enough to ensure thatthere is no CEC data loss. CEC data received when the system is in the Stop modecause the system to wake up from the low power mode, and in so doing, allow the CECperipheral to easily retrieve them.16/36Doc ID 16896 Rev 2As the tolerance margin on the start bit is 200µs, the software has to reconfigure the systemclock within this time frame (see Figure9). The system clock reconfiguration is necessary asafter waking up from the Stop mode the CPU starts running on the high-speed internaloscillator (HSI 8MHz).To ensure that there is no data loss while the system is in the wakeup phase from the Stopmode, the following procedures can be selected:●The software can choose to use the system PLL as the system main clock. The PLLsource should be the HSI and not the HSE.●For applications which do not need the full CPU performance, the software can chooseto receive the first message just after waking up from Stop mode at the HSI frequency.In this case, there is no need to reconfigure the system clock after the CPU exits theStop mode. However, just before entering the Stop mode the CEC prescaler should bereprogrammed to be in line with the HSI frequency by:–disabling the CEC peripheral. T o do so, write PE=0 and wait until PE goes low–writing the CEC prescaler register (CEC_PRER = 399)–enabling the CEC peripheral. This is done by writing PE=1.–requesting Stop mode entryNote:1The HSE cannot be used after wakeup from Stop mode as it takes some time to start up, and CEC data would be lost.2Any data sent on the CEC bus cause the device to wake up even if the destination address is not matched.3After the first message is received, the software can restore the initial clock configuration to continue in Run mode or re-enter the Stop mode.Refer to the STM32F100xx reference manual (RM0041) for further details.Doc ID 16896 Rev 217/36。