testbench时钟信号的编写

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

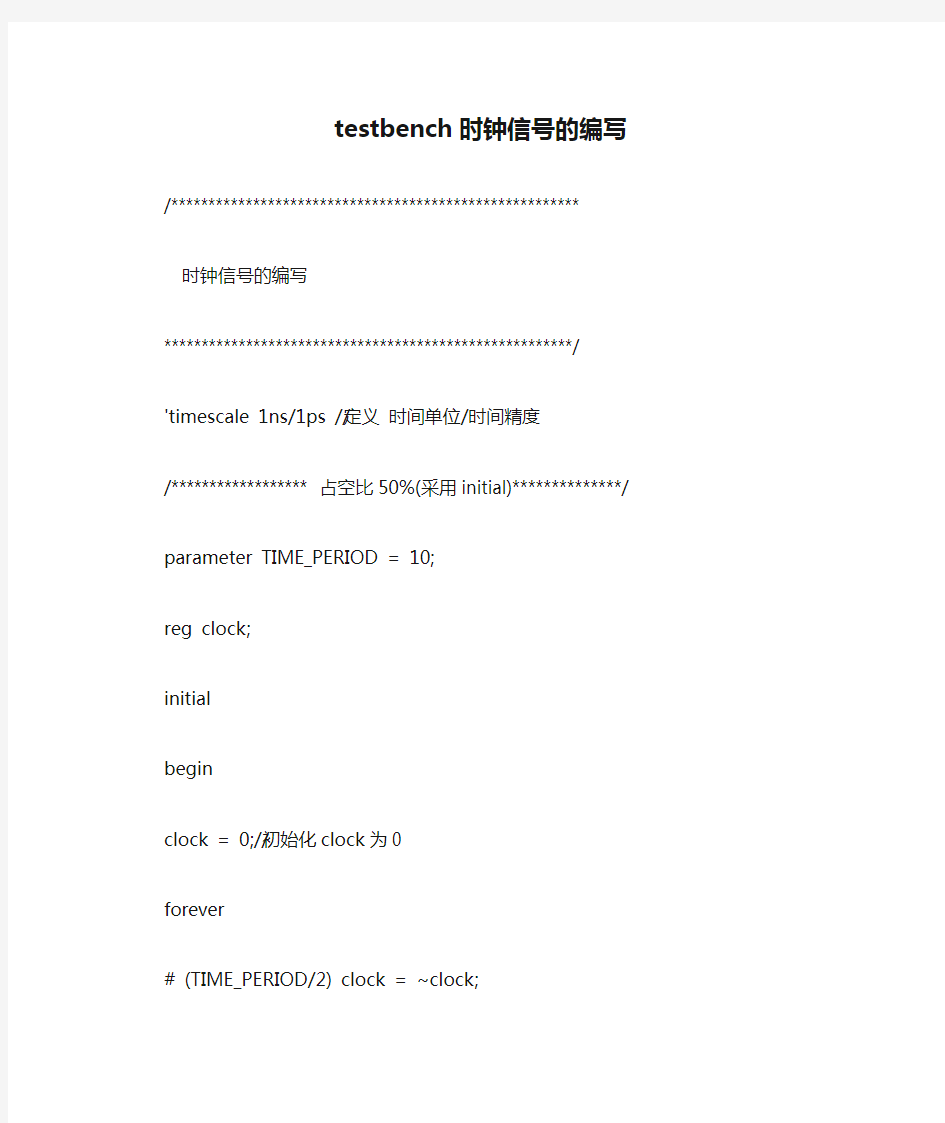

testbench时钟信号的编写

/*************************************************** ****

时钟信号的编写

*************************************************** ****/

'timescale 1ns/1ps //定义时间单位/时间精度

/******************占空比50%(采用

initial)**************/

parameter TIME_PERIOD = 10;

reg clock;

initial

begin

clock = 0;//初始化clock为0

forever

# (TIME_PERIOD/2) clock = ~clock;

end

/******************占空比50%(采用

always)***************/

parameter TIME_PERIOD = 10;

reg clock;

initial

clock = 0;//初始化clock为0

always

# (TIME_PERIOD/2) clock = ~clock;

/******************非50%占空比(采用always)*************/

parameter HI_TIME = 5,

LO_TIME = 10;

reg clock;

always

begin

# HI_TIME clock = 0;

# LO_TIME clock = 1;

end

/***********固定数目时钟占空比50%(采用initial)*********/

parameter PULSE_COUNT = 4,

TIME_PERIOD = 10;

reg clock;

initial

begin

clock = 0;//初始化clock为0

repeat (2*PULSE_COUNT)

# (TIME_PERIOD/2) clock = ~clock;

end

/****************相移时钟信号(采用

always)**************/

parameter HI_TIME = 5,

LO_TIME = 10,

PHASE_SHIFT = 2;

reg absolute_clock;

wire derived_clock;

always

begin

# HI_TIME absolute_clock = 0;

# LO_TIME absolute_clock = 1;

end

assign # PHASE_SHIFT derived_clock = absolute_clock;