数字电路实验报告-数据选择器

实验一四选一数据选择器的设计

实验一四选一数据选择器的设计实验目的:设计并实现一个四选一数据选择器,可以将四个输入信号中的一个作为输出信号进行传递。

实验原理:四选一数据选择器是多路选择器的一种,主要由输入端、控制端和输出端组成。

输入端有四个信号输入线,控制端有两个控制输入线,输出端有一个信号输出线。

通过控制输入线的不同组合,可以选择其中一个输入信号传递到输出端。

实验材料与器件:1.1片74LS153(二选四数据选择器)芯片2.4个开关按钮3.连接线4.电源线5.示波器(可选)实验步骤:1.连接电路:a. 将芯片74LS153的Vcc引脚连接到正极电源线,将GND引脚连接到负极电源线。

b.将芯片的1A、1B、2A、2B四个输入引脚分别连接到四个开关按钮。

c.将芯片的S0、S1两个控制输入引脚分别连接到两个控制开关按钮。

d.将芯片的Y输出引脚连接到输出信号线。

e.将电源线接入电源插座,通电。

2.设置控制输入:a.初始状态下,所有控制输入引脚都为低电平状态。

b.可以通过控制两个开关按钮的开关状态来改变控制输入引脚的电平。

3.输出结果观测:a.打开示波器,将其输入端连接到芯片的输出引脚,设置为观测模式。

b.通过改变控制输入的电平状态,可以选择不同的输入信号进行输出。

c.观察示波器上的输出信号波形,确保输出信号与选择的输入信号一致。

4.实验记录:a.记录不同控制输入状态下的输入信号及输出信号。

b.通过对比观测结果,验证芯片的正常工作。

实验注意事项:1.连接电路时,注意电源接线正确,避免短路或电路损坏。

2.实验过程中操作电路和仪器时,保持手部干燥,并确保安全。

3.实验完成后,关闭电源,将电路和仪器恢复原状,并整理实验记录。

4.若没有示波器,可以通过观察输出信号线连接的LED灯的亮灭来判断输出信号的状态。

实验结果与讨论:在实验中,我们设计并实现了一个四选一数据选择器,并通过改变控制输入的电平状态来选择不同的输入信号进行输出。

通过观察观测结果,我们可以发现当控制输入引脚的电平状态为低-低时,选择1A作为输出;当为低-高时,选择1B作为输出;当为高-低时,选择2A作为输出;当为高-高时,选择2B作为输出。

实验四 数据选择器及应用

实验四数据选择器及应用一、实验目的(1)掌握采用中规模集成器件设计组合逻辑电路的方法。

(2)掌握数据选择器的工作原理。

(3)测定数据选择器的逻辑功能。

(4)设计并验证用数据选择器实现逻辑函数。

二、预习要求(1)掌握数据选择器的工作原理。

(2)掌握用数据选择器实现逻辑函数的设计原则。

(3)片选端E'起什么作用?E'为何值时,选择器正常工作。

(4)如何用卡诺图分离出多余的变量?三、实验器材(1)实验仪器:数字电路实验箱、万用表;(2)实验器件:74LS00、74LS32、74LS153、74LS151;四、实验原理以前所讨论的组合电路设计方法常称“四步法”,即列真值表,写出逻辑函数,简化逻辑函数和画逻辑图。

一般只在使用小规模集成器件时使用。

在中、大规模集成电路出现之后,逻辑设计方法有很大的改变。

即可用中规模集成器件设计组合逻辑网络。

1. 数据选择器的工作原理在数字信息的传输过程中,有时按要求从多路并行传送的数据中选通一路送到唯一的输出线上,形成总线传输。

这时要用到数据选择器(多路转换器,可简称为MUX),逻辑符号如图4-1(a)所示。

其功能类似于单刀多掷开关,如图4-1(b)所示。

由图4-1(a)看出,数据选择器有n条地址线,2n个输入线,一条输出线。

其功能是根据地址线编码从2n个输入信号中选用一个信号输出。

即可以把它看成二进制编码的可控开关,由编码控制选通信息,如图4-1(b)所示。

(a )数据选择逻辑符号 (b )单刀多掷开关图4-1 数据选择器图4-2是4选1数据选择器。

图中1A 、0A 是地址变量,由地址代码来选择数据通道;0123D D D D 是输入信号;F 是输出信号;E '是使能端或片选端,低电平有效。

当E '为低电平时,数据选择器正常工作;E '为高电平时,数据选择器禁止工作。

数据选择器的功能如表4-1所示。

(a )电路 (b )逻辑符号图4-2 4选1数据选择器表4-1 4选1 MUX 功能表由表4-1可写出输出F 的表达式如下:⎩⎨⎧+++==30120110100''''0D A A D A A D A A D A A F F 时时01='='E E 由表可看出,当1='E 时,输出0F =;当0='E 时,0001=A A 时,0D F =,相当于开关与0D 接通;0101=A A 时,1D F =,相当于开关与1D 接通;1001=A A 时,2D F =,相当于开关与2D 接通;1101=A A 时,3D F =,相当于开关与3D 接通。

山东交通学院译码器和数据选择器实验报告

实验十译码器和数据选择器一、实验目的1、熟悉集成译码器。

2、了解集成译码器应用。

二、实验原理译码器是将给定代码译成相应状态的电路。

双2-4线集成变量译码器74LS139如图10-1所示。

每个2-4线译码器有两个输入端(A、B)和四个输出端(Y0、Y1、Y2、Y3)。

两个输入端可以输入四种数码,即00、01、10、11,对应的四种输出状态是0111、1011、1101、1110。

G为使能端,当G=0时,译码器能正常工作,当G=1时,不能工作,输出端全部为高电平(即“1”)。

数据选择器有多个输入,一个输出。

其功能类似单刀多掷开关,故又称多路开关(MUX)。

在控制端的作用下可从多路并行数据中选择一路送输出端。

双4选1数据选择器74LS153如图10-2所示。

以其中的一个数据选择器为例,C0、C1、C2、C3为输入端,可同时输入四种不同的数据(信号),Y为被选中的数据的输出端,G为使能端(低电平时工作),A、B为选择控制端。

设四个输入端的输入信号分别为C0、C1、C2、C3则其功能如表10-1所示。

三、实验仪器及材料1、双踪示波器2、器件74LS139 双2—4线译码器 1片74LS153 双4选1数据器 1片74LS00 二输入端四与非门 1片四、实验预习要求1、复习有关译码器和数据选择器的原理。

2、根据实验任务,画出所需的实验线路及记录表格。

五、实验内容及步骤1、译码器功能测试将74LS139译码器按图10-1,接线,按表10-2输入电平分别置位,填写输出状态表图10-1 74LS139译码器表10-22、译码器转换将双2—4线译码器转换为3—8线译码器。

(1)画出转换电路图。

(2)在实验仪上接线并验证设计是否正确。

(3)设计并填写该3—8线译码器功能表,画出输入、输出波形。

3、数据选择器的测试及应用将双4选1数据选择器74LS153参照图10-2接线,测试其功能并填写功能表。

(1)将选择端1(G)、2(B)、14(A)脚接逻辑电平开关;(2)将实验仪脉冲信号源中固定连续脉冲4个不同频率的信号接到数据选择器4个输入端:3(250KHz)、4(100KHz)、5(10KHz)、6(1KHz);将选择端置位,使输出端7(1Y)接示波器,可分别观察到4种不同频率脉冲信号。

实验二、数据选择器及其应用

实验二 数据选择器及应用一、实验目的1、掌握数据选择器的工作原理及逻辑功能。

2、熟悉74LS153和74LS151的引脚排列和测试方法。

3、学习用数据选择器构成组合逻辑电路的方法。

二、预习要求1、复习组合逻辑电路的分析方法及设计方法。

2、了解数据选择器的原理及功能。

3、阅读本实验的实验原理和测试方法。

三、实验内容1、中规模集成芯片74LS153、74LS151逻辑功能的验证。

2、用双四选一数据选择器74LS153实现八选一数据选择器。

3、用八选一数据选择器74LS151实现函数电路。

4、自行设计题目。

四、实验原理与测试方法数据选择器又称多路转换器或多路开关,其功能是把多个通道的数据传送到唯一的公共数据通道上去。

类似一个多掷开关,如图2.1所示。

图中有四路数据D 0 ~ D 3通过选择控制信号A 1、A 0(地址码)从四路数据中选中某一路数据送至输出端Y 。

一个n 个地址端的数据选择器,具有2n 个数据选择 功能。

例如:数据选择器(74LS153),n = 2,可完成四选一的功能;数据选择器(74LS151),n = 3,可完成八选一的功能。

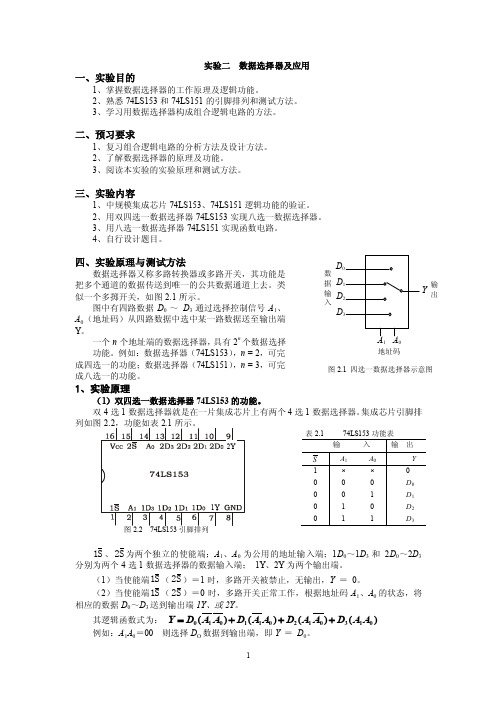

1、实验原理(1)双四选一数据选择器74LS153的功能。

双4选1数据选择器就是在一片集成芯片上有两个4选1数据选择器。

集成芯片引脚排S 1、S 2为两个独立的使能端;A 1、A 0为公用的地址输入端;1D 0~1D 3和2D 0~2D 3分别为两个4选1数据选择器的数据输入端; 1Y 、2Y 为两个输出端。

(1)当使能端S 1(S 2)=1时,多路开关被禁止,无输出,Y = 0。

(2)当使能端S 1(S 2)=0时,多路开关正常工作,根据地址码A 1、A 0的状态,将相应的数据D 0~D 3送到输出端1Y 、或2Y 。

其逻辑函数式为: )()()()(013012011010A A D A A D A A D A A D Y +++= 例如:A 1A 0=00 则选择D O 数据到输出端,即Y = D 0。

数据选择器实验报告

数据选择器实验报告Company Document number:WUUT-WUUY-WBBGB-BWYTT-1982GT实验三 数据选择器实验人员: 班号: 学号:一、实验目的(1) 熟悉并掌握数据选择器的功能。

(2) 用双4选1数据选择器74LS153设计出一个16选1的数据选择器。

(3) 用双4选1数据选择器74LS153 设计出一个全加法器。

二、实验设备数字电路实验箱,74LS00,74LS153。

三、实验内容(1) 测试双4选1数据选择器74LS153的逻辑功能。

74LS153含有两个4选1数据选择器,其中A 0和A 1为芯片的公共地址输入端,V cc 和GND 分别为芯片的公共电源端和接地端。

Figure1为其管脚图:Figure 11Q =A 1A 0̅̅̅̅̅̅̅1D 0+A 1̅̅̅A 0?1D 1+A 1A 0̅̅̅?1D 2+A 1A 0?1D 32Q =A 1A 0̅̅̅̅̅̅̅2D 0+A 1̅̅̅A 0?2D 1+A 1A 0̅̅̅?2D 2+A 1A 0?2D 3按下图连接电路:Figure 2(2) 设某一导弹发射控制机构有两名司令员A 、B 和两名操作员C 、D ,只有当两名司令员均同意发射导弹攻击目标且有操作员操作,则发射导弹F 。

利用所给的实验仪器设计出一个符合上述要求的16选1数据选择器,并用数字电路实验箱上的小灯和开关组合表达实验结果。

思路:由于本实验需要有四个地址输入端来选中16个数据输入端的地址之中的一个,进而实现选择该数据输入端中的数据的功能,即16选1。

而公共的A 0、A 1两个地址输入端和S使能端(用于片选,已达到分片工作的目的,进而扩展了一位输入)一共可以提供三个地址输入端,故需要采用降维的方法,将一个地址输入隐藏到一个数据输入端D x中。

本实验可以降一维,也可以降两位。

由于两位比较复杂,本实验选择使用降一维的方式。

做法:画出如应用题中实现所需功能的卡诺图:将D降到数据输入端中。

7数据选择器应用实验

数字电路-07数据选择器应用实验一.实验目的1.掌握数据选择器的逻辑功能和使用方法。

2.学习用数据选择器进行组合逻辑电路设计的方法。

二.实验原理中规模集成器件(MSI)的大量出现使得许多逻辑电路可以直接选用相应功能的集成器件实现。

这样即省去繁琐的逻辑化简和综合步骤、减少人为因素造成的设计错误,又能使电路系统结构简单,体积小,连线少,功能强,同时稳定性和可靠性也大大提高。

当采用SSI实现组合逻辑电路时,逻辑设计和元件选择是相互独立的。

设计过程是按一定的方法和步骤,在对功能要求进行逻辑抽象的基础上,通过函数化简,得到一种实现给定功能的最经济的设计方案。

而在MSI进行组合逻辑设计时,必须了解所选用集成器件的逻辑功能、外部引脚电气性能以及使用方法,充分发挥器件本身的控制功能。

做到使用最少的集成器件,获得最佳的、符合技术指标的设计方案。

数据选择器是数字系统中常用的中规模集成电路。

它的主要功能是根据地址码的控制,从多路输入数据中选择一路作为输出。

本实验采用中规模集成器件74LS153双4选1数据选择器进行组合逻辑电路设计,图7-1 为74153的引脚排列图。

图7-1 双4选1数据选择器74LS153的引脚排列图74153内部有两个地址码共用的4选1数据选择器。

通过输入不同的地址码A1,A0,可以控制输出Y选择4个输入数据D0~D3中的一个。

7-1 为74153逻辑功能表。

表7-1 双4选1数据选择器74153逻辑功能表根据表7-1可以写出函数输出表达式:11301201101001)1111(S D A A D A A D A A D A A Y +++=22301201101001)2222(S D A A D A A D A A D A A Y +++=其中D 0~D 3为4路数据输入端。

A1A0为输入地址代码,可组成四种状态:“00”,“01”,“10”,“11”,依次对应选择D 0,D 1,D 2,和D 3。

实验三选数据选择器实验报告

实验三选数据选择器实验报告实验三、八选一数据选择器一、实验目的:1.熟悉Quartus116.0软件的使用和FPGA设计流程2.用VHDL语言进行八选一数据选择器的设计二、实验步骤:一建立文件夹:在D盘“_ngmng”的文件夹下建立一个名为“choce8”的文件夹。

二建立新工程1.双击桌面上Quartus6.0的图标,启动该软件。

2.通过Fle=NewProjectWzard菜单命令启动新项目向导。

在随后弹出的对话框上点击Ne_t按钮,在Whatstheworkngdrectoryforthsproject栏目中设定新项目所使用的路径:D:_ngmngchoce8;在Whatsthenameofthsproject栏目中输入新项目的名字:choce8,点击Ne_t按钮。

在下一个出现的对话框中继续点击Ne_t,跳过这步。

3.为本项目指定目标器件:选择器件系列为ACE_1K,选择具体器件为EP1K30TC144FlowSunrTary1或LBRARYEEEjU5EEEE.STDLOGC1164stated。

点击确定按钮,确认设置。

回到Setng对话框,点击OK按钮。

3.在这些均设置好后,选择Processng 菜单下,点击StartComplaton命令,开始再一次编译我们的项目。

编译结束后,点击“确定”按钮。

七与配置1.可编程器件通过专用电缆和计算机相连,使用命Tools=Programmer打开编程模块窗口,目标器件名和编程文件名必须正确地显示在该窗口中。

2.回到编程器窗口,选中program/confgure,再点击Start启动编程。

3成功后,在试验箱中进行试验,可观察到实验结果。

三、实验感想在这次的试验中,因为是第三次使用Quartus6.0做实验,所以,对于实验的步骤和流程比较熟悉了,这次试验是根据二选一和四选一数据选择器来改编八选一数据选择器,但是,在改编VHDL语言程序的过程中,遇到的一个问题就是由于输入法没有调整到英文状态,导致程序无法正常进行编译,后面检查后就修正过来了。

译码器和数据选择器

实验四 译码器及其应用一、实验目的1.掌握中规模集成译码器的逻辑功能和使用方法2.熟悉数码管的使用二、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器可分为通用译码器和显示译码器两类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n 个输入变量,则有2n 个不同的组合状态,就有2n 个输出端供其使用。

而每一个输出所代表的函数对应于n 个输入变量的最小项。

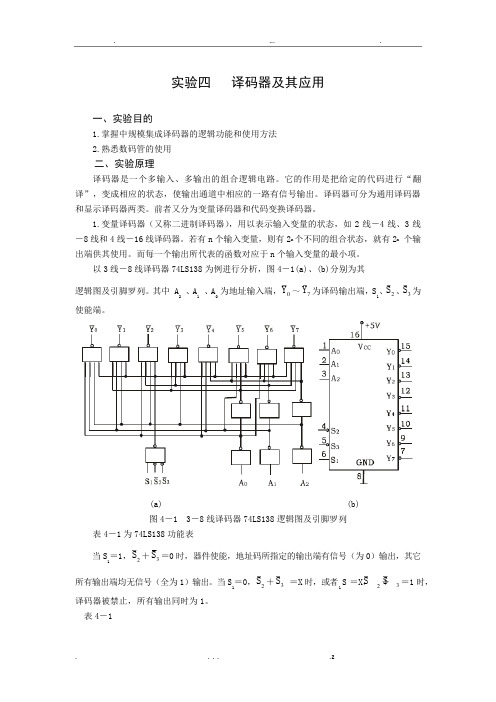

以3线-8线译码器74LS138为例进行分析,图4-1(a)、(b)分别为其逻辑图及引脚罗列。

其中 A 2 、A 1 、A 0为地址输入端,0Y ~7Y 为译码输出端,S 1、2S 、3S 为使能端。

(a) (b)图4-1 3-8线译码器74LS138逻辑图及引脚罗列表4-1为74LS138功能表当S 1=1,2S +3S =0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S 1=0,2S +3S =X 时,或者 S 1=X,2S +3S=1时,译码器被禁止,所有输出同时为1。

表4-1输 入输 出S 1 2S +3S A 2A 1 A 0 0Y1Y2Y3Y 4Y5Y6Y 7Y1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 0 × × × × 1 1 1 1 1 1 1 1 × 1×××11111111二进制译码器实际上也是负脉冲输出的脉冲分配器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三数据选择器

验证74LS153的逻辑功能仿真电路图如下所示:

当S1̅=1时,Y1=0;当S2̅=1时,Y2=0。

二、将74LS153扩展为八选一数据选择器,并测试实现其功能。

仿真电路图如下所示:

真值表为:

三、 利用上题所扩展的八路选择器设计一个8421BCD 非法码检测

电路,当输入端为非法码组时,输出为1,否则为0。

根据题意,当DCBA 输入为0000~1001时,Y 为0;当DCBA 输入为1010~1111时,Y 为1。

由真值表可得,当BCD 相同时,A 的取值不影响Y 的输出结果。

故可得 Y =D 5DC B +D 6DCB ̅+D 7DCB ,所以D 0=D 1=D 2=D 3=D 4=0,D 5=D 6=D 7=1。

真值表为:

仿真电路图如下所示:

当DCBA 输入为0000~1001时,Y 的输出为0

当DCBA 输入为1010~1111时,Y 的输出为1

四、 利用扩展的八路选择器实现函数Y =A B C +BC

̅̅̅̅+AB ̅C Y =A B C +BC ̅̅̅̅+AB ̅C =A B C +A B C

̅̅̅̅+ABC ̅̅̅̅+AB ̅C 所以D 0=D 3=D 4=D 5=1,D 1=D 2=D 6=D 7=1 仿真电路图如下所示:

真值表为:。