74151 TTL 8选1数据选择器

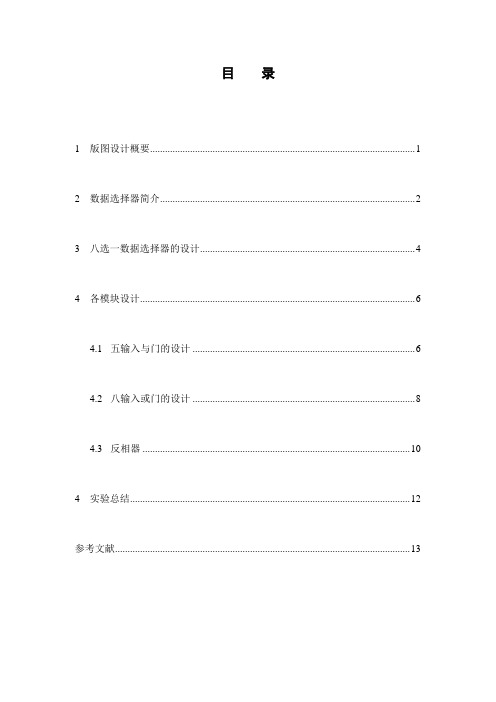

数字电子技术基础实验-8选1数据选择器74LS151

8选1数据选择器74LS151简介74LS151是一种典型的集成电路数据选择器,为互补输出的8选1数据选择器,它有3个地址输入端CBA,可选择D0~D7 8个数据源,具有两个互补输出端,同相输出端Y和反相输出端W。

74LS151引脚图选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。

(1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。

(2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。

如:CBA=000,则选择D0数据到输出端,即Y=D0。

如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。

74LS151功能表数据选择器的应用数据选择器除实现有选择的传送数据外,还有其他用途,下面介绍几种典型应用。

(1)逻辑函数产生器从74LS151的逻辑图可以看出,当使能端G=0时,Y是C、B、A和输入数据D0~D7的与或函数。

式中mi是C、B、A构成的最小项。

显然。

当Di=1时,其对应的最小项mi在与或表达式中出现,当Di=0时,对应的最小项就不出现。

利用这一点,不难实现组合逻辑函数。

已知逻辑函数,利用数据选择器构成函数产生器的过程是,将函数变换成最小项表达式,根据最小项表达式确定各数据输入端的二元常量。

将数据选择器的地址信号C、B、A作为函数的输入变量,数据输入D0~D7,作为控制信号,控制各最小项在输出逻辑函数中是否出现,使能端G始终保持低电平,这样8选1数据选择器就成为一个3变量的函数产生器。

例1 试用8选1数据选择器74LS151产生逻辑函数解:把式变换成最小项表达式:显然D3、D5、D6、D7,都应该等于1,而式中没有出现的最小项m0,m1,m2,m4的控制变量D0、D1、D2、D4都应该等于0,由此可画出该逻辑函数产生器的逻辑图:、例2 试用与上例相同的8选1数据选择器产生从表中可以看出,凡使L值为1的那些最小项,其控制变量应该等于1,即D1、D2、D4、D7等于1(对应XYZ:001、010、100、111),其他控制变量均等于0。

74HC1518选1数据选择器

74HC151 8选1数据选择器国际通用符号54/74151A,54/74S151,54/74LS151,54/74AS151,54/74ALS151,54/74F151,54/74HC151,54/74AC151,54/74HCT151,54/74ACT151,74FC151,74FCT15174HC153 双4选1数据选择器国际通用符号54/74153,54/74L153,54/74LS153,54/74S153,54/74ALS153,54/74F153,54/74HC153,54/74AC153,54/74HCT153,54/74ACT153,74FCT153,74FCT2153,54/74AS15374HC160 可预置BCD计数器(异步清除)国际通用符号54/74160,54/74LS160A,54/74AS160,54/74ALS160A,54/74F160,54/74HC160,54/74AC160,54/74HCT160,54/74ACT160160为十进制计数器,直接清除。

两个高电平有效允许输入P和T及动态进位输出使计数器易于级联;T允许动态进位输出;在允许态若计数器处于最大值的状态,动态进位输出变为高电平;对于160动态进位输出QD=。

TQAQBQC74HC161 可预置四位二进制计数器(异步清除)国际通用符号54/74161,54/74LS161A,54/74AS161,54/74ALS161A,54/74F161,54/74HC161,54/74AC161,54/74HCT161,54/74ACT161,54/74FCT161,74FCT2161161为二进制计数器,直接清除。

两个高电平有效允许输入P和T及动态进位输出使计数器易于级联;T允许动态进位输出;在允许态若计数器处于最大值的状态,动态进位输出变为高电平;对于161动态进位输出=TQATQBTQCTQD。

74HC162 可预置BCD计数器(同步清除)国际通用符号54/74162,54/74S162,54/74LS162A,54/74AS162,54/74ALS162A,54/74F162,54/74HC(T)162,40162,14162,54/74AC162,54/74HCT162,54/74ACT162162为十进制计数器,同步清除。

8选1数据选择器74LS151

8选1数据选择器74LS15174LS151为互补输出的8选1数据选择器,引脚排列如图所示,功能见表。

选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。

(1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。

838电子(2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。

如:CBA=000,则选择D0数据到输出端,即Y=D0。

新艺图库如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。

工作原理ab126计算公式大全74LS151功能表:在数字系统中,往往要求将并行输出的数据转换成串行输出,用数据选择器很容易完成这种转换。

例如将四位的并行数据送到四选一数据选择器的数据端上,然后在A1,A0地址输入端周期性顺序给出00 01 10 11,则在输出端将输出串行数据,不断重复。

数据选择器除了能从多路数据中选择输出信号外,还可以实现并行数据到串行数据的转换,作函数发生器等。

1.逻辑特性(1) 逻辑功能:从多路输入中选中某一路送至输出端,输出对输入的选择受选择控制量控制。

通常,对于一个具有2n路输入和一路输出的多路选择器有n个选择控制变量,控制变量的每种取值组合对应选中一路输入送至输出。

(2) 构成思想: 多路选择器的构成思想相当于一个单刀多掷开关,即数据选择器的原理o74LS151为互补输出的8选1数据选择器,引脚排列如图3-2,功能如表3-1。

选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Q,为使能端,低电平有效。

图74LS151引脚排列使能端=1时,不论A2~A0状态如何,均无输出(Q=0,=1),多路开关被禁止。

1)使能端=0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择D0~D7中某一个通道的数据输送到输出端Q。

74sl151(详细)

8选1数据选择器74LS151(151 为互补输出的8 选1 数据选择器)74LS151为互补输出的8选1数据选择器,引脚排列如图所示,功能见表。

引脚,又叫管脚,英文叫Pin。

就是从集成电路(芯片)内部电路引出与外围电路的接线,所有的引脚就构成了这块芯片的接口数据选择端(ABC)按二进制译码(译码是编码的逆过程,同时去掉比特流在传播过程中混入的噪声。

利用译码表把文字译成一组组数码或用译码表将代表某一项信息的一系列信号译成文字的过程称之为译码。

),以从8 个数据(D0---D7)中选取1 个所需的数据。

只有在选通端STROBE 为低电平时才可选择数据。

151 有互补输出端(Y、W),Y 输出原码,W 输出反码。

选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。

(就是说能使芯片工作的端口,如果使能端开,芯片就能工作,一般你看表示使能端的符号,如果上面有一横就是低电平有效(即如果使能端为低电平,芯片就能工作),反之就是高电平有效。

)又叫使能输入端(enable),它是芯片的一个输入引脚,或者电路的一个输入端口,只有该引脚激活,芯片才能工作,通常情况下为高电平有效,若符号上面有一横,则表示低电平有效。

多路选择器多路选择器是数据选择器的别称。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关。

有4选1数据选择器、8选1数据选择器(型号为74151、74LS151、74251、74LS151)、16选1数据选择器(可以用两片74151连接起来构成)等之分。

多路选择器还包括总线的多路选择,模拟信号的多路选择等,相应的器件也有不同的特性和使用方法.具体可以查找相关网站数据选择器的定义及功能 数据选择是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去。

实现数据选择功能的逻辑电路称为数据选择器→→→→数据输出n位通道选择信号I I I 012n -1数据选择器示意图4选1数据选择器功能表 输 入输出使能地 址G B A Y100001100××011D D D D 0123(1)使能端G =1时,不论C ~A 状态如何,均无输出(Y =0,W =1),多路开关被禁止。

2.8选1数据选择器74LS151_数字电子技术_[共2页]

![2.8选1数据选择器74LS151_数字电子技术_[共2页]](https://img.taocdn.com/s3/m/20e790fa2af90242a995e5c4.png)

第4章 组合逻辑电路 77选择变量AB 作为地址变量A 1A 0,则剩下的变量CD 将体现在数据译码器的数据输入端D 0~D 3。

观察卡诺图并按变量AB 组合将卡诺图划分为4个卡诺圈,各卡诺圈所示的函数就是与地址变量A 1A 0各自对应的数据输入,即D 0=C ,D 1=C+D ,3D =C ,2D C D =⊕,其逻辑电路图如图4.4.23所示。

常见的中规模集成数据选择器有双四选一数据选择器74LS153、八选一数据选择器74LS151、十六选一数据选择器74LS150等类型。

1.双4选1数据选择器74LS153双4选1数据选择器74LS153是在一个芯片上集成了两个功能相同的4选1选择器,两个选择器共用地址输入端,但分别有各自的数据输入端和数据输出端,电路引脚如图4.4.24所示,真值表如表4.4.7所示。

图4.4.23 例4.4.5的逻辑电路图 图4.4.24 74LS153引脚图 由真值表4.4.7可以看出,输入选择控制端S 为低电平有效。

S =1时芯片被禁止,输出端Y 为低电平。

S =0时芯片被选中,数据选择器处于正常工作状态,由地址控制端A 1A 0确定从4个输入数据D 3~D 0中选择其中一个作为输出端Y 的输出,此时Y 的逻辑函数表达式为: 100101102103Y=A A D +A A D +A A D +A A D (4.4.5)2.8选1数据选择器74LS1518选1数据选择器74LS151有8个数据输入端D 7~D 0,3个地址输入端A 2A 1A 0,1个输入选择控制端S ,2个互补输出端:同相输出端Y 和反向输出端Y 。

74LS151的逻辑符号图如图4.4.25所示,真值表如表4.4.8所示。

表4.4.7 74LS153真值表图4.4.25 74LS151符号图。

74LS系列IC管脚图大全

74LS390 双十进制计数器

74LS624 压控振荡器

74LS625 压控振荡器

74LS626 压控振荡器

74LS627 压控振荡器

74LS628 压控振荡器

74LS629 压控振荡器

两片74LS283构成的8位加法器

74LS289 64位随机存取存储器

74LS289 64位随机存取存储器

74LS290异步2—5—10进制计数器

74LS290异步2—5—10进制计数器

74LS292 可编程分频器/数字定时器

74LS293 4位二进制计数器

74LS294 16位可编程模块

74LS374 八D触发器(三态同相)

74381

符号

A0 A1 A2 A3

B0 B1 B2 B3

C -1

S0 S1 S2

引脚排列

A 1 1 20 VCC

F0

B1

A2

F1

A0

B2

F2

B0

F3

S0

A3 B3

7 43 81

S1

C -1

S2

P

P

F0

G

G

F1

F3

GND 1 0 1 1 F 2

74LS381算术逻辑单元

74LS181 算术逻辑单元/功能发生器

74LS181 四位算术逻辑运算器

7 4 18 2

G 1 1 16 V cc

P1

P2

G0

G2

P0

C -1

G3

C0

P3

C1

P

G

G ND 8 9 C 2

74LS182先行进位发生器/超前进位产生器

VCC 2Ai 2Bi 2Ci-1 2Ci 2Si VCC2A 2B 2CIn 2COn+1 2F 74LS183 1COn+1 1A 1B 1CIn 1F GND 1Ai 1Bi 1Ci-1 1Ci 1Si 地

74系列芯片功能大全+4000系列的选型说明

74系列芯片功能大全+4000系列的选型说明74与40是所有外围最常用的IC,其中包括SN74HC595 8位移位寄存器/锁存器(即串转并转换)等十分重要的芯片。

7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D驱动器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器SN74LSOO 四2输入与非门SN74LSO2 四2输入与非门SN74LS04 六反相器SN74LS06 六反相缓冲器/驱动器SN74LS08 四2输入与非门SN74LS10 三3输入与非门SN74LS12 三3输入与非门SN74LS14 六反相器.斯密特触发SN74LS16 六反相缓冲器/触发器SN74LS20 双4输入与门SN74LS22 双4输入与门SN74LS26 四2输入与非门SN74LS28 四输入端或非缓冲器SN74LS32 四2输入或门SN74LS37 四输入端与非缓冲器SN74LS40 四输入端与非缓冲器SN74LS47 BCD-七段译码驱动器SN74LS49 BCD-七段译码驱动器SN74LS54 四输入与或非门SN74LS63 六电流读出接口门SN74LS74 双D触发器SN74LS76 双J-K触发器SN74LS83 双J-K触发器SN74LS86 四2输入异或门SN74LS90 4位十进制波动计数器SN74LS92 12分频计数器SN74LS96 5位移位寄存器SN74LS109 正沿触发双J-K触发器SN74LS113 双J-K负沿触发器SN74LS121 单稳态多谐振荡器SN74LS123 双稳态多谐振荡器SN74LS125 三态缓冲器SN74LS131 3-8线译码器SN74LS137 地址锁存3-8线译码器SN74LS139 双2-4线译码-转换器SN74LS147 10-4线优先编码器SN74LS153 双4选1数据选择器SN74LS155 双2-4线多路分配器SN74LS157 四2选1数据选择器SN74LS160 同步BDC十进制计数器SN74LS162 同步BDC十进制计数器SN74LS164 8位串入并出移位寄存SN74LS166 8位移位寄存器SN74LS169 4位可逆同步计数器SN74LS172 16位多通道寄存器堆SN74LS174 6D型触发器SN74LS176 可预置十进制计数器SN74LS182 超前进位发生器SN74LS189 64位随机存储器SN74LS191 二进制同步可逆计数器SN74LS193 二进制可逆计数器SN74LS195 并行存取移位寄存器SN74LS197 可预置二进制计数器SN74LS238 3-8线译码/多路转换器SN74LS241 八缓冲/驱动/接收器SN74LS243 四总线收发器SN74LS245 八总线收发器SN74LS248 BCD-七段译码驱动器SN74LS251 三态8-1数据选择器SN74LS256 双四位选址锁存器SN74LS258 四2选1数据选择器SN74LS260 双5输入或非门SN74LS266 四2输入异或非门SN74LS275 七位树型乘法器SN74LS279 四R-S触发器SN74LS283 4位二进制全加器SN74LS293 4位二进制计数器SN74LS365 六缓冲器带公用启动器SN74LS367 六总线三态输出缓冲器SN74LS373 8D锁存器SN74LS375 4位双稳锁存器SN74LS386 四2输入异或门SN74LS393 双4位二进制计数器SN74LS574 8位D型触发器SN74LS684 8位数字比较器SN74LSO1 四2输入与非门SN74LS05 六反相器SN74LS07 六缓冲器/驱动器SN74LS09 四2输入与非门SN74LS11 三3输入与非门SN74LS13 三3输入与非门SN74LS15 三3输入与非门SN74LS17 六反相缓冲器/驱动器SN74LS21 双4输入与门SN74LS25 双4输入与门SN74LS27 三3输入与非门SN74LS30 八输入端与非门SN74LS33 四2输入或门SN74LS38 双2输入与非缓冲器SN74LS42 BCD-十进制译码器SN74LS48 BCD-七段译码驱动器SN74LS51 三3输入双与或非门SN74LS55 四4输入与或非门SN74LS73 双J-K触发器SN74LS75 4位双稳锁存器SN74LS78 双J-K触发器SN74LS85 4位幅度比较器SN74LS88 4位全加器SN74LS91 8位移位寄存器SN74LS93 二进制计数器SN74LS95 4位并入并出寄存器SN74LS107 双J-K触发器SN74LS112 双J-K负沿触发器SN74LS114 双J-K负沿触发器SN74LS122 单稳态多谐振荡器SN74LS124 双压控振荡器SN74LS126 四3态总线缓冲器SN74LS132 二输入与非触发器SN74LS136 四异或门SN74LS138 3-8线译码/转换器SN74LS145 BCD十进制译码/驱动器SN74LS148 8-3线优先编码器SN74LS151 8选1数据选择器SN74LS154 4-16线多路分配器SN74LS156 双2-4线多路分配器SN74LS158 四2选1数据选择器SN74LS161 4位二进制计数器SN74LS163 4位二进制计数器SN74LS165 8位移位寄存器SN74LS168 4位可逆同步计数器SN74LS170 4x4位寄存器堆SN74LS173 4D型寄存器SN74LS175 4D烯触发器SN74LS181 运算器/函数发生器SN74LS183 双进位保存全价器SN74LS190 同步BCD十进制计数器SN74LS192 BCD-同步可逆计数器SN74LS194 双向通用移位寄存器SN74LS196 可预置十进制计数器SN74LS221 双单稳态多谐振荡器SN74LS240 八缓冲/驱动/接收器SN74LS242 四总线收发器SN74LS244 八缓冲/驱动/接收器SN74LS247 BCD-七段译码驱动器SN74LS249 BCD-七段译码驱动器SN74LS253 双三态4-1数据选择器SN74LS257 四3态2-1数据选择器SN74LS259 8位可寻址锁存器SN74LS261 2x4位二进制乘发器SN74LS273 八进制D型触发器SN74LS276 四J-K触发器SN74LS280 9位奇偶数发生校检器SN74LS290 十进制计数器SN74LS295 4位双向通用移位寄存器SN74LS366 六缓冲器带公用启动器SN74LS368 六总线三态输出反相器SN74LS374 8D触发器SN74LS377 8位单输出D型触发器SN74LS390 双十进制计数器SN74LS573 8位三态输出D型锁存器SN74LS670 8位数字比较器SN74HC00 四2输入与非门SN74HC02 四2输入或非门SN74HC03 四2输入或非门SN74HC04 六反相器SN74HC05 六反相器SN74HC08 四2输入与门SN74HC10 三3输入与非门SN74HC11 三3输入与门SN74HC14 六反相器/斯密特触发器SN74HC20 双四输入与门SN74HC21 双四输入与非门SN74HC27 三3输入与非门SN74HC30 八输入端与非门SN74HC32 四2输入或门SN74HC42 BCD十进制译码器SN74HC73 双J-K触发器SN74HC74 双D型触发器SN74HC76 双J-K触发器SN74HC86 四2输入异或门SN74HC107 双J-K触发器SN74HC113 双J-K负沿触发器SN74HC123 双稳态多谐振荡器SN74HC125 三态缓冲器SN74HC126 四三态总线缓冲器SN74HC132 二输入与非缓冲器SN74HC137 二输入与非缓冲器SN74HC138 3-8线译码/解调器SN74HC139 双2-4线译码/解调器SN74HC148 8选1数据选择器SN74HC151 双4选1数据选择器SN74HC154 4-16线多路分配器SN74HC157 四2选1数据选择器SN74HC161 4位二进制计数器SN74HC163 4位二进制计数器SN74HC164 8位串入并出移位寄存器SN74HC165 8位移位寄存器SN74HC173 4D型触发器SN74HC174 6D触发器SN74HC175 4D型触发器SN74HC191 二进制同步可逆计数器SN74HC221 双单稳态多谐振荡器SN74HC238 3-8线译码器SN74HC240 八缓冲器SN74HC244 八总线3态输出缓冲器SN74HC245 八总线收发器SN74HC251 三态8-1数据选择器SN74HC259 8位可寻址锁存器SN74HC266 四2输入异或非门SN74HC273 8D型触发器SN74HC367 六缓冲器/总线驱动器SN74HC368 六缓冲器/总线驱动器SN74HC373 8D锁存器SN74HC374 8D触发器SN74HC393 双4位二进制计数器SN74HC541 8位三态输出缓冲器SN74HC573 8位三态输出D型锁存器SN74HC574 8D型触发器SN74HC595 8位移位寄存器/锁存器SN74HC4028 7级二进制串行加数器SN74HC4046 锁相环SN74HC4050 六同相缓冲器SN74HC4051 8选1模拟开关SN74HC4053 三2选1模拟开关SN74HC4060 14位计数/分频/振荡器SN74HC4066 四双相模拟开关SN74HC4078 3输入端三或门SN74HC4511 7段锁存/译码驱动器SN74HC4520 双二进制加法计数器74F00 高速四2输入与非门74F02 高速四2输入或非门74F04 高速六反相器74F08 高速四2输入与门74F10 高速三3输入与门74F14 高速六反相斯密特触发74F32 高速四2输入或门74F38 高速四2输入或门74F74 高速双D型触发器74F86 高速四2输入异或门74F139 高速双2-4线译码/驱动器74F151 高速双2-4线译码/驱动器74F153 高速双4选1数据选择器74F157 高速双4选1数据选择器74F161 高速6D型触发器74F174 高速6D型触发器74F175 高速4D型触发器74F244 高速八总线3态缓冲器74F245 高速八总线收发器74F373 高速8D锁存器SN74HCT04 六反相器74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门 74LS10 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ 8输入与非门 74LS30│ 1 2 3 4 5 6 7│ ________└┬─┬─┬─┬─┬─┬─┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或门 74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或非门 74LS02│14 13 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│14 13 12 11 10 9 8│ _____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐ 4-2-3-2与或非门 74S64 74S65(OC门) │14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688 │20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位锁存器 74LS373│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(OC)TI[DATA]SN7406六高压输出反相器 (OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门 TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门 TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门74756Dual 4-bit open-collector inverting buffer/line driver.+---+--+---+/1OE |1 +--+ 20| VCC1A1 |2 19| /2OE/2Y4 |3 18| /1Y11A2 |4 17| 2A4/2Y3 |5 74 16| /1Y21A3 |6 756 15| 2A3/2Y2 |7 14| /1Y31A4 |8 13| 2A2/2Y1 |9 12| /1Y4GND |10 11| 2A1+----------+74757Dual 4-bit open-collector noninverting buffer/line driver.One active low, one active high output enable.+---+--+---+/1OE |1 +--+ 20| VCC1A4 |2 19| 2OE2Y1 |3 18| 1Y11A3 |4 17| 2A42Y2 |5 74 16| 1Y21A2 |6 757 15| 2A32Y3 |7 14| 1Y31A1 |8 13| 2A22Y4 |9 12| 1Y4GND |10 11| 2A1+----------+747584-bit open-collector inverting bus transceiver.Two enable pins control output enables, one active high and one active low. +---+--+---+/GAB |1 +--+ 14| VCC|2 13| GBAA1 |3 74 12|A2 |4 758 11| B1A3 |5 10| B2A4 |6 9| B3GND |7 8| B4+----------+74760Dual 4-bit open-collector noninverting buffer/line driver. +---+--+---+/1OE |1 +--+ 20| VCC1A1 |2 19| /2OE2Y4 |3 18| 1Y11A2 |4 17| 2A42Y3 |5 74 16| 1Y21A3 |6 760 15| 2A32Y2 |7 14| 1Y31A4 |8 13| 2A22Y1 |9 12| 1Y4GND |10 11| 2A1+----------+* - 本贴最后修改时间:2002-12-9 18:46:59 修改者:autwl* - 修改原因:.autwl 发表于 2002-12-9 18:34 技术交流←返回版面补充1 ZT74804Hex 2-input NAND gates/line drivers.+---+--+---+ +---+---*---+ __1A |1 +--+ 20| VCC | A | B |/Y | /Y = AB1B |2 19| 6B +===+===*===+/1Y |3 18| 6A | 0 | 0 | 1 |2A |4 17| /6Y | 0 | 1 | 1 |2B |5 74 16| 5B | 1 | 0 | 1 |/2Y |6 804 15| 5A | 1 | 1 | 0 |3A |7 14| /5Y +---+---*---+3B |8 13| 4B/3Y |9 12| 4AGND |10 11| /4Y+----------+74805Hex 2-input NOR gates/line drivers.+---+--+---+ +---+---*---+ ___ 1A |1 +--+ 20| VCC | A | B |/Y | /Y = A+B 1B |2 19| 6B +===+===*===+/1Y |3 18| 6A | 0 | 0 | 1 |2A |4 17| /6Y | 0 | 1 | 0 |2B |5 74 16| 5B | 1 | 0 | 0 |/2Y |6 805 15| 5A | 1 | 1 | 0 |3A |7 14| /5Y +---+---*---+3B |8 13| 4B/3Y |9 12| 4AGND |10 11| /4Y+----------+74808Hex 2-input AND gates/line drivers.+---+--+---+ +---+---*---+1A |1 +--+ 20| VCC | A | B | Y | Y = AB 1B |2 19| 6B +===+===*===+1Y |3 18| 6A | 0 | 0 | 0 |2A |4 17| 6Y | 0 | 1 | 0 |2B |5 74 16| 5B | 1 | 0 | 0 |2Y |6 808 15| 5A | 1 | 1 | 1 |3A |7 14| 5Y +---+---*---+3B |8 13| 4B3Y |9 12| 4AGND |10 11| 4Y+----------+7482110-bit 3-state D flip-flop/bus driver.+---+--+---+ +---+---+---*---+/OE |1 +--+ 24| VCC |/OE|CLK| D | Q |D1 |2 23| Q1 +===+===+===*===+D2 |3 22| Q2 | 1 | X | X | Z |D3 |4 21| Q3 | 0 | / | 0 | 0 |D4 |5 20| Q4 | 0 | / | 1 | 1 |D5 |6 74 19| Q5 | 0 |!/ | X | - |D6 |7 821 18| Q6 +---+---+---*---+D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9D10 |11 14| Q10GND |12 13| CLK+----------+7482210-bit 3-state inverting D flip-flop/bus driver.+---+--+---+ +---+---+---*---+/OE |1 +--+ 24| VCC |/OE|CLK| D |/Q |D1 |2 23| /Q1 +===+===+===*===+D2 |3 22| /Q2 | 1 | X | X | Z |D3 |4 21| /Q3 | 0 | / | 0 | 1 |D4 |5 20| /Q4 | 0 | / | 1 | 0 |D5 |6 74 19| /Q5 | 0 |!/ | X | - |D6 |7 822 18| /Q6 +---+---+---*---+D7 |8 17| /Q7D8 |9 16| /Q8D9 |10 15| /Q9D10 |11 14| /Q10GND |12 13| CLK+----------+748239-bit 3-state D flip-flop/bus driver with clock enable and reset.+---+--+---+/OE |1 +--+ 24| VCCD1 |2 23| Q1D2 |3 22| Q2D3 |4 21| Q3D4 |5 20| Q4D5 |6 74 19| Q5D6 |7 823 18| Q6D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9/RST |11 14| /CLKENGND |12 13| CLK+----------+748258-bit 3-state D flip-flop/bus driver with three output enables, clock enable and reset. +---+--+---+/OE1 |1 +--+ 24| VCC/OE2 |2 23| /OE3D1 |3 22| Q1D2 |4 21| Q2D3 |5 20| Q3D4 |6 74 19| Q4D5 |7 825 18| Q5D6 |8 17| Q6D7 |9 16| Q7D8 |10 15| Q8/RST |11 14| /CLKENGND |12 13| CLK+----------+7482710-bit 3-state noninverting buffer/line driver.+---+--+---+/OE1 |1 +--+ 24| VCCA1 |2 23| Y1A2 |3 22| Y2A3 |4 21| Y3A4 |5 20| Y4A5 |6 742 19| Y5A6 |7 827 18| Y6A7 |8 17| Y7A8 |9 16| Y8A9 |10 15| Y9A10 |11 14| Y10GND |12 13| /OE2+----------+74832Hex 2-input OR gates/line drivers.+---+--+---+ +---+---*---+1A |1 +--+ 20| VCC | A | B | Y | Y = A+B 1B |2 19| 6B +===+===*===+1Y |3 18| 6A | 0 | 0 | 0 |2A |4 17| 6Y | 0 | 1 | 1 |2B |5 74 16| 5B | 1 | 0 | 1 |2Y |6 832 15| 5A | 1 | 1 | 1 |3A |7 14| 5Y +---+---*---+3B |8 13| 4B3Y |9 12| 4AGND |10 11| 4Y+----------+748338-bit 3-state noninverting bus transceiver with parity generator/checker and parity register.+---+--+---+/OEA |1 +--+ 24| VCCA1 |2 23| B1A2 |3 22| B2A3 |4 21| B3A4 |5 20| B4A5 |6 74 19| B5A6 |7 833 18| B6A7 |8 17| B7A8 |9 16| B8/ERROR |10 15| PAR/CLR |11 14| /OEBGND |12 13| CLK+----------+7484110-bit 3-state transparent latch/bus driver.+---+--+---+ +---+---+---*---+/OE |1 +--+ 24| VCC |/OE| LE| D | Q |D1 |2 23| Q1 +===+===+===*===+D2 |3 22| Q2 | 1 | X | X | Z |D3 |4 21| Q3 | 0 | 0 | X | - |D4 |5 20| Q4 | 0 | 1 | 0 | 0 |D5 |6 74 19| Q5 | 0 | 1 | 1 | 1 |D6 |7 841 18| Q6 +---+---+---*---+D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9D10 |11 14| Q10GND |12 13| LE+----------+748439-bit 3-state transparent latch/bus driver with set and reset.+---+--+---+ +----+----+---+---+---*---+/OE |1 +--+ 24| VCC |/RST|/SET|/OE| LE| D | Q |D1 |2 23| Q1 +====+====+===+===+===*===+D2 |3 22| Q2 | 0 | 1 | 0 | X | X | 0 |D3 |4 21| Q3 | 1 | 0 | 0 | X | X | 0 |D4 |5 20| Q4 | X | X | 1 | X | X | Z |D5 |6 74 19| Q5 | 1 | 1 | 0 | 0 | X | - |D6 |7 843 18| Q6 | 1 | 1 | 0 | 1 | 0 | 0 |D7 |8 17| Q7 | 1 | 1 | 0 | 1 | 1 | 1 |D8 |9 16| Q8 +----+----+---+---+---*---+D9 |10 15| Q9/RST |11 14| /SETGND |12 13| LE+----------+748458-bit 3-state transparent latch/bus driver with three output enables, set and reset.+---+--+---+/OE1 |1 +--+ 24| VCC/OE2 |2 23| /OE3D1 |3 22| Q1D2 |4 21| Q2D3 |5 20| Q3D4 |6 74 19| Q4D5 |7 845 18| Q5D6 |8 17| Q6D7 |9 16| Q7D8 |10 15| Q8/RST |11 14| /SETGND |12 13| LE+----------+7485712-to-6 line inverting/noninverting data selector/multiplexer with masking and zero detect. +---+--+---+S0 |1 +--+ 24| VCC1A0 |2 23| S11A1 |3 22| 6A01Y |4 21| 6A12A0 |5 20| 6Y2A1 |6 74 19| 5A02Y |7 857 18| 5A13A0 |8 17| 5Y3A1 |9 16| 4A03Y |10 15| 4A1GND |12 13| COMP+----------+7486110-bit 3-state noninverting bus transceiver.+---+--+---+/GBA |1 +--+ 24| VCCA1 |2 23| B1A2 |3 22| B2A3 |4 21| B3A4 |5 20| B4A5 |6 74 19| B5A6 |7 861 18| B6A7 |8 17| B7A8 |9 16| B8A9 |10 15| B9A10 |11 14| B10GND |12 13| /GAB+----------+748639-bit 3-state noninverting bus transceiver.+---+--+---+/GBA1 |1 +--+ 24| VCCA1 |2 23| B1A2 |3 22| B2A3 |4 21| B3A4 |5 20| B4A5 |6 74 19| B5A6 |7 863 18| B6A7 |8 17| B7A8 |9 16| B8A9 |10 15| B9/GBA2 |11 14| /GAB2GND |12 13| /GAB1+----------+748678-bit synchronous binary up/down counter with load, asynchronous reset and ripple carry outp ut.+---+--+---+S1 |2 23| /ENPP0 |3 22| Q0P1 |4 21| Q1P2 |5 20| Q2P3 |6 74 19| Q3P4 |7 867 18| Q4P5 |8 17| Q5P6 |9 16| Q6P7 |10 15| Q7/ENT |11 14| CLKGND |12 13| /RCO+----------+748698-bit synchronous binary up/down counter with load, reset and ripple carry output. +---+--+---+S0 |1 +--+ 24| VCCS1 |2 23| /ENPP0 |3 22| Q0P1 |4 21| Q1P2 |5 20| Q2P3 |6 74 19| Q3P4 |7 869 18| Q4P5 |8 17| Q5P6 |9 16| Q6P7 |10 15| Q7/ENT |11 14| CLKGND |12 13| /RCO+----------+74873Dual 4-bit 3-state transparent latch with reset.+---+--+---+/1RST |1 +--+ 24| VCC/1OE |2 23| 1LE1D1 |3 22| 1Q11D2 |4 21| 1Q21D3 |5 20| 1Q31D4 |6 74 19| 1Q42D1 |7 873 18| 2Q12D2 |8 17| 2Q22D3 |9 16| 2Q32D4 |10 15| 2Q4/2OE |11 14| 2LEGND |12 13| /2RST+----------+74874Dual 4-bit 3-state D flip-flops with reset.+---+--+---+ +----+---+---+---*---+ /1RST |1 +--+ 24| VCC |/RST|/OE|CLK| D | Q | /1OE |2 23| 1CLK +====+===+===+===*===+ 1D1 |3 22| 1Q1 | 0 | 1 | X | X | Z | 1D2 |4 21| 1Q2 | X | 0 | X | X | 0 | 1D3 |5 20| 1Q3 | 1 | 0 | / | 0 | 0 | 1D4 |6 74 19| 1Q4 | 1 | 0 | / | 1 | 1 | 2D1 |7 874 18| 2Q1 | 1 | 0 |!/ | X | - | 2D2 |8 17| 2Q2 +----+---+---+---*---+ 2D3 |9 16| 2Q32D4 |10 15| 2Q4/2OE |11 14| 2CLKGND |12 13| /2RST+----------+74878Dual 4-bit 3-state D flip-flops with reset.+---+--+---+ +----+---+---+---*---+ /1RST |1 +--+ 24| VCC |/RST|/OE|CLK| D | Q | /1OE |2 23| 1CLK +====+===+===+===*===+ 1D1 |3 22| 1Q1 | 0 | 1 | X | X | Z | 1D2 |4 21| 1Q2 | X | 0 | X | X | 0 | 1D3 |5 20| 1Q3 | 1 | 0 | / | 0 | 0 | 1D4 |6 74 19| 1Q4 | 1 | 0 | / | 1 | 1 | 2D1 |7 878 18| 2Q1 | 1 | 0 |!/ | X | - | 2D2 |8 17| 2Q2 +----+---+---+---*---+ 2D3 |9 16| 2Q32D4 |10 15| 2Q4/2OE |11 14| 2CLKGND |12 13| /2RST+----------+748814-bit 16- arithmetic logic unit (ALU)+---+--+---+/B0 |1 +--+ 24| VCC/A0 |2 23| /A1S3 |3 22| /B1S2 |4 21| /A2S1 |5 20| /B2S0 |6 74 19| /A3CIN |7 881 18| /B3M |8 17| /G/F0 |9 16| COUT/F1 |10 15| /P/F2 |11 14| A=BGND |12 13| /F3+----------+748858-bit noninverting magnitude comparator with cascade inputs and latchable A inputs.+---+--+---+L+/A |1 +--+ 24| VCCIA<B |2 23| ALEIA>B |3 22| A7B7 |4 21| A6B6 |5 20| A5B5 |6 74 19| A4B4 |7 885 18| A3B3 |8 17| A2B2 |9 16| A1B1 |10 15| A0B0 |11 14| OA<BGND |12 13| OA>B+----------+748998-bit 3-state noninverting latchable bus transceiver with parity generator/checker and indep endent latch-enable inputs.+---+--+---+O//E |1 +--+ 28| VCC/ERRA |2 27| /OEABLEAB |3 26| B1A1 |4 25| B2A2 |5 24| B3A3 |6 23| B4A4 |7 74 22| B5A5 |8 899 21| B6A7 |10 19| B8A8 |11 18| BPARAPAR |12 17| LEBA/OEBA |13 16| /SELGND |14 15| /ERRB+----------+749568-bit 3-state noninverting latched transceiver.+---+--+---+LEAB |1 +--+ 24| VCCSAB |2 23| LEBADIR |3 22| SBAA1 |4 21| /OEA2 |5 20| B1A3 |6 74 19| B2A4 |7 956 18| B3A5 |8 17| B4A6 |9 16| B5A7 |10 15| B6A8 |11 14| B7GND |12 13| B8+----------+749908-bit transparent latch with readback.+---+--+---+/OERB |1 +--+ 20| VCCD1 |2 19| Q1D2 |3 18| Q2D3 |4 17| Q3D4 |5 74 16| Q4D5 |6 990 15| Q5D6 |7 14| Q6D7 |8 13| Q7D8 |9 12| Q8GND |10 11| LE+----------+749929-bit 3-state transparent latch with readback and reset. +---+--+---+/OERB |1 +--+ 24| VCCD2 |3 22| Q2D3 |4 21| Q3D4 |5 20| Q4D5 |6 74 19| Q5D6 |7 992 18| Q6D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9/RST |11 14| /OEGND |12 13| LE+----------+7499410-bit transparent latch with readback.+---+--+---+/OERB |1 +--+ 24| VCCD1 |2 23| Q1D2 |3 22| Q2D3 |4 21| Q3D4 |5 20| Q4D5 |6 74 19| Q5D6 |7 994 18| Q6D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9D10 |11 14| Q10GND |12 13| LE+----------+741000Quad 2-input NAND gates with buffered output.+---+--+---+ +---+---*---+ __ 1A |1 +--+ 14| VCC | A | B |/Y | /Y = AB 1B |2 13| 4B +===+===*===+/1Y |3 7410 12| 4A | 0 | 0 | 1 |2A |4 00 11| /4Y | 0 | 1 | 1 |2B |5 10| 3B | 1 | 0 | 1 |/2Y |6 9| 3A | 1 | 1 | 0 |GND |7 8| /3Y +---+---*---++----------+741004Hex inverters with buffered output.+---+--+---+ +---*---+ _1A |1 +--+ 14| VCC | A |/Y | /Y = A/1Y |2 13| 6A +===*===+2A |3 7410 12| /6Y | 0 | Z |/2Y |4 04 11| 5A | 1 | 0 |3A |5 10| /5Y +---*---+/3Y |6 9| 4AGND |7 8| /4Y+----------+741005Hex open-collector inverters with buffered output.+---+--+---+ +---*---+ _1A |1 +--+ 14| VCC | A |/Y | /Y = A/1Y |2 13| 6A +===*===+2A |3 7410 12| /6Y | 0 | Z |/2Y |4 05 11| 5A | 1 | 0 |3A |5 10| /5Y +---*---+/3Y |6 9| 4AGND |7 8| /4Y+----------+741032Quad 2-input OR gates with buffered output.+---+--+---+ +---+---*---+1A |1 +--+ 14| VCC | A | B | Y | Y = A+B1B |2 13| 4B +===+===*===+1Y |3 7410 12| 4A | 0 | 0 | 0 |2A |4 32 11| 4Y | 0 | 1 | 1 |2B |5 10| 3B | 1 | 0 | 1 |2Y |6 9| 3A | 1 | 1 | 1 |GND |7 8| 3Y +---+---*---++----------+74335110-tap noninverting delay lines (20, 50 or 100ns total delay). +---+--+---+A |1 +--+ 16| VCC|2 15||3 14| Y1Y2 |4 743 13| Y3Y4 |5 351 12| Y5Y6 |6 11| Y7Y8 |7 10| Y9GND |8 9| Y10+----------+7443748-bit 3-state dual-ranking D flip flop.Designed to prevent stable conditions in data synchronization applications in which setup an d hold times may be violated.+---+--+---+Q1 |1 +--+ 20| D1Q2 |2 19| D2Q3 |3 18| D3Q4 |4 17| D4GND |5 744 16| VCCQ5 |6 374 15| D5Q6 |7 14| D6Q7 |8 13| D7Q8 |9 12| D8/OE |10 11| CLK+----------+747001Quad 2-input AND gates with schmitt-trigger inputs.0.8V typical input hysteresis at VCC=+5V.+---+--+---+ +---+---*---+1A |1 +--+ 14| VCC | A | B | Y | Y = AB1B |2 13| 4B +===+===*===+1Y |3 747 12| 4A | 0 | 0 | 0 |2A |4 001 11| 4Y | 0 | 1 | 0 |2B |5 10| 3B | 1 | 0 | 0 |2Y |6 9| 3A | 1 | 1 | 1 |GND |7 8| 3Y +---+---*---++----------+747266Quad 2-input XNOR gates.+---+--+---+ +---+---*---+ _ _ _1A |1 +--+ 14| VCC | A | B |/Y | Y = A$B = (A.B)+(A.B)1B |2 13| 4B +===+===*===+/1Y |3 747 12| 4A | 0 | 0 | 1 |。

八选一数据选择器

图4-4五输入与门的输出SPICE文件

图4-6五输入与门仿真示意图

从电路图可知,该五输入与门有五个输入端,S,A,B,C,D。电路仿真图中可知,当S,A,B,C,D都为1时,输出Y才为1。当S,A,B,C,D之中至少有一个为0时,输出Y为0。由仿真图可知该功能是正确的。

图4-7五输入与门LVS对比

4.2八输入或门的设计

版图设计在大学阶段课程教学使用软件为Tanner该软件有L-Edit、S-Edit、T-Spice、W-Edit和LVS组成。

Tanner集成电路设计软件是由Tanner Research公司开发的基于Windows平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

IC版图设计是指将前端设计产生的门级网表通过EDA设计工具进行布局布线和进行物理验证并最终产生供制造用的GDSII数据的过程。其主要工作职责有:芯片物理结构分析、逻辑分析、建立后端设计流程、版图布局布线、版图编辑、版图物理验证、联络代工厂并提交生产数据。作为连接设计与制造的桥梁,合格的版图设计人员既要懂得IC设计、版图设计方面的专业知识,还要熟悉制程厂的工作流程、制程原理等相关知识。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DM74150,DM74151AData Selectors/MultiplexersGeneral DescriptionThese data selectors/multiplexers contain full on-chip decod-ing to select the desired data source.The150selects one-of-sixteen data sources;the151A selects one-of-eight data sources.The150and151A have a strobe input which must be at a low logic level to enable these devices.A high level at the strobe forces the W output high and the Y output (as applicable)low.The151A features complementary W and Y outputs, whereas the150has an inverted(W)output only.The151A incorporates address buffers which have sym-metrical propagation delay times through the complementary paths.This reduces the possibility of transients occurring at the output(s)due to changes made at the select inputs,even when the151A outputs are enabled(i.e.,strobe low).Featuresn150selects one-of-sixteen data linesn151A selects one-of-eight data linesn Performs parallel-to-serial conversionn Permits multiplexing from N lines to one linen Also for use as Boolean function generatorn Typical average propagation delay time,data input to W output15011ns151A9nsn Typical power dissipation150200mW151A135mWn Alternate Military/Aerospace device(54150,54151A)is available.Contact a Fairchild Semiconductor SalesOffice/Distributor for specifications.Connection DiagramsDual-In-Line PackageDS006546-1 Order Number54150DQMB,54150FMQB,DM54150J or DM74150NSee Package Number J24A,N24A or W24CDual-In-Line PackageDS006546-2 Order Number54151ADMQB,54151AFMQB, DM54151AJ,DM54151AW or DM74151AN See Package Number J16A,N16E or W16AAbsolute Maximum Ratings(Note1)Supply Voltage7V Input Voltage 5.5V Operating Free Air Temperature RangeDM54and54−55˚C to+125˚C DM740˚C to+70˚C Storage Temperature Range−65˚C to+150˚CRecommended Operating ConditionsSymbol Parameter DM54150DM74150UnitsMin Nom Max Min Nom MaxV CC Supply Voltage 4.55 5.5 4.755 5.25VV IH High Level Input Voltage22VV IL Low Level Input Voltage0.80.8VI OH High Level Output Current−0.8−0.8mA I OL Low Level Output Current1616mA T A Free Air Operating Temperature−55125070˚C Note1:The“Absolute Maximum Ratings”are those values beyond which the safety of the device cannot be guaranteed.The device should not be operated at these limits.The parametric values defined in the“Electrical Characteristics”table are not guaranteed at the absolute maximum ratings.The“Recommended Operating Conditions”table will define the conditions for actual device operation.’150Electrical Characteristicsover recommended operating free air temperature range(unless otherwise noted)Symbol Parameter Conditions Min Typ Max Units(Note2)V I Input Clamp Voltage V CC=Min,I I=−12mA−1.5VV OH High Level Output V CC=Min,I OH=Max 2.4V Voltage V IL=Max,V IH=MinV OL Low Level Output V CC=Min,I OL=Max0.4V Voltage V IH=Min,V IL=MaxI I Input Current@Max V CC=Max,V I=5.5V1mAInput VoltageI IH High Level Input Current V CC=Max,V I=2.4V40µA I IL Low Level Input Current V CC=Max,V I=0.4V−1.6mA I OS Short Circuit V CC=Max DM54−20−55mAOutput Current(Note3)DM74−18−55I CC Supply Current V CC=Max,(Note4)4068mANote2:All typicals are at V CC=5V,T A=25˚C.Note3:Not more than one output should be shorted at a time.Note4:I CC is measured with the strobe and data select inputs at4.5V,all other inputs and outputs open.2’150Switching Characteristicsat V CC=5V and T A=25˚CSymbol Parameter From(Input)R L=400Ω,C L=15pF UnitsTo(Output)Min Maxt PLH Propagation Delay Time Select35ns Low to High Level Output to Wt PHL Propagation Delay Time Select33ns High to Low Level Output to Wt PLH Propagation Delay Time Strobe24ns Low to High Level Output to Wt PHL Propagation Delay Time Strobe30ns High to Low Level Output to Wt PLH Propagation Delay Time E0-E1520ns Low to High Level Output to Wt PHL Propagation Delay Time E0-E1514ns High to Low Level Output to WRecommended Operating ConditionsSymbol Parameter DM54151A DM74151A UnitsMin Nom Max Min Nom MaxV CC Supply Voltage 4.55 5.5 4.755 5.25VV IH High Level Input Voltage22VV IL Low Level Input Voltage0.80.8VI OH High Level Output Current−0.8−0.8mAI OL Low Level Output Current1616mAT A Free Air Operating Temperature−55125070˚C’151A Electrical Characteristicsover recommended operating free air temperature range(unless otherwise noted)Symbol Parameter Conditions Min Typ Max Units(Note5)V I Input Clamp Voltage V CC=Min,I I=−12mA−1.5VV OH High Level Output V CC=Min,I OH=Max 2.4V Voltage V IL=Max,V IH=MinV OL Low Level Output V CC=Min,I OL=Max0.4V Voltage V IH=Min,V IL=MaxI I Input Current@Max V CC=Max,V I=5.5V1mAInput VoltageI IH High Level Input Current V CC=Max,V I=2.4V40µAI IL Low Level Input Current V CC=Max,V I=0.4V−1.6mAI OS Short Circuit V CC=Max DM54−20−55mAOutput Current(Note6)DM74−18−55I CC Supply Current V CC=Max,(Note7)2748mANote5:All typicals are at V CC=5V,T A=25˚C.Note6:Not more than one output should be shorted at a time.Note7:I CC is measured with the strobe and data select inputs at4.5V,all other inputs and outputs open.’151A Switching Characteristicsat V CC=5V and T A=25˚CSymbol Parameter From(Input)R L=400Ω,C L=15pF UnitsTo(Output)Min Max t PLH Propagation Delay Time Select38ns Low to High Level Output(4Levels)to Yt PHL Propagation Delay Time Select30ns High to Low Level Output(4Levels)to Yt PLH Propagation Delay Time Select26ns Low to High Level Output(3Levels)to Wt PHL Propagation Delay Time Select30ns High to Low Level Output(3Levels)to Wt PLH Propagation Delay Time Strobe33ns Low to High Level Output to Yt PHL Propagation Delay Time Strobe30ns High to Low Level Output to Yt PLH Propagation Delay Time Strobe21ns Low to High Level Output to Wt PHL Propagation Delay Time Strobe25ns High to Low Level Output to Wt PLH Propagation Delay Time D0-D724ns Low to High Level Output to Yt PHL Propagation Delay Time D0-D724ns High to Low Level Output to Yt PLH Propagation Delay Time D0-D714ns Low to High Level Output to Wt PHL Propagation Delay Time D0-D714ns High to Low Level Output to W4Logic Diagrams150Logic Diagrams151ADS006546-4 See Address Buffers BelowAddress Buffers for54151A/74151A6Function Tables54150/74150Inputs OutputsSelect Strobe WD C B A SX X X X H HL L L L L E0L L L H L E1L L H L L E2L L H H L E3L H L L L E4L H L H L E5L H H L L E6L H H H L E7H L L L L E8H L L H L E9H L H L L E10H L H H L E11H H L L L E12H H L H L E13H H H L L E14H H H H L E15H=High Level,L=Low Level,X=Don’t CareE0,E1…E15=the complement of the level of the respective E input54151A/75151AInputs OutputsSelect Strobe Y WC B A SX X X H L HL L L L D0D0L L H L D1D1L H L L D2D2L H H L D3D3H L L L D4D4H L H L D5D5H H L L D6D6H H H L D7D7H=High Level,L=Low Level,X=Don’t CareD0,D1…D7=the level of the respective D input8Physical Dimensions inches(millimeters)unless otherwise noted24-Lead Ceramic Dual-In-Line Package(J)Order Number54150DMQB or DM54150JPackage Number J24APhysical Dimensions inches(millimeters)unless otherwise noted(Continued)16-Lead Molded Dual-In-Line Package(N)Order Number DM74151ANPackage Number N16E10Physical Dimensions inches(millimeters)unless otherwise noted(Continued)16-Lead Ceramic Flat Package(W)Order Number54151AFMQB or DM54151AWPackage Number W16A24-Lead Ceramic Flat Package(W)Order Number54150FMQBPackage Number W24CLIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMI-CONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or sys-tems which,(a)are intended for surgical implant intothe body,or (b)support or sustain life,and (c)whosefailure to perform when properly used in accordancewith instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.Fairchild Semiconductor Corporation AmericasCustomer Response Center Tel:1-888-522-5372Fairchild Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)8141-35-0English Tel:+44(0)1793-85-68-56Italy Tel:+39(0)2575631Fairchild SemiconductorHong Kong Ltd.13th Floor,Straight Block,Ocean Centre,5Canton Rd.Tsimshatsui,Kowloon Hong KongTel:+8522737-7200Fax:+8522314-0061National Semiconductor Japan Ltd.Tel:81-3-5620-6175Fax:81-3-5620-6179D M 74150,D M 74151A D a t a S e l e c t o r s /M u l t i p l e x e r sFairchild does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.。