最新CMOS电荷泵的电路设计

电荷泵电路的效率优化研究

交叠时钟信号。当Vo为低电平时,电荷由VDD给V1节 点充电至VDD-Vth;当Vo为高电平时,Vob为低电平,

程,产生相应的功率消耗。电荷泵工作时的电荷再 分配过程如图3。

作者简介:夏天,聚辰半导体股份有限公司,研究方向:集成电路设计。 收稿日期:2021-04-06,修回日期:2021-04-22。

集成电路应用 第 38 卷 第 5 期(总第 332 期)2021 年 5 月 1

研究与设计 Research and Design

图3 电荷泵工作过程中的电荷再分配 电荷泵工作过程中产生电荷再分配功耗的根本原 因是负载电流Iout的存在。由于持续地向负载端输出 Iout,因此即便在最终的稳定状态时,Cout上仍存在 φ1阶段电荷流出,φ2阶段电荷流入的充放电电荷, 这一过程产生的功耗为式(3)。

图8 电荷泵效率与开关管宽度关系 3 仿真及测试结果

使用SMIC 0.13μm ASEE工艺,按照前述的方 法,优化设计了一款电荷泵电路,如图9所示。同 时搭载了一颗原型设计作为对比。

由于级数和主电容大小一致,因此两款电荷泵 的面积基本一致。两款电荷泵的效率测试结果如下 表1所示。通过针对功耗损失的精心优化,电荷泵 的效率提升接近14%。

式(2)所示。

(2)

该值看作一个N级电荷泵的效率极值,实际电

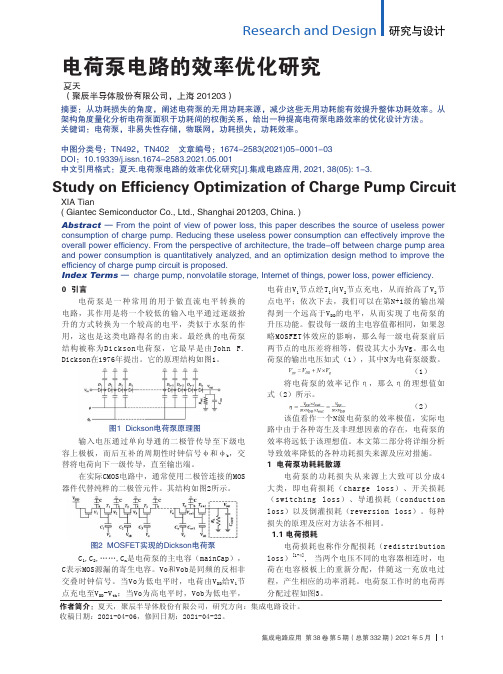

图1 Dickson电荷泵原理图

路中由于各种寄生及非理想因素的存在,电荷泵的

输入电压通过单向导通的二极管传导至下级电

效率将远低于该理想值。本文第二部分将详细分析

容上极板,而后互补的周期性时钟信号φ和φb,交 替将电荷向下一级传导,直至输出端。

一种基于电荷泵锁相环的时钟调节电路设计

一种基于电荷泵锁相环的时钟调节电路设计王雪萍,王金龙,蔡永涛,马金龙中国电子科技集团公司第58研究所摘要:设计了一种基于电荷泵锁相环(PLL)的独特时钟调节电路,可调节时钟频率和延时,可纠正时钟偏斜,能够输出不同相位(0°,90°,180°,270°)锁定且低抖动的各种频率信号,锁相环可外部动态配置。

该电路可应用于FPGA系统集成电路的时钟发生源电路中,能够提供非常灵活的时钟调节功能。

仿真结果表明,该电路满足设计需求。

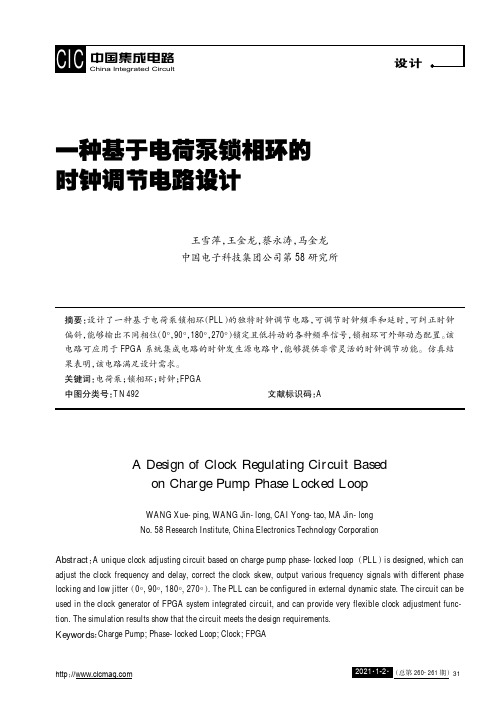

关键词:电荷泵;锁相环;时钟;FPGA中图分类号:TN492文献标识码:AA Design of Clock Regulating Circuit Basedon Charge Pump Phase Locked LoopWANG Xue-ping,WANG Jin-long,CAI Yong-tao,MA Jin-longNo.58Research Institute,China Electronics Technology CorporationAbstract:A unique clock adjusting circuit based on charge pump phase-locked loop(PLL)is designed,which can adjust the clock frequency and delay,correct the clock skew,output various frequency signals with different phase locking and low jitter(0°,90°,180°,270°).The PLL can be configured in external dynamic state.The circuit can be used in the clock generator of FPGA system integrated circuit,and can provide very flexible clock adjustment func-tion.The simulation results show that the circuit meets the design requirements.Keywords:Charge Pump;Phase-locked Loop;Clock;FPGA图1时钟调节电路结构1引言锁相环(Phase-locked Loop ,PLL )是FPGA 类系统集成电路中重要的时钟资源,随着FPGA 在通信、自动化控制、航空航天等领域应用越来越广泛[1-2],PLL 电路设计也越来越关键。

快速稳定的cmos电荷泵电路的设计_概述说明

快速稳定的cmos电荷泵电路的设计概述说明1. 引言1.1 概述CMOS电荷泵电路作为现代电子设备中广泛应用的关键组成部分之一,可以实现电荷的积累和转移,从而达到升压、降压或者反相等功能。

它具有体积小、功耗低、响应速度快等特点,在数字和模拟电路领域得到了广泛的应用。

本文旨在设计一种快速稳定的CMOS电荷泵电路,通过优化设计方法,提高频率特性以及增加稳定性,能够在高效率和低功耗的情况下工作。

对于CMOS电荷泵电路的设计原理进行深入剖析,并提出一种可行且有效的设计方法,通过实验验证其性能并进行结果分析与讨论。

1.2 文章结构本文共包含五个主要部分。

引言部分对文章进行了总体概述;第二部分介绍了CMOS电荷泵电路的设计原理,包括其概述、基本原理及工作方式以及需要考虑的因素;第三部分详细说明了快速稳定的CMOS电荷泵电路设计方法,主要包括高频特性提升技术、增加稳定性的方法和优化功耗和效率的措施;第四部分介绍了实验结果与讨论,包括设计方案介绍、实验条件与参数设置以及结果分析与讨论;最后一部分是结论与展望,对本文的主要研究结果进行总结,并展望未来的研究方向。

1.3 目的本文的目的在于提供一种快速稳定的CMOS电荷泵电路设计方法,以满足现代电子设备对升压、降压或反相等功能的需求。

通过研究CMOS电荷泵电路的设计原理和需要考虑的因素,提出有效的设计方法,尽可能提高其工作频率、稳定性并降低功耗。

通过实验验证和结果分析,评估所提出方法的性能优劣,并为进一步研究提供参考。

最终旨在推动CMOS电荷泵技术在电子设备领域的应用和发展。

2. CMOS电荷泵电路的设计原理:2.1 CMOS电荷泵概述:CMOS电荷泵是一种常见的直流-直流(DC-DC)转换器,在集成电路中广泛应用于电源管理等领域。

它通过周期性切换的方式实现了高压与低压之间的转换。

CMOS电荷泵由一系列开关和电容组成,可以产生所需倍数的输入电压。

2.2 基本原理及工作方式:CMOS电荷泵的基本原理是利用开关将电容器中的电荷转移到输出端,并通过串联或并联连接多个级联以实现所需输出电压。

低功耗电荷泵DCDC转换电路的设计解读

电子科技大学硕士学位论文低功耗电荷泵DC/DC转换电路的设计姓名:杨志江申请学位级别:硕士专业:微电子学与固体电子学指导教师:李肇基20060501摘要摘要高效率、低成本和低噪声己成为便携式设备中电源管理芯片的发展方向。

其中,电荷泵电路采用电荷转移方式工作,在不需要电感元件情况下可实现一定升压,因此这类电源管理芯片在中低功率的应用中倍受欢迎。

该文分析设计的一种低功耗电荷泵DC/DC转换电路源于和海外公司的合作项目。

它采用0.5微米标准 CMOS 工艺制成,输入电压范围为2.OV~5.5V,且输入电压高于或低于输出电压时, 输出电压都可保持稳定的低纹波输出,并能自动工作于升压或降压模式。

该电荷泵电路采用跳周期调制方式(PsM,有效的降低了芯片功耗,特别在轻负载情况下提高了系统的转换效率。

在典型情况下,芯片满载时的静态电流为lmA,空载时的静态电流仅为60uA,关断电流小于O.01uA。

电路还具有软启动、过热保护及过流保护等多重保护功能。

在电路设计中,首先分析了跨周期调制的电荷泵Dc/Dc转换电路的基本原理, 然后推导出电荷泵等效模型,以此为理论依据分析了电荷泵的两种控制模式:线性调制模式和跳周期调制模式。

通过两种调制模式优缺点的比较并根据芯片低功耗要求,选用跳周期调制模式进行了电路的总体结构设计。

在予电路设计中,作者比较深入分析的内容有:基准电路的原理及低电源电压下基准电路的设计:振荡器和控制电路中尖峰脉冲噪声抑制、两分频电路及死区时间设定;驱动及模式选择电路中开关管的宽长比的选择及模式转换点的设计。

在完成电路原理分析与电路设计的基础之上,还应用EDA软件HsPIcE对各个子电路模块和整体电路进行了功能仿真及量化模拟。

其中,整体仿真指标包括:芯片线性调整率和负载调整率、转换效率、输出电压纹波、芯片静态电流、最大负载电流、输出电压温度特性及短路负载电流。

仿真结果均达到预定指标,验证了作者在第二章中阐述的电荷泵Dc仍c转换器的设计理论,是设计理论与实践相结合的一次有价值的尝试。

新型低压四相位高效率电荷泵电路

新型低压四相位高效率电荷泵电路张炎峰;姜伟;胡玉青;张其笑【摘要】目前,降低功耗已成为超大规模集成电路的一个重要的发展方向。

而通过降低片上系统电源电压来降低功耗是目前普遍使用的一种方法。

为了给存储器的编程、擦写过程提供高电压,必须在低电源电压的输入状态下提高电荷泵的输出电压,但也导致每级电荷泵节点电压大幅上升,使得MOS体效成为降低电荷泵输出效率的主要因素。

本文设计了一种四相位电荷泵电路,消除了MOS体效应导致的阈值电压上升的影响,提高了电荷泵电路的电压增益。

在相同的低电源电压下,本文所设计的电荷泵电路可以大幅的减少电荷泵的级数和所消耗的芯片面积,该电路特别适用于低电源电压下工作的嵌入式快闪存储器。

%Nowadays, reducing power consumption has become an important development direction of scaling integrated circuit. By lowering the on-chip system power supply voltage to reduce the power consumption is the method commonly used at present. To provide high voltage to prgram and erase the memory array, we should increase the output voltage and the voltage gain in the condition of low supply voltage input. This paper proposes a four phase charge pump circuit. It eliminates the MOS body effect that causes the threshold voltage rising. Besides, it improves the voltage gain of charge pump circuit and reduces the output ripple voltage of charge pump. This charge pump circuit is very useful for low-voltage embedded flash memory.【期刊名称】《电子设计工程》【年(卷),期】2016(024)005【总页数】4页(P148-151)【关键词】电荷泵;低电源电压;体效应;四相位;输出纹波;嵌入式闪存【作者】张炎峰;姜伟;胡玉青;张其笑【作者单位】苏州大学城市轨道交通学院江苏苏州 215000;苏州大学城市轨道交通学院江苏苏州 215000;苏州大学城市轨道交通学院江苏苏州 215000;苏州大学城市轨道交通学院江苏苏州 215000【正文语种】中文【中图分类】TN432随着SoC技术的不断更新换代,系统电源电压的不断降低,目前,在90 nm工艺的SoC芯片中,其系统电源电压已降到1.2 V。

一种应用于EEPROM的高压电荷泵的设计

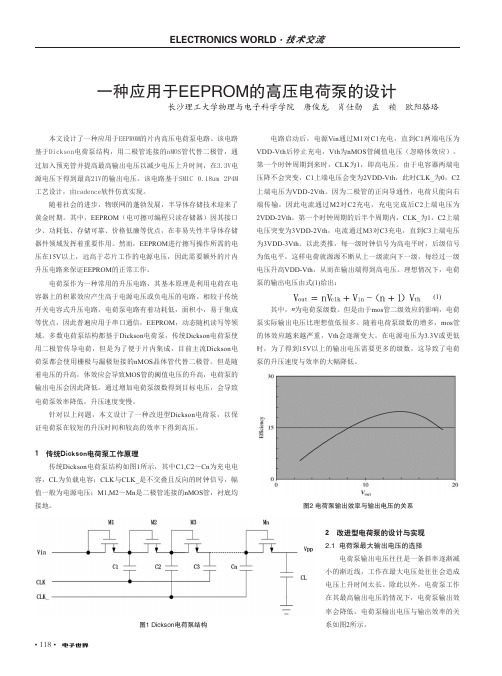

• 118•本文设计了一种应用于EEPROM的片内高压电荷泵电路。

该电路基于Dickson电荷泵结构,用二极管连接的nMOS管代替二极管,通过加入预充管并提高最高输出电压以减少电压上升时间,在3.3V电源电压下得到最高21V的输出电压。

该电路基于SMIC 0.18um 2P4M 工艺设计,由cadence软件仿真实现。

随着社会的进步,物联网的蓬勃发展,半导体存储技术迎来了黄金时期。

其中,EEPROM (电可擦可编程只读存储器)因其接口少、功耗低、存储可靠、价格低廉等优点,在非易失性半导体存储器件领域发挥着重要作用。

然而,EEPROM 进行擦写操作所需的电压在15V 以上,远高于芯片工作的电源电压,因此需要额外的片内升压电路来保证EEPROM 的正常工作。

电荷泵作为一种常用的升压电路,其基本原理是利用电荷在电容器上的积累效应产生高于电源电压或负电压的电路。

相较于传统开关电容式升压电路,电荷泵电路有着功耗低,面积小,易于集成等优点,因此普遍应用于串口通信,EEPROM ,动态随机读写等领域。

多数电荷泵结构都基于Dickson 电荷泵,传统Dickson 电荷泵使用二极管传导电荷,但是为了便于片内集成,目前主流Dickson 电荷泵都会使用栅极与漏极短接的nMOS 晶体管代替二极管。

但是随着电压的升高,体效应会导致MOS 管的阈值电压的升高,电荷泵的输出电压会因此降低。

通过增加电荷泵级数得到目标电压,会导致电荷泵效率降低,升压速度变慢。

针对以上问题,本文设计了一种改进型Dickson 电荷泵,以保证电荷泵在较短的升压时间和较高的效率下得到高压。

1 传统Dickson电荷泵工作原理传统Dickson 电荷泵结构如图1所示,其中C1,C2~Cn 为充电电容,CL 为负载电容;CLK 与CLK_是不交叠且反向的时钟信号,幅值一般为电源电压;M1,M2~Mn 是二极管连接的nMOS 管,衬底均接地。

电路启动后,电源Vin 通过M1对C1充电,直到C1两端电压为VDD-Vth 后停止充电,Vth 为nMOS 管阈值电压(忽略体效应)。

电荷泵电路参数

电荷泵电路参数全文共四篇示例,供读者参考第一篇示例:电荷泵电路是一种常用的电路设计,用于从电压较低的电路提升到较高的电压级别。

在现代电子设备中,电荷泵电路被广泛应用于LCD显示屏、手机和摄像头等设备中。

电荷泵电路的参数是指影响电路性能和稳定性的各种特性和指标。

通过调整这些参数,可以实现不同的电压升压率、效率和输出波形等要求。

下面将详细介绍一些常见的电荷泵电路参数及其影响。

1. 输入电压范围(Vin):电荷泵电路的输入电压范围决定了电路能够提供的最大输出电压。

通常来说,输入电压范围越宽,电路提供的输出电压范围也越大。

因此,在设计电荷泵电路时,需要根据具体需求选择合适的输入电压范围。

2. 输出电压范围(Vout):输出电压范围是电荷泵电路最重要的参数之一。

通过调整电路中的元件和拓扑结构,可以实现不同的输出电压范围。

在实际应用中,需要根据具体设备的电压要求选择合适的输出电压范围。

3. 输出电流能力:输出电流能力决定了电荷泵电路能够提供的最大输出电流。

通常来说,输出电流能力越大,电路能够驱动的负载也越大。

因此在设计电荷泵电路时,需要考虑所需驱动的负载及其电流需求。

4. 效率(Efficiency):效率是指电荷泵电路将输入电压转换成输出电压的能力。

通常来说,效率越高,电路产生的热量就越少,运行更加稳定。

在设计电荷泵电路时,需要尽可能提高电路的效率,以减少能量浪费和热量产生。

5. 输出波形质量:输出波形质量是指电路产生的输出波形是否稳定、纯净。

在一些对波形质量要求较高的应用中,如音频放大器和信号调理器,需要特别关注电荷泵电路的输出波形质量,避免产生干扰和噪音。

在实际应用中,设计电荷泵电路时需要综合考虑以上各项参数,并根据具体需求做出相应的调整。

同时,还需要考虑电路的稳定性、可靠性和成本等因素,以确保设计出符合要求的电路。

总之,电荷泵电路的参数是影响电路性能和稳定性的重要因素,通过合理设计和调整这些参数,可以实现满足不同需求的电荷泵电路设计。

纳米级CMOS技术下具有超低待机漏电电流的多电源ESD钳位电路的设计

纳米级CMOS技术下具有超低静态漏电电流的多电源ESD钳位电路的设计Chang-Tzu Wang,Student Menber,IEEE,and Ming-Dou Ker,Fellow,IEEE摘要:一个超低漏电电流多电源ESD钳位电路是用栅极电流来减少静态漏电电流,这个电路是由SCR和新型ESD检测电路组成。

通过控制在一定偏置条件下ESD 检测电路中的栅极电流,整个多电源ESD钳位电路能达到超低水平的静态漏电电流。

新的电路已经在1V、65nm的CMOS工艺下进行实验验证。

假设在室温下设置1V偏置条件下只有一个96nA的静态漏电电流和只占据一个仅49μm×21μm的工作区域的条件下,新的多电源ESD钳位电路能达到7kV人体放电模式和325V 机器放电模式ESD水平。

索引条目——静电阻抗器(ESD),栅极漏电,多电源ESD钳位电路,可控硅(SCR)。

一、介绍随着低功率应用电路电源补偿电压的降低,在纳米级CMOS技术中栅极氧化层也按比例减小。

然而,在发展的CMOS技术中仅仅2nm 薄的栅极氧化层已被指出因栅极漏电电流而导致在芯片中产生相当大的一部分漏电电流[1]。

在45nm系列和后来的产品中,因而金属栅极技术可以用来减少栅极漏电电流[2]。

尽管如此,栅极漏电问题仍然存在于当前没有运用金属栅极结构的90nm和65nm技术产品中。

栅极电流被规范于BSIM4 MOSFET标准,并且制造商也提供了纳米级CMOS 工艺相应的SPICE标准给电路设计者。

近日,一些报告提出了在发展CMOS工艺中对于数字电路怎样降低栅极漏电电流[3],[4]。

就商业IC产品来说,达到ESD的规格是产品质量的保证。

多电源ESD钳位电路有效保护核心电路通常是用带有大型ESD钳位MOSFET 的RC触发的ESD保护结构[5]。

图1(a)就是传统的RC触发的ESD 钳位电路。

然而,大型MOSFET(M ESD)造成了栅极漏电电流,并且在传统多电源系统ESD钳位电路中的MOS电容器(Mc)在纳米级CMOS工艺中很难实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Vref端输入将变大的一个信号,CLK和CLK’就是I10-ZN和I9ZN端的两个反相时钟信号,当B为低电频视作为0,D为高电频 的时候,从Vref端输入的信号进过M1,AB两端的电压差就是 Vref+Vth,经过M2时,CD两端的电压差为Vref+Vth+CLK,此 时D端电压为1.8V,电容不能突变电压,所以仍然存在电势差, 所以B点电压就是Vref+Vth+1.8,以此类推一直经过M6,Mf1 和Mf2可以看作一个低通滤波器,把交流信号变成直流信号, 最后从Bias端输出放大信号。

根据上图由M28-D输入一个高电频信号到A点,由D点是高电 频所以M1电容充电,M2导通,C点变为低电频,经过3次反相 器到E点为高电频传到B点,则B为高电频时M3导通,D点变 为低电频,M1放电,M2断开,C点变为高电频再由3次反相器 到E点变为低电频传到B点,B点为低电频时M3断开,D点为 高电频。如此反复循环从I9-ZN,I10-ZN两端输出两个反相的振 荡周期信号。

四版图的设计与优化

本芯片拟采用 ASMC0.35林m双层多晶硅、三层金 属的高压Bi一CMOs工艺来实现。并应用Cadence 系统软件提供的 VirtuosoLayout软件进行版图的设 计工作。在版图完成后使用Dracula工具从单元电 路到系统进行DRC,LVS验证。

1布局与布线 2DRC 3LVS

谢谢各位老师指导!

此课件下载可自行编辑修改,仅供参考! 感谢您的支持,我们努力做得更好!谢谢

五总结与展望

本文介绍了一种电荷泵电路在500KHZ条件 下把最初的输入电压通过振荡器产生两个 反相的周期信号,再由RS触发器把占空比 变为百分之五十,最后由电荷泵把输出的 1.3V放大到12.2V,实践证明这一电路是很 有使用价值的。

80 年代末90 年代初各半导体器件厂生产的电荷泵变换器是以 ICL7660为基础开发出一些改进型产品,如MAXIM 公司的 MAX1044、Telcom 公司的TC1044S、TC7660 和LTC 公司的 LTC1044/7660等。这些改进型器件功能与ICL7660相同,性能 上有改进,管脚排列与ICL7660完全相同,可以互换。 这一 类器件的缺点是:输出电流小;输出电阻大;振荡器工作频 率低,使外接电容容量大;静态电流大。 随着半导体工艺技

二 CMOS电荷泵的电路原理

此电荷泵由三部分组成,分别为

1,Oscillator 振荡器 2,RS-FF RS触发器 3,Charge pump 电荷泵 先由振荡器产生反向周期信号,然后由RS触发器让周 期信号占空比为百分之五十,最后通过电荷泵把低电压 变高电压。

Байду номын сангаас

三 CMOS电荷泵的设计与仿真结果

术的进步与便携式电子产品的迅猛发展,各半导体器件公司

开发出各种新型电荷泵变换器,它们在器件封装、功能和性

能方面都有较大改进,并开发出一些专用的电荷泵变换器。 它们的特点可归纳为:

1. 提高输出电流及降低输出电阻 2减小功耗 3扩大输入电压范围 4. 减少占印板的面积 5. 输出负电压可设定(调整) 6. 两种新型的四倍压器件

从I10-ZN和I9-ZN两个输入端输入上节中环形振荡器得出的两 个反相振荡周期信号,根据上章定义的A门的一个输入端为Rd 端,低电平有效,此时 Sd端应为高电平。B门的一个输入端为 Sd端,此时 Rd端应为高电平。又因为上升沿输出反转,下升 沿输出无影响,所以每次I10-ZN端的电平在上升,I9-ZN端的 电平在下降的时候,输出端I1-ZN和I2-ZN会完成一次变化,所 以就能得出两个占空比为百分之五十的反相时钟信号。

CMOS电荷泵的电路设计

一 CMOS电荷泵的背景

电荷泵电路是一种能够产生比电源电压更高的电压 的电路。它在实现过程中不使用电感,而能够只用电容和 有源器件来实现,非常便于集成。电荷泵电路具有广泛应 用,一个重要的用途是用于非易失性存储器中,作为编程 电压产生器或电平转换电路中的高压产生器。电荷泵电路 还应用在需要高压来驱动模拟开关的低电源电压开关电容 系统、数模转换器和DC-DC转换器中。随着IC的设计与制 造中晶体管尺寸的逐渐减小以及低功耗的需求越来越高, 电源电压将不断降低,电荷泵电路的应用也将越来越广泛。