伪随机序列发生器设计

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验七伪随机序列发生器设计

一、实验目的

1.掌握伪随机序列(m序列)发生器的基本原理和设计方法;

2.深入理解VHDL中signal和variable的不同及其应用;

二、设计描述及方法

1.伪随机序列概述

在扩展频谱通信系统中,伪随机序列起着十分关键的作用。在直接序列扩频系统得发射端,伪随机序列将信息序列的频谱扩展,在接收端,伪随机序列将扩频信号恢复为窄带信号,进而完成信息的接收。

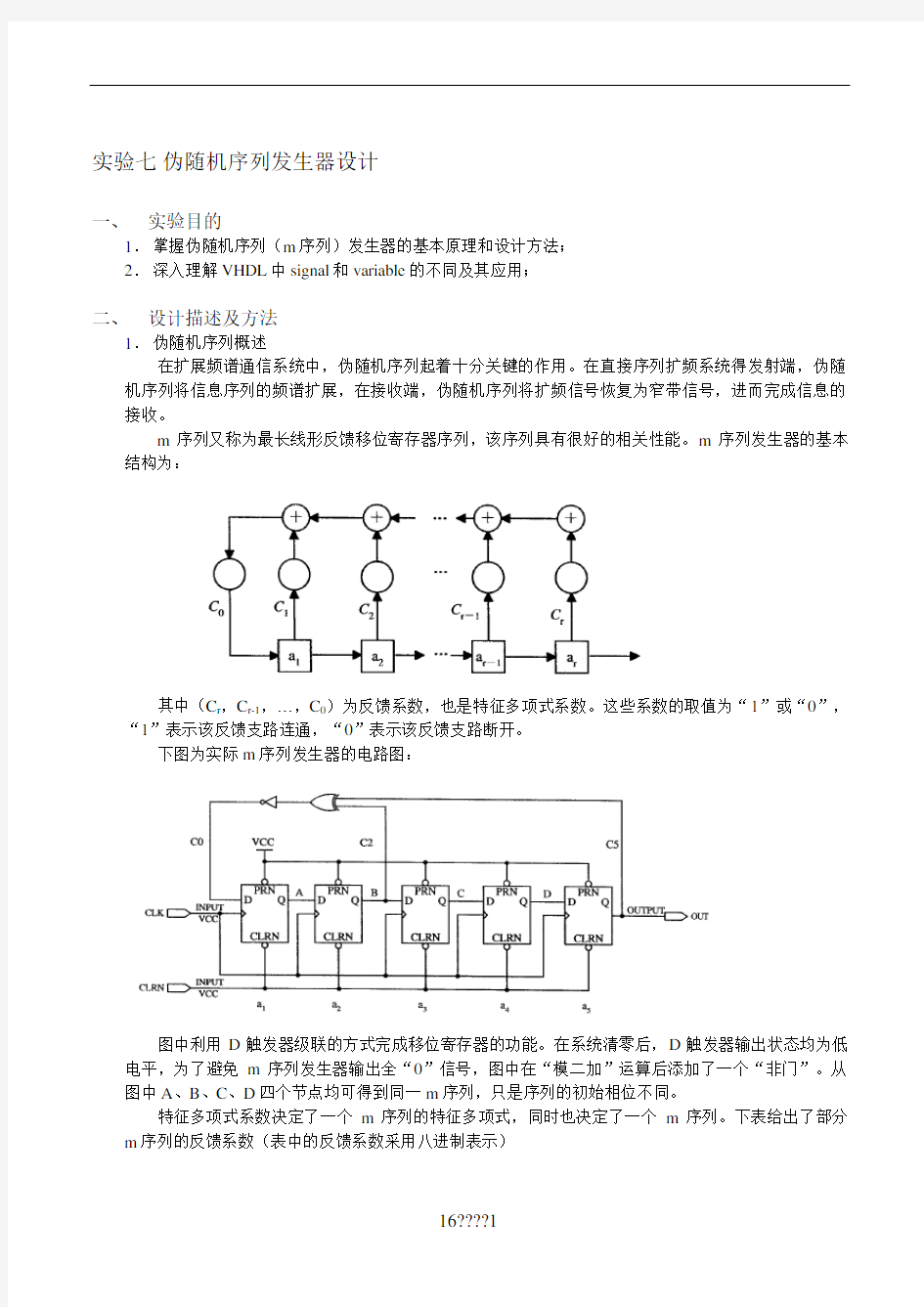

m序列又称为最长线形反馈移位寄存器序列,该序列具有很好的相关性能。m序列发生器的基本结构为:

其中(C r,C r-1,…,C0)为反馈系数,也是特征多项式系数。这些系数的取值为“1”或“0”,“1”表示该反馈支路连通,“0”表示该反馈支路断开。

下图为实际m序列发生器的电路图:

图中利用D触发器级联的方式完成移位寄存器的功能。在系统清零后,D触发器输出状态均为低电平,为了避免m序列发生器输出全“0”信号,图中在“模二加”运算后添加了一个“非门”。从图中A、B、C、D四个节点均可得到同一m序列,只是序列的初始相位不同。

特征多项式系数决定了一个m序列的特征多项式,同时也决定了一个m序列。下表给出了部分m序列的反馈系数(表中的反馈系数采用八进制表示)

2. 电路设计基本方法

本实验要设计一个寄存器级数为5的m 序列发生器,从m 序列发生器反馈系数表可知,有三个反馈系数可选,即可以产生三种不同的m 序列;在以下设计的接口描述中choice (1 downto0)为m 序列选择输入信号,clk 为时钟输入信号,reset 为复位信号,psout 为m 序列输出信号。

三、 程序代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity mps is

port (clk,reset : in std_logic;

choice : in std_logic_vector(1 downto 0);

psout: out std_logic );

end mps;

architecture behave of mps is

signal a :std_logic_vector(4 downto 0);

signal k:std_logic;

begin

process(clk,reset,choice,a) clk reset mps.vhd choice(1 downto 0)

psout

begin

case choice is

when "00"=> k<=not(a(3) xor a(2));

when "01"=> k<=not(a(4) xor a(3)xor a(2)xor a(0));

when "10"=> k<=not(a(4) xor a(2)xor a(1)xor a(0));

when others =>k<='X';

end case;

if clk'event and clk='1' then

a(0)<=k;

for i in 1 to 4 loop

a(i)<=a(i-1);

end loop;

end if;

if(reset='1') then

a<="00000";

end if;

end process;

psout<=a(4);

end behave;

四、功能仿真

五、RTL级电路