进制7段数码显示译码器设计实验报告

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验目的与要求

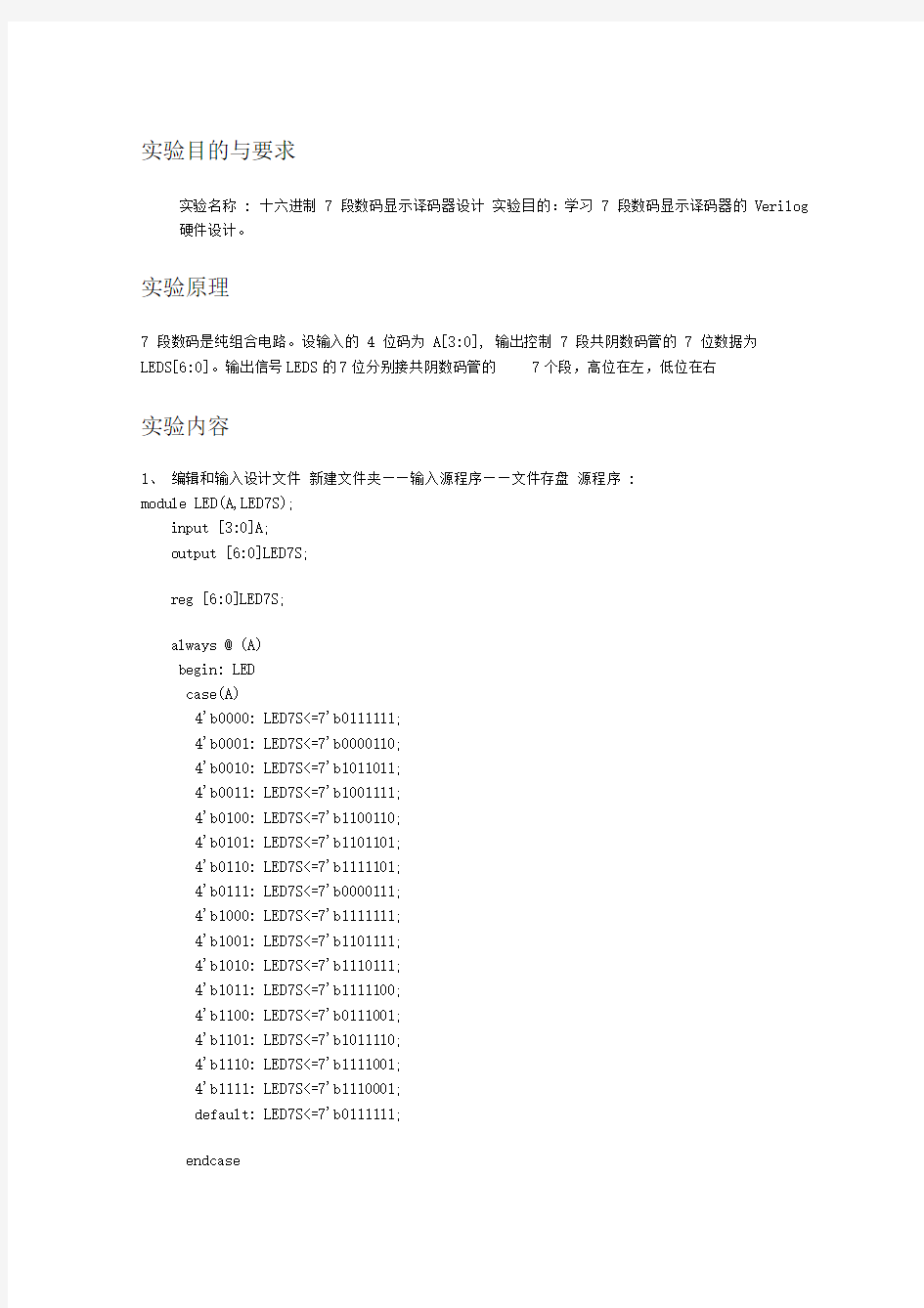

实验名称: 十六进制7 段数码显示译码器设计实验目的:学习7 段数码显示译码器的Verilog 硬件设计。

实验原理

7 段数码是纯组合电路。设输入的4 位码为A[3:0], 输出控制7 段共阴数码管的7 位数据为

LEDS[6:0]。输出信号LEDS的7位分别接共阴数码管的7个段,高位在左,低位在右

实验内容

1、编辑和输入设计文件新建文件夹——输入源程序——文件存盘源程序:

module LED(A,LED7S);

input [3:0]A;

output [6:0]LED7S;

reg [6:0]LED7S;

always @ (A)

begin: LED

case(A)

4'b0000: LED7S<=7'b0111111;

4'b0001: LED7S<=7'b0000110;

4'b0010: LED7S<=7'b1011011;

4'b0011: LED7S<=7'b1001111;

4'b0100: LED7S<=7'b1100110;

4'b0101: LED7S<=7'b1101101;

4'b0110: LED7S<=7'b1111101;

4'b0111: LED7S<=7'b0000111;

4'b1000: LED7S<=7'b1111111;

4'b1001: LED7S<=7'b1101111;

4'b1010: LED7S<=7'b1110111;

4'b1011: LED7S<=7'b1111100;

4'b1100: LED7S<=7'b0111001;

4'b1101: LED7S<=7'b1011110;

4'b1110: LED7S<=7'b1111001;

4'b1111: LED7S<=7'b1110001;

default: LED7S<=7'b0111111;

endcase

end en dmodule

2、创建工程

打开并建立新工程管理窗口一一将设计文件加入工程中一一选择目标芯片一一工具设置一

—结束设置

3、全程编译前约束项目设置

选择FPGA目标芯片一一选择配置器件的工作方式一一选择配置器件和编程方式一一选

择目标器件引脚端口状态--- 选择Verilog语言版本

4、全程综合与编译

Processi ng -- Start Compilatio n 启动全程编译

5、仿真测试

图观察器应用

Eecodei "■

通过本次实验,对quartus有了进一步的学习和认识,对Verilog 也有了深入了解。学会了7段数码显示译码器的Verilog的硬件设计,学会了利用计数器模块消除抖动。