实验三74ls139译码器实验

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三译码器实验

一、实验目的

1、掌握中规模集成电路译码器的工作原理及逻辑功能。

2、学习译码器的灵活应用。

二、实验设备

1、SAC-DS4数字逻辑电路实验箱 1个

2、74LS138 3-8线译码器2片

3、74LS20 双四输入与非门 1片

三、实验内容与步骤

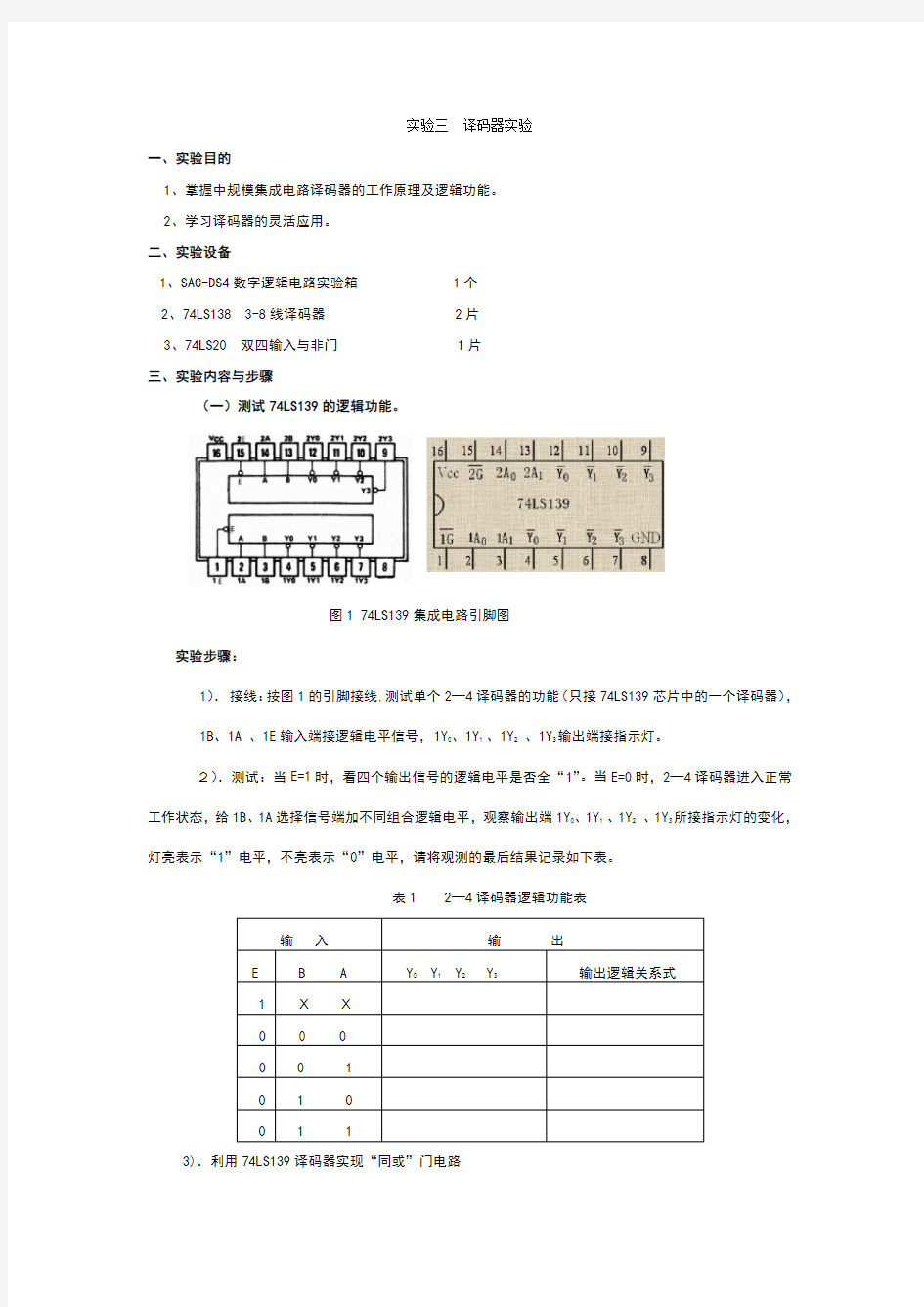

(一)测试74LS139的逻辑功能。

图1 74LS139集成电路引脚图

实验步骤:

1).接线:按图1的引脚接线,测试单个2—4译码器的功能(只接74LS139芯片中的一个译码器),1B、1A 、1E输入端接逻辑电平信号,1Y0、1Y1 、1Y2、1Y3输出端接指示灯。

2).测试:当E=1时,看四个输出信号的逻辑电平是否全“1”。当E=0时,2—4译码器进入正常工作状态,给1B、1A选择信号端加不同组合逻辑电平,观察输出端1Y0、1Y1 、1Y2、1Y3所接指示灯的变化,灯亮表示“1”电平,不亮表示“0”电平,请将观测的最后结果记录如下表。

表1 2—4译码器逻辑功能表

输入输出

E B A Y0 Y1 Y2 Y3输出逻辑关系式

1 ΧΧ

00 0

0 0 1

0 1 0

0 1 1

3).利用74LS139译码器实现“同或”门电路

Y =30Y Y •=30Y Y +=B A B A •+•=A ⊙B

如下图2所示连接电路,将实验结果填入表中,验证其逻辑关系。是否符合“同或”逻辑门电路的逻辑关系。

图2 用74LS139译码器实现“同或”逻辑门电路接线图和真值

4).利用74LS139译码器实现“异或”门电路 Y =21

Y Y •=2

1Y Y +=

B A B A •+•=A B

如下图3所示连接电路,将实验结果填入表中,验证其逻辑关系。是否符合“异或”逻辑门电路的逻辑关系。

Y

图3 用74LS139译码器实现“异或”逻辑门电路接线图和真值

二、用74LS139集成电路将2—4译码器扩展成3—8译码器。

1).接线:扩展的3—8译码器逻辑电路如图3—4所示。按图3—4连线,A 、B 、C 输入端接实验板电平信号,Y 0 ~Y 7接到指示灯。

图4 用74LS139集成电路将2—4译码器扩展成3—8译码器电路图

2).测试:按真值表4给扩展的3—8译码器输入端送入不同组合的逻辑电平,将输出端显示的逻辑电平填

Y o Y 1

74LS139

Y 2 Y 3

&

V cc

E A B

G Y o Y 174LS139

Y 2 Y 3

&

V cc

E A B G

Y

Y 0 Y 1 Y 2 Y 3

74LS139(A ) 1A 1B 1E

Y 4

Y 5 Y 6 Y 7

74LS139(B) 2A 2B 2E

&

45671112109

2

3

1

14

13

15

A

B

C

入表中,灯亮表示“1”电平,灯灭表示“0”电平。

表4 3—8译码器真值表

输 入 输 出 C B A Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

3). 写出3—8译码器输出逻辑关系式:

Y 0= Y 1= Y 2= Y 3= Y 4= Y 5= Y 6= Y 7=

4).利用3—8译码器实现3输入多数表决器。要求3个输入A 、B 、C 中有2个和3个为1时,输出Y 为高电平,否则Y 为低电平。根据3输入多数表决器的要求,可以有两种方案来实现。

a.采用“与非”门来实现。

图5 多数表决器 表5

从3—8译码器输出逻辑关系式可以得到表决器的输出为:Y=7653

Y Y Y Y •••如图5所示,根据不同的输

74LS139(A)

74LS139(B)

2

1A 2B 1B 2A

2E

Y o Y 1Y 2Y 3

Y 4Y 5Y 6Y

Y 7

3

1

15

14134567

9

1011

12

A B C

&

Y o 11Y 1

2Y 12Y o

1Y 21Y 3

2Y 3

2Y 2&

E

1

入值获得相应的Y把结果记录如下表5

b.采用“或”门来实现,从3—8译码器输出逻辑关系式可以得到表决器的输出为: Y=

7

6

5

3

Y

Y

Y

Y+

+

+

①写出函数的标准与或表达式,并变换为与非-与非形式。

②画出用二进制译码器和与非门实现这些函数的接线图。

图6多数表决器逻辑电路图表6

根据不同的输入值获得相应的Y把结果记录如下表6

⎪⎩

⎪

⎨

⎧

=

=

=

=

∑

∑

-

-

7

6

5

3

1

7

4

2

1

1

)7,6,5,3(

)

,

,

(

)7,4,2,1(

)

,

,

(

m

m

m

m

m

C

B

A

C

m

m

m

m

m

C

B

A

S

i

i

i

i

i

i

i

i