3-8译码器的设计实验报告

3-8译码器实验报告

3-8译码器实验报告

班级:121 姓名:连森学号:02

1.实验目标与实验要求:

1.理解译码器的概念和意义

2.理解译码器在计算机电路里的作用。

2.实验器材:

Altair 80C31Small 教学实验平台杜邦线

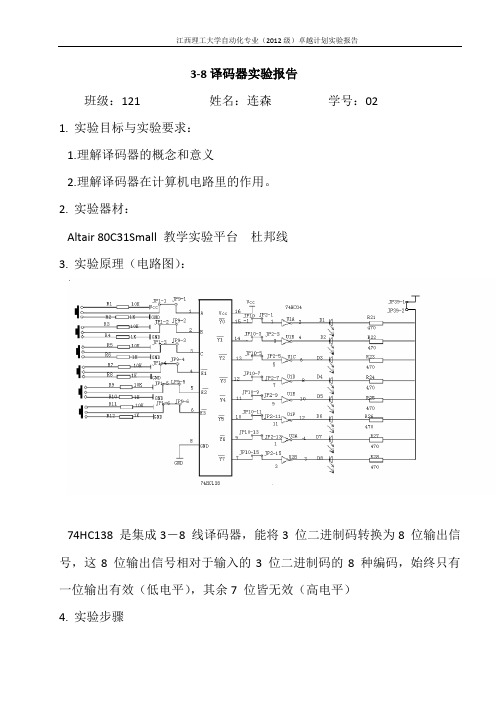

3.实验原理(电路图):

74HC138 是集成3-8 线译码器,能将3 位二进制码转换为8 位输出信号,这8 位输出信号相对于输入的3 位二进制码的8 种编码,始终只有一位输出有效(低电平),其余7 位皆无效(高电平)

4.实验步骤

首先用杜邦线将A3实验区与逻辑开关K1~K6相连的JP1-1~JP1-6,连接到A7实验区与74HC138相连的JP9单号插针;接着在74HC138的输出端连接绿色LED显示器;然后用跳线连接JP39-1与JP39-2,即可接通电源。

5.实验结果(现象):

当K4、K5、K6 打到0、0、1时,译码器74HC138 的逻辑功能有效,相应引脚输出低电平,对应LED 熄灭。

否则,74HC138 始终输出高电平(无效电平),LED 全亮。

学号_姓名_3-8译码器实验报告

电子科技大学实验报告学生姓名:学号:指导教师:黄*实验地点:主楼C2-514实验时间:(1班)一、实验室名称:虚拟仪器实验室二、实验项目名称:3-8 译码器实验三、实验学时:4学时四、实验原理开发板上共四个按键:SW3~SW6,其中SW3 为总开关;SW4、SW5、SW6 作为三个译码输入。

本实验3-8 译码器所有的接口如下。

input ext_clk_25m, //外部输入25MHz 时钟信号input ext_rst_n, //外部输入复位信号,低电平有效input[3:0] switch, //4个拨码开关接口,ON -- 低电平;OFF -- 高电平。

SW3 为总开关;SW4、SW5、SW6 的三个译码输入output reg[7:0] led //8 个LED 指示灯接口注:X 表示ON 或OFF,即任意状态。

五、实验目的熟悉利用HDL代码输入方式进行电路的设计和仿真的流程,掌握Verilog语言的基本语法。

并通过一个3-8译码器的设计把握利用EDA软件(Quartus II 13.1)进行HDL代码输入方式的电子线路设计与仿真的详细流程。

六、实验内容利用HDL代码输入方式在Quartus II 13.1平台上实现一个3-8译码器设计,并进行仿真,然后生成配置文件下载到开发板上进行验证。

七、实验器材(设备、元器件)1. 计算机(安装Quartus II 13.1& ModelSim13.1软件平台);2. Cyclone IV FPGA开发板一套(带Altera USB-Blaster下载器)。

八、实验步骤(1)新建工程,设置器件属性:在Quartus II 13.1平台中,新建一个工程(注意命名规范),在“Family”中选择“Cyclone IV E”系列,“Availabledevice”中选择具体型号“EP4CE6E22C8”,设置好器件属性。

在EDATool Settings 页面中,可以设置工程各个开发环节中需要用到的第三方(Altera 公司以外)EDA 工具,我们只需要设置“Simulation”工具为“ModelSim-Altera”,Format 为“Verilog HDL”即可,其他工具不涉及,因此都默认为<None>。

3 8译码器实验报告

3 8译码器实验报告3 8译码器实验报告引言:在数字电路中,译码器是一种常见的逻辑电路,用于将输入的二进制编码转换为对应的输出信号。

本实验旨在通过搭建一个3 8译码器电路,并对其进行测试和分析,以加深对译码器工作原理的理解。

实验目的:1. 理解3 8译码器的基本原理和工作方式;2. 掌握搭建3 8译码器电路的方法;3. 进行实验测试并分析结果。

实验器材:1. 3 8译码器芯片;2. 逻辑门芯片(与门、非门等);3. 连线板、导线等。

实验步骤:1. 将3 8译码器芯片和逻辑门芯片连接到连线板上;2. 根据芯片引脚的连接要求,使用导线将各个芯片的输入和输出连接起来;3. 将输入信号接入3 8译码器芯片的输入端;4. 将输出信号接入逻辑门芯片的输入端;5. 将逻辑门芯片的输出信号连接到LED灯或其他输出设备上;6. 调整输入信号,观察输出信号的变化。

实验结果:通过实验,我们得到了以下结果:1. 当输入信号为000时,输出信号为00000001;2. 当输入信号为001时,输出信号为00000010;3. 当输入信号为010时,输出信号为00000100;4. 当输入信号为011时,输出信号为00001000;5. 当输入信号为100时,输出信号为00010000;6. 当输入信号为101时,输出信号为00100000;7. 当输入信号为110时,输出信号为01000000;8. 当输入信号为111时,输出信号为10000000。

结果分析:根据实验结果,我们可以看到,3 8译码器将输入的三位二进制编码转换为对应的八位输出信号。

每个输出信号代表一个特定的输入编码。

通过观察输出信号的变化,我们可以清晰地看到译码器的工作原理:根据输入编码的不同,译码器会激活对应的输出线路,将其输出为高电平信号,而其他输出线路则为低电平信号。

实验总结:通过本次实验,我们深入了解了3 8译码器的工作原理和应用场景。

译码器在数字电路中扮演着重要的角色,能够将复杂的二进制编码转换为易于理解和使用的信号输出。

实验五 3-8线译码器

实验五 3-8线译码器一、实验目的1、熟悉常用译码器的功能逻辑。

2、掌握复杂译码器的设计方法。

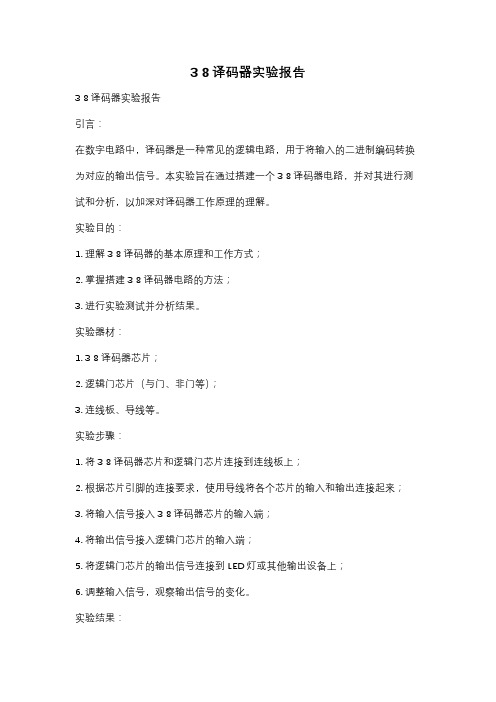

二、实验原理1、总体思路以EP2C5中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七段LED数码管上显示出来。

2、3-8线译码器原理图如下图所示:三、实验程序实验参考代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY DECODE ISPORT(DATA_IN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);LEDOUT,DATA_OUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW :OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END DECODE;ARCHITECTURE ADO OF DECODE ISSIGNAL OUTA,D_OUT : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINLEDW<="000";PROCESS (DATA_IN)VARIABLE DIN: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINDIN:=DATA_IN;LEDOUT<=OUTA;DATA_OUT<=D_OUT;CASE DIN ISwhen "000" => OUTA<="00111111" ; --"0"when "001" => outa<="00000110" ; --"1"when "010" => outa<="01011011"; --"2"when "011" => outa<="01001111"; --"3"when "100" => outa<="01100110"; --"4"when "101" => outa<="01101101"; --"5"when "110" => outa<="01111101"; --"6"when "111" => outa<="00000111"; --"7"WHEN OTHERS => OUTA<="XXXXXXXX";END CASE;CASE DIN ISWHEN "000" => D_OUT<="00000000";WHEN "001" => D_OUT<="00000001";WHEN "010" => D_OUT<="00000010";WHEN "011" => D_OUT<="00000100";WHEN "100" => D_OUT<="00001000";WHEN "101" => D_OUT<="00010000";WHEN "110" => D_OUT<="00100000";WHEN "111" => D_OUT<="01000000";WHEN OTHERS=> D_OUT<="XXXXXXXX";END CASE;END PROCESS;END ADO;四、实验步骤1、打开Quartus II,选择“File”菜单下的“New Project Wizard”,建立Project及顶层实体的名称为ADO,期间,选择的目标芯片为EP2C5Q208C8N;2、选择“File”菜单下的“New”命令,在“New”窗口中选择“VHDL Files”,输入程序,进行编译;3、选择“File”菜单中的“New”项,在“New”窗口中选择“Other Files”中的“VectorWaveform File”项,打开空白的波形编辑器,输入所有的信号节点,给输入随机赋值,保存,单击工具栏上的快捷方式,进行波形仿真;4、打开“Assignments”菜单下的“Pins”命令,打开引脚锁定窗口,进行引脚锁定,再次对VHDL Files进行编译;5、连接EDA实验箱,将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG 口连接起来,万用下载区右下角的电源开关拨到 SOPC下载的一边,将JPLED1短路帽右插,JPLED的短路帽全部上插,请将JP103的短路帽全部插上。

EDA实验:3-8译码器的设计

组合逻辑3-8译码器的设计一、实验目的:1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步掌握Max+PlusII软件的基本操作与应用。

4、初步了解可编程器件的设计全过程。

二、实验步骤:(一)设计输入:1、软件的启动:单击“开始”进入“程序”选中“Max+PlusII 10.1 BASELINE”,打开“”MaxplusII软件,如图4.1-1所示。

图4.1-12、启动File\New菜单,弹出设计输入选择窗口,如图4.1-2所示:图4.1-23、选择Graphic Editor File ,单击OK ,打开原理图编辑器,进入原理图设计输入电路编辑状态,如图4.1-3所示:4、设计输入1)放置一个器件在原理图上a 、在原理图的空白处双击鼠标右键,出现图4.1-4:图4.1-3图4.1-4b 、在光标处输入元件名称(如:input ,output ,and2,and3,nand2,or2,not ,xor ,dff 等)或用鼠标点击库元件,按下OK 即可。

c 、如果安放相同的元件,只要按住Ctrl 键,同时用鼠标按左键拖动该元件复制即可。

d 、一个完整的电路包括:输入端口input 、电路元件集合、输出端口output 。

e 、图4.1-5为3-8译码器元件安放结果。

2)添加连线到器件的引脚上:把鼠标移到元件引脚附近,则鼠标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线。

3-8译码器原理图连线后如图4.1-6所示。

图4.1-5图4.1-63)标记输入/输出端口属性分别双击输入端口的“PINNAME ”,当变成黑色时,即可输入标记符并回车确认;输出端口标记方法类似。

本译码器的三输入端分别标记为:A 、B 、C ;其八输出端分别为:D0、D1、D2、D3、D4、D5、D6、D7。

如图4.1-7所示。

4)保存原理图单击保存按钮图表,对于新建文件,出现类似文件管理器图框,请选择保存路径/文件名称保存原理图,原理图的扩展名为.gdf ,本实验中取名为test1.gdf 。

3线8线译码器七段译码器实验报告

实验报告数据选择器设计12传感网金涛1228403019一.实验目的1.熟悉硬件描述语言软件的使用2.熟悉译码器的工作原理和逻辑功能3.掌握译码器及七段显示译码器的设计方法二.实验原理译码器是数字系统中常用的组合逻辑电路。

译码器的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或者另外一个代码。

译码是编码的反操作。

常用的译码电路有二进制译码器、二—十进制译码器和显示译码器。

三.实验内容1.设计一个3线—8线译码器。

程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder3_8 ISPORT(a0,a1,a2,g1,g2a,g2b:IN STD_LOGIC;Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END decoder3_8;ARCHITECTURE rtl of decoder3_8 isSIGNAL indata :STD_LOGIC_VECTOR(2 DOWNTO 0);BEGININdata <=a2&a1&a0;PROCESS(indata,g1,g2a,g2b)BEGINIF(g1='1' AND g2b='0' AND g2a='0')THENCASE INDA TA ISWHEN"000"=>Y<="11111110";WHEN"001"=>Y<="11111101";WHEN"010"=>Y<="11111001";WHEN"011"=>Y<="11110111";WHEN"100"=>Y<="11101111";WHEN"101"=>Y<="11011111";WHEN"110"=>Y<="10111111";WHEN"111"=>Y<="01111111";WHEN OTHERS=> NULL;END CASE;ELSEY<="11111111";END IF;END PROCESS;END rtl;仿真波形仿真波形分析g1g2ag2b为控制输入端,a2a1a0为数据输入端,y0y1y2y3y4y5y6y7为数据输出端。

实验一 3—8译码器

实验一:组合逻辑3-8译码器的设计说明:本书将以实验一为例详细介绍altera公司max+plusII 10.0版本软件的基本应用,其它实验将不再赘述。

读者在通过本实验后将对max+plusII软件及CPLD/FPGA的设计与应用有一个比较完整的概念和思路。

此处仅仅介绍了max+plusII软件的最基本、最常用的一些基本功能,相信读者在熟练使用本软件以后,你定会发现该软件还有好多非常方便、快捷、灵活的设计技巧与开发功能。

一、实验目的:1、通过一个简单的3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解可编程器件设计的全过程。

二、实验步骤:MaxplusII软件的基本操作与应用(一)设计输入:1、软件的启动:进入Altera软件包,打开MAX+plus II 10.0软件,如图1-1所示。

图:1-12、启动File \ New菜单,弹出设计输入选择窗口,如下图1-2所示。

或点击下图1-3主菜单中的空白图标,进入新建文件状态。

图:1-2图:1-33、选择Graphic Editor File,单击ok按钮,打开原理图编辑器,进入原理图设计输入电路编辑状态,如下图1-4所示:图:1-44、设计的输入1)放置一个器件在原理图上a.在原理图的空白处双击鼠标左键,出现窗口如图2-2;也可单击鼠标右键,出现窗口如图2-1,选择“Enter symbol..”,出现窗口如图2-2,进入器件选择输入窗口。

图2-1图:2-2b.在“symbol name”提示处(光标处)输入元件名称或用鼠标双击库文件(在提示窗”Symbol Libraries”里的各个文件),在提示窗“Symbol Files”中双击元件或选中元件按下OK即可将该器件放置到原理图中。

c.如果安放相同元件,只要按住Ctrl键,同时用鼠标拖动该元件复制即可。

d.一个完整的电路包括:输入端口INPUT、电路元器件集合、输出端口OUTPUT。

实验一3-8译码器

3-8译码器的仿真

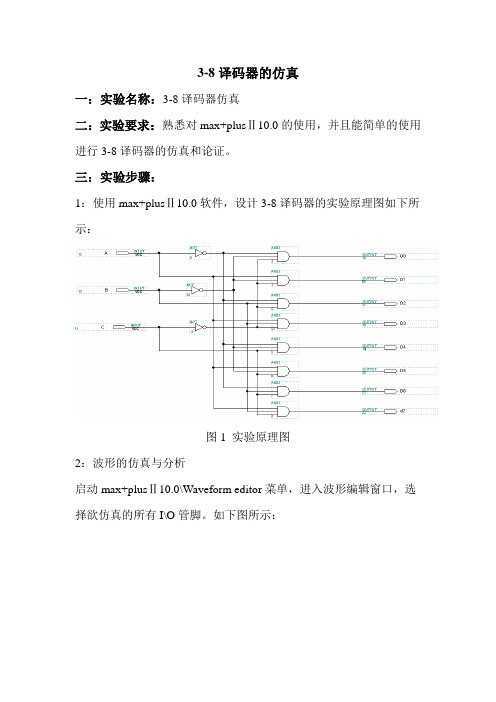

一:实验名称:3-8译码器仿真

二:实验要求:熟悉对max+plusⅡ10.0的使用,并且能简单的使用进行3-8译码器的仿真和论证。

三:实验步骤:

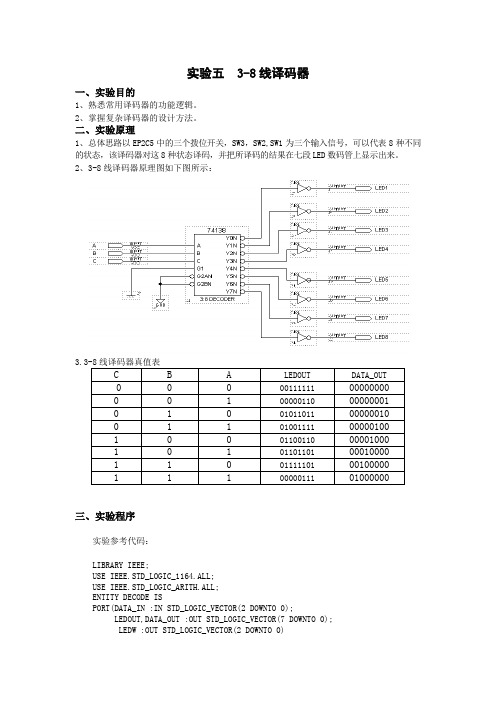

1:使用max+plusⅡ10.0软件,设计3-8译码器的实验原理图如下所示:

图1 实验原理图

2:波形的仿真与分析

启动max+plusⅡ10.0\Waveform editor菜单,进入波形编辑窗口,选择欲仿真的所有I\O管脚。

如下图所示:

图2 波形编辑

为输入端口添加激励波形,使用时钟信号。

选择初始电平为“0”,时

钟周期倍数为“1”。

添加完后,波形图如下所示:

图3 添加激励后的波形

打开max+plusⅡ10.0\Simulator菜单,确定仿真时间,单击Start开始仿真,如下图所示:

图4 仿真过程

图5 仿真结果

四:实验结论:使用max+plusⅡ10.0能很好的完成很多电路的仿真与工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA实验报告书

1根据74138的功能,当S0=1, S 仁0, S2=0时译码器处于工作状态。

否则 译码器被禁止,所有输出端被封锁在高电平。

由真值表画出卡诺图,再写出对 应表达式,再画出电路。

2、使用VHDL 语言时,应注意头文件以及各种输入的格式,使用

IF 语句, CASE 语句设计电路,最后再用 END 语句结束程序。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY SA IS

PORT(

D:IN STD_LOGIC_VECTOR(2 DOWNTO 0); S0,S1,S2:IN STD_LOGIC; Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );

END ;

ARCHITECTURE XIANI OF SA IS BEGIN

PROCESS(D,S0,S1,S2) BEGIN

IF (S0='0')THEN Y<="11111111";

ELSIF(S0='1' AND S1='0' AND S2='0')THEN

IF (D(2)='0' AND D(1)='0' AND D(0)='0')THEN Y<="01111111"; ELSIF (D(2)='0' AND D(1)='0' AND D(0)='1')THEN Y<="10111111"; ELSIF (D(2)='0' AND D(1)='1' AND D(0)='0')THEN Y<="11011111"; ELSIF (D(2)='0' AND D(1)='1' AND D(0)='1')THEN Y<="11101111"; ELSIF (D(2)='1' AND D(1)='0' AND D(0)='0')THEN Y<="11110111"; ELSIF (D(2)='1' AND D(1)='0' AND D(0)='1')THEN Y<="11111011"; ELSIF (D(2)='1' AND D(1)='1' AND D(0)='0')THEN Y<="11111101"; ELSIF (D(2)='1' AND D(1)='1' AND D(0)='1')THEN Y<="11111110";

设 计 思

路 设

计 原 理 图 及 源 程 序

ELSE Y<=”ZZZZZZZZ”;

END IF;

ELSE Y<="ZZZZZZZZ"; END IF; END PROCESS; END;

■ V3

•世

■

ffi

■i •啊

Delay Matrix

Desinfllim

7i

a &Orw S.Ohs 50ns- S.ftis

5&w

5 Ohs

HOn 盘 b 5唏 S.Ohs

50ns- 弓加

50ht

自阮

5.0ns

D

50ns* 6.0ns

伽

S.Ohg 5.0m SiOna 伽

5.0ns 命

5i Ohs 5心g 5.0ns

5.0ns 5.0ns

5.0ns 5.0ns 5.Qn^ si 5i0r» S.OhE &0h$ 5.0ns 5% 5.Qng 5.0ns

B.Qns s2

50hs

E.Qn?

&0rw

5.0ns

&0m

S.Oki?

&Ohi

E.Ote

|¥T77T

Ht tub

仿 直 /、 波 形

实

验结果

ft# |鹏伽

十 limp |時12na Mrai |.2Pna |

严

•■M B

I aioi^ 型血 潮愉 珈恤 知伽 BGC >

OIB 叭恤 ・

] L

I ■! I

fflOOng

i

1 1

910

Ong 1

930抽 i

MO TIB M.Dkw

h 1

蚁加恥阮剛饥測

-…丄”“,.—”一"11—“

才吕2

a

a 1

Hi

» i 1

\ 2

I 「「

(1 s 2

I l ). $ K 5 K T i Q \ 、 \ 3

WDF K TF y

Bf H

CF it EF f FT /

ra K fD ]

\ FE

2潢【

DF

'EF

K FT 1 RA ( FO K

FE K ?F K

K D

-

YO

Y1

Y2

¥3

丫 4

Y6

Y7

DID 5.0rts 5L0hs 5.0m 5. Ohs

5.003

5.0ns 5.0ns 5.0hs D1 S.Ont

5LDH& 5.0FB

5.0nt

5.0<K

5. Ohs 5.0ns

5i0m D2

S.0m

5 0ht &0n

EOit

E.Qrd

5iOhf 5.Cktt

5i0m so

BOh^/iJSns 5,0n5/1J6n5 B&is/lJtni 5,0n?/13&i¥ 50n^nl6ni- 5()n¥/13 6n? £0h5/i36n? 5Qn¥/13&1? 51

5.0ns/13.6nE

5.0ns/13.&w & Ois/13.6ns 5.0ns/l 3.6ns 5.0hs/H3.6rft 5.0n?/13 6ri? 5.0hs/13.6ns 5.0>?/13.5n& S2

5.0ns/13.6ns

&Dhs/13l6ns

5.0ns/13.6n$

5.0hs/13.6rw

5.Qns/13,Ens

5.0hs/13.6rB

5.0ns/13lEns

Q

>

■冊

羽丄"ii” "i"・

■帥 ■Hjh' 越iJSlT, !H0A 曲舸 好.m W.i[r tHHi , jJpJj 电 —0*。