组成实验报告

计算机组成原理实验报告

重庆理工大学《计算机组成原理》实验报告学号 __***********____姓名 __张致远_________专业 __软件工程_______学院 _计算机科学与工程二0一六年四月二十三实验一基本运算器实验报告一、实验名称基本运算器实验二、完成学生:张致远班级115030801 学号11503080109三、实验目的1.了解运算器的组成结构。

2.掌握运算器的工作原理。

四、实验原理:两片74LS181 芯片以并/串形式构成的8位字长的运算器。

右方为低4位运算芯片,左方为高4位运算芯片。

低位芯片的进位输出端Cn+4与高位芯片的进位输入端Cn相连,使低4位运算产生的进位送进高4位。

低位芯片的进位输入端Cn可与外来进位相连,高位芯片的进位输出到外部。

两个芯片的控制端S0~S3 和M 各自相连,其控制电平按表2.6-1。

为进行双操作数运算,运算器的两个数据输入端分别由两个数据暂存器DR1、DR2(用锁存器74LS273 实现)来锁存数据。

要将内总线上的数据锁存到DR1 或DR2 中,则锁存器74LS273 的控制端LDDR1 或LDDR2 须为高电平。

当T4 脉冲来到的时候,总线上的数据就被锁存进DR1 或DR2 中了。

为控制运算器向内总线上输出运算结果,在其输出端连接了一个三态门(用74LS245 实现)。

若要将运算结果输出到总线上,则要将三态门74LS245 的控制端ALU-B 置低电平。

否则输出高阻态。

数据输入单元(实验板上印有INPUT DEVICE)用以给出参与运算的数据。

其中,输入开关经过一个三态门(74LS245)和内总线相连,该三态门的控制信号为SW-B,取低电平时,开关上的数据则通过三态门而送入内总线中。

总线数据显示灯(在BUS UNIT 单元中)已与内总线相连,用来显示内总线上的数据。

控制信号中除T4 为脉冲信号,其它均为电平信号。

由于实验电路中的时序信号均已连至“W/R UNIT”单元中的相应时序信号引出端,因此,需要将“W/R UNIT”单元中的T4 接至“STATE UNIT”单元中的微动开关KK2 的输出端。

xx大学计算机组成原理实验报告(全)

上海大学计算机组成原理实验报告(全)《计算机组成原理实验》报告一姓名学号时间地点行健楼 609机房评阅一.数据传送实验1. 实验内容及要求在试验箱上完成以下内容:将58H写入A寄存器。

将6BH写入W寄存器。

将C3H 写入R1寄存器。

2. 实验环境本实验箱用74HC574构成各种寄存器。

3. 实施步骤或参数①注视仪器,打开电源,手不要远离电源开关,随时准备关闭电源,注意各数码管、发光管的稳定性,静待10秒,确信仪器稳定、无焦糊味。

②设置实验箱进入手动模式。

③K2接AEN,K1和K2接EX0和EX1,设置K2K1K0=010,设置K23~K16=01011000。

④注视A及DBUS的发光管,按下STEP键,应看到CK灯灭、A旁的灯亮。

记住看到的实际显示情况。

⑤放开STEP键,应看到CK灯亮、A寄存器显示58。

记住看到的实际情况。

⑥重复上述实验步骤,在做6BH时,K2接WEN,K1和K2接EX2和EX3,设置K2K1K0=010,设置K23~K16=01101011;重复上述实验步骤,在做C3H时,K2接RWR,K1和K2接SB 和SA,设置K2K1K0=001,设置K23~K16=10100011。

⑦关闭实验箱电源。

4. 测试或者模拟结果A寄存器显示58,W寄存器显示6B,R1寄存器显示C3,完成实验目的。

5. 体会本次实验相对简单,只需要三根线便可以完成整个实验,但是,今天认识了实验箱。

124并且在老师的带领下较为完整的认识了整个试验箱,还是很开心的,今后实验箱将是我们学习计算机组成原理的重要工具,也是我们的好朋友。

《计算机组成原理实验》报告二姓名学号时间地点行健楼 609机房评阅二.运算器实验1. 实验内容及要求在试验箱上完成以下内容:计算07H+6AH后左移一位的值送OUT输出。

把39H取反后同64H相或的值送入R2寄存器。

通过人工译码,加深对译码器基本工作原理的理解。

理解命令的顺序执行过程。

计算机组成原理实验报告_32位ALU设计实验

实验三32位ALU设计实验一、实验目的学生理解算术逻辑运算单元(ALU)的基本构成,掌握Logisim 中各种运算组件的使用方法,熟悉多路选择器的使用,能利用前述实验完成的32位加法器、Logisim 中的运算组件构造指定规格的ALU 单元。

二、实验原理、内容与步骤实验原理、实验内容参考:1、32位加法功能的原理与设计1)设计原理1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。

这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。

而最后的第32位必须在前31位全部计算出结果后,才能开始计算。

这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

2)电路设计32位加法功能2、32位减法功能的原理与实现1)变减法为加法的原理1.在Y引脚处使用求补器(32位),即可变减法为加法2.用构造好的32位加法器。

Y各位取反,C0取1,即可达到减法变加法。

无符号数的减法溢出,带加减功能的ALU的进位取反后表示,有符号数的减法溢出,仍然用最高位和符号位是否相等来判断2)电路设计32位减法功能3、加减溢出检测的设计(不考虑乘除法)1)有符号数溢出的设计有符号数溢出的设计2)无符号数溢出的设计无符号数溢出的设计4、移位的原理与设计1)逻辑移位逻辑移位2)算术移位算术移位5、逻辑运算功能的原理与设计2)与、或、异或、或非逻辑6、大于、等于、小于功能设计大于、等于、小于功能设计7、AluOP的控制原理与设计1)原理:AluOP的控制原理与设计8、总电路设计图算术逻辑运算单元ALU三、实验结论及分析(实验完成功能情况、存在问题分析或改进思路、自己的心得体会等。

《计算机组成原理》学生实验报告

《计算机组成原理》学生实验报告(2011~2012学年第二学期)专业:信息管理与信息系统班级: A0922学号:10914030230姓名:李斌目录实验准备------------------------------------------------------------------------3 实验一运算器实验-----------------------------------------------------------7 实验二数据通路实验-------------------------------------------------------13 实验三微控制器实验--------------------------------------------------------18 实验四基本模型机的设计与实现------------------------------------------22实验准备一、DVCC实验机系统硬件设备1、运算器模块运算器由两片74LS181构成8位字长的ALU。

它是运算器的核心。

可以实现两个8位的二进制数进行多种算术或逻辑运算,具体由74181的功能控制条件M、CN、S3、S2、S1、S0来决定,见下表。

两个参与运算的数分别来自于暂存器U29和U30(采用8位锁存器),运算结果直接输出到输出缓冲器U33(采用74LS245,由ALUB信号控制,ALUB=0,表示U33开通,ALUB=1,表示U33不通,其输出呈高阻),由输出缓冲器发送到系统的数据总线上,以便进行移位操作或参加下一次运算。

进位输入信号来自于两个方面:其一对运算器74LS181的进位输出/CN+4进位倒相所得CN4;其二由移位寄存器74LS299的选择参数S0、S1、AQ0、AQ7决定所得。

触发器的输出QCY就是ALU结果的进位标志位。

QCY为“0”,表示ALU结果没有进位,相应的指示灯CY灭;QCY为“1”,表示ALU结果有进位,相应的指示灯CY点亮。

杭电计算机组成原理实验报告.doc

杭电计算机组成原理实验报告篇一:杭电计组实验报告9计组实验九老师:包健一、源代码测试模块代码:moduleTest_Top;// Inputsreginclk;regmem_clk;regrst;reg [3:0] SW;// Outputswire [7:0] LED;// Instantiate the Unit Under TestTop uut ,.mem_clk,.rst,.LED,.SW);reg [2:0] i;initial begin// Initialize Inputsinclk = 0;mem_clk = 0;rst = 0;SW = 0;i=0;// Wait 100 ns for global reset to finish #100;rst = 1;#100;rst =0 ;#100;foreverbegin#100;mem_clk=~mem_clk;i=i+1;ifinclk=~inclk;endendendmodule顶层模块代码:moduleMy_I_CPU;wireclk_n = ~clk;wire[31:0] codes;Inst_Fetch1 inst_fetch,.clk,.Inst_codes);wire[5:0] OP;wire[5:0] func;wire[2:0] ALU_OP;wirerd_rt_s;wireimm_s;wirert_imm_s;wirealu_mem_s;wireWrite_Reg;wireMem_Write;wire [15:0] imm;wire [31:0] imm_data ;assign imm_data = ?{{16{imm[15]}},imm}:{{16{1b0}},imm}; assign OP =codes[31:26];assignfunc = codes[5:0];assignimm = codes[15:0]; OP_Decoderop_decoder,//input.func,//input.ALU_OP,.rd_rt_s,.imm_s,.rt_imm_s,.alu_mem_s,.Write_Reg,.Mem_Write);wire[4:0] rs;wire[4:0] rt;wire[4:0] rd;assigs = codes[25:21];assigt = codes[20:16];assigd = codes[15:11];wire[4:0] W_Addr;assignW_Addr=?rt:rd;wire [31:0]W_Data;wire [31:0]R_Data_A;wire [31:0]R_Data_B; RegisterHeapregister,.R_Addr_B,.W_Addr,.Write_Reg,.Reset,.Clk,.W_Data,.R_Data_A,.R_Data_B);wire [31:0]ALU_A;wire [31:0]ALU_B;assign ALU_A = R_Data_A;assign ALU_B = ?imm_data:R_Data_B;ALU alu,.A,.B,.F,.ZF,.OF);Data_Memdata_mem , // input clka.wea, // input [0 : 0] wea .addra, // input [5 : 0] addra .dina, // input [31 : 0] dina .douta // output [31 : 0] douta);assignW_Data = ?M_R_Data:ALU_F; endmodule二、仿真波形三、电路图四、引脚配置篇二:杭电计算机组成原理取指令与指令译码实验7杭州电子科技大学计算机学院实验报告课程名称:计算机组成原理姓名实验项目:取指令与指令译码实验班级指导教师:学号:实验位置:日期:篇三:杭电计算机组成原理多功能ALU设计实验3杭州电子科技大学计算机学院实验报告课程名称:计算机组成原理姓名:实验项目:多功能ALU设计实验班级:指导教师:学号:实验位置:日期:2015年4月29日。

计算机组成原理实验报告

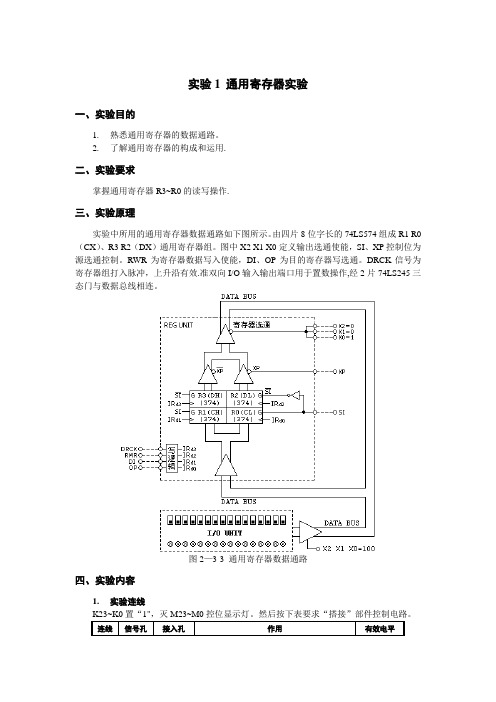

实验1 通用寄存器实验一、实验目的1.熟悉通用寄存器的数据通路。

2.了解通用寄存器的构成和运用.二、实验要求掌握通用寄存器R3~R0的读写操作.三、实验原理实验中所用的通用寄存器数据通路如下图所示。

由四片8位字长的74LS574组成R1 R0(CX)、R3 R2(DX)通用寄存器组。

图中X2 X1 X0定义输出选通使能,SI、XP控制位为源选通控制。

RWR为寄存器数据写入使能,DI、OP为目的寄存器写选通。

DRCK信号为寄存器组打入脉冲,上升沿有效.准双向I/O输入输出端口用于置数操作,经2片74LS245三态门与数据总线相连。

图2—3-3 通用寄存器数据通路四、实验内容1.实验连线连线信号孔接入孔作用有效电平2.寄存器的读写操作①目的通路当RWR=0时,由DI、OP编码产生目的寄存器地址,详见下表.通用寄存器“手动/搭接”目的编码②通用寄存器的写入通过“I/O输入输出单元”向R0、R1寄存器分别置数11h、22h,操作步骤如下:通过“I/O输入输出单元”向R2、R3寄存器分别置数33h、44h,操作步骤如下:③源通路当X2~X0=001时,由SI、XP编码产生源寄存器,详见下表.通用寄存器“手动/搭接”源编码④ 通用寄存器的读出关闭写使能,令K18(RWR )=1,按下流程分别读R0、R1、R2、R3。

五、实验心得通过这个实验让我清晰的了解了通用寄存器的构成以及通用寄存器是如何运用的,并且熟悉了通用寄存器的数据通路,而且还深刻的掌握了通用寄存器R3~R0的读写操作。

实验2 运算器实验一、实验目的掌握八位运算器的数据传输格式,验证运算功能发生器及进位控制的组合功能.二、实验要求完成算术、逻辑、移位运算实验,熟悉ALU 运算控制位的运用.三、实验原理实验中所用的运算器数据通路如图2-3—1所示。

ALU 运算器由CPLD 描述。

运算器的输出FUN 经过74LS245三态门与数据总线相连,运算源寄存器A 和暂存器B 的数据输入端分别由2个74LS574锁存器锁存,锁存器的输入端与数据总线相连,准双向I/O 输入输出端口用来给出参与运算的数据,经2片74LS245三态门与数据总线相连。

计算机组成原理实验报告

湖南师范大学工程与设计学院计算机组成原理实验报告姓名:年级:2014级专业:计算机科学与技术学号:**********任课教师:***开课时间:2015~2016学年第二学期湖南师范大学工程与设计学院实验数据报告单实验课程:计算机组成原理实验题目:基本运算器实验实验日期:2016年 6月13日专业:计算机年级:2014级班级:五班姓名:一.实验目的:1.了解运算器的组成结构2.掌握运算器的工作原理二..实验内容:主要内容:该试验旨在了解运算器内部运算过程及组成结构,并能进行一些简单的数据运算。

该实验通过一片CPLD来实现运算器部件的功能,在接好的实验电路上,用CMA软件将数据加载加入内存,最终实现通过设置CON单元的S3、S2、S1、S0以及时序T1、T2、T3、T4的不同值来实现不同的功能。

表现在:用S3、S2、S1、S0的不同值并配合CN的值来实现将寄存器A、寄存器B中的两个数进行逻辑运算、移位运算、算术运算,并且加上时间脉冲的加入,并且能够准确的实现值的输出。

结果体现在:用FC灯亮表示有进位,FZ灯亮表示零标志,D7…D0灯显示通过运算后得出来的值。

三.实验原理图:图一(运算器原理图)四.实验数据与分析:0000:功能是F=A(直通),因为A=65,所以F=65,且没有进位,标志位也没有变化,所以FC=0,FZ=0. 0001: 功能是F=B (直通),因为A=A7,所以F=A7,且没有进位,标志位也没有变化,所以FC=0,FZ=0. 0010: 功能是F=AB,也就是A与B的逻辑与,所以F=25, 且没有进位,标志位也没有变化,所以FC=0,FZ=0. 0011:功能是F=A+B,也就是A与B的逻辑或,所以F=E7, 且没有进位,标志位也没有变化,所以FC=0,FZ=0. 0100: 功能是F=/A,0101:功能是F=A不带进位循环右移B(取低三位)位。

0110:功能是当CN=0时,F=A逻辑右移一位;当CN=1时,F=A带进位逻辑右移一位。

血液组成成分实验报告

一、实验目的1. 了解血液的组成成分。

2. 掌握血液分层实验的操作方法。

3. 熟悉血浆、血细胞和血小板的观察方法。

二、实验原理血液由血浆和血细胞两部分组成。

血浆约占血液的55%,主要成分是水、蛋白质、无机盐等。

血细胞包括红细胞、白细胞和血小板,其中红细胞约占血液的45%,白细胞和血小板占血液的5%左右。

血液分层实验是将血液加入抗凝剂后,静置一段时间,血液会自然分层。

上层为血浆,下层为血细胞。

通过观察血浆和血细胞,可以了解血液的组成成分。

三、实验材料与仪器1. 实验材料:新鲜血液、抗凝剂(如柠檬酸钠)、载玻片、显微镜、吸管等。

2. 实验仪器:离心机、烧杯、试管等。

四、实验步骤1. 将新鲜血液加入抗凝剂,充分混匀。

2. 将混匀后的血液倒入试管中,静置一段时间。

3. 观察血液分层情况,上层为血浆,下层为血细胞。

4. 将上层血浆小心吸出,滴在载玻片上,观察其颜色、透明度等特征。

5. 将下层血细胞小心吸出,滴在载玻片上,观察其颜色、形状、大小等特征。

6. 使用显微镜观察白细胞和血小板。

五、实验结果与分析1. 血浆:呈淡黄色,半透明,主要成分是水、蛋白质、无机盐等。

血浆具有运输营养物质、激素、氧气等功能。

2. 血细胞:包括红细胞、白细胞和血小板。

a. 红细胞:呈暗红色,不透明,无细胞核,富含血红蛋白。

红细胞主要负责运输氧气和二氧化碳。

b. 白细胞:呈白色,有细胞核,体积较大。

白细胞具有吞噬、消化病原体等功能,参与人体免疫功能。

c. 血小板:呈白色,无细胞核,体积最小。

血小板具有止血、凝血等功能。

六、实验结论通过本次实验,我们了解了血液的组成成分,掌握了血液分层实验的操作方法,熟悉了血浆、血细胞和血小板的观察方法。

血液是人体重要的组成部分,具有运输、调节、防御等功能,对人体健康具有重要意义。

七、注意事项1. 实验过程中要严格遵守无菌操作原则,避免污染。

2. 操作时要小心谨慎,避免血液溅出。

3. 观察时注意观察细节,准确记录实验结果。

计算机组成原理实验报告

计算机组成原理实验报告实验⼀静态随机存取存贮器实验⼀.实验⽬的了解静态随机存取存贮器的⼯作原理;掌握读写存贮器的⽅法。

⼆.实验内容实验仪的存贮器MEM单元选⽤⼀⽚静态存贮器6116(2K×8bit)存放程序和数据。

CE:⽚选信号线,低电平有效,实验仪已将该管脚接地。

OE:读信号线,低电平有效。

WE:写信号线,低电平有效。

A0..A10: 地址信号线。

I/O0..I/O7:数据信号线。

SRAM6116存贮器挂在CPU的总线上,CPU通过读写控制逻辑,控制MEM的读写。

实验中的读写控制逻辑如下图:读写控制逻辑M_nI/O⽤来选择对MEM还是I/O读写,M_nI/O = 1,选择存贮器MEM;M_nI/O = 0,选择I/O设备。

nRD = 0为读操作;nWR = 0为写操作。

对MEM、I/O的写脉冲宽度与T2⼀致;读脉冲宽度与T2+T3⼀致,T2、T3由CON单元提供。

存贮器实验原理图存贮器数据信号线与数据总线DBus相连;地址信号线与地址总线ABus相连,6116的⾼三位地址A10..A8接地,所以其实际容量为256字节。

数据总线DBus、地址总线ABus、控制总线CBus与扩展区单元相连,扩展区单元的数码管、发光⼆极管上显⽰对应的数据。

IN单元通过⼀⽚74HC245(三态门),连接到内部数据总线iDBus上,分时提供地址、数据。

MAR由锁存器(74HC574,锁存写⼊的地址数据)、三态门(74HC245、控制锁存器中的地址数据是否输出到地址总线上)、8个发光⼆极管(显⽰锁存器中的地址数据)组成。

T2、T3由CON单元提供,按⼀次CON单元的uSTEP键,时序单元发出T1信号;按⼀次uSTEP键,时序单元发出T2信号;按⼀次uSTEP键,时序单元发出T3信号;再按⼀次uSTEP键,时序单元⼜发出T1信号,……按⼀次STEP键,相当于按了三次uSTEP键,依次发出T1、T2、T3信号。

其余信号由开关区单元的拨动开关模拟给出,其中M_nI/O应为⾼(即对MEM 读写操作)电平有效,nRD、nWR、wMAR、nMAROE、IN单元的nCS、nRD 都是低电平有效。

计算机组成原理运算器实验报告

计算机组成原理运算器实验报告计算机组成原理实验⼀运算器实验⼀、实验⽬的:1、掌握简单运算器的数据传输⽅式。

2、验证运算功能发⽣器(74LS181)及进位控制的组合功能。

⼆、实验要求:完成不带进位及带进位算数运算实验、逻辑运算实验,了解算数逻辑运算单元的运⽤。

三、实验原理:74LS181是4位算术逻辑运算器,⽤两个74LS181并联可以实现8位运算,为了实现双操作的运算,ALU 的输⼊端分别由两个锁存器DR1,DR2锁存数据。

数据显⽰灯和数据总线相连接,⽤来显⽰数据总线上的内容。

由于实验电路中的时序信号均已连接⾄W /RUIT相应的时序信号引出端,只要微动开关,即可获得实验所需的单脉冲。

四、实验连接:1.⼋位运算器控制信号连接:S3,S2,S1,S0,M ,/CN ,LDDR1,LDDR2,LDCZY ,/SW-B ,/ALU-B ,Cn+4 Cn+4I2.完成连接并检查⽆误后接通电源。

五、实验仪器状态设定:在闪动的“P.”状态下按动“增址”命令键,使LED 显⽰器⾃左向右第⼀位显⽰提⽰符“H ”,表⽰本装置已进⼊⼿动单元实验状态。

五、实验项⽬:(⼀)算数运算实验拨动⼆进制数据开关向DR1和DR2寄存器置数(灯亮为1,灯灭为0)。

步骤如下:[CBA=001] [LDDR1=1] [LDDR1=0][LDDR2=0] [LDDR2=1]数据开关(01100101)三态门寄存器DR1(01100101)数据开关(10100111)寄存器DR2 (10100111)[“按STEP”] [“按STEP”] 然后检查数据:1.关闭数据输⼊三态门(CBA=000)2.打开ALU输出三态门(CBA=010)3.当置S3,S2,S1,S0,M为11111时,总线指⽰灯显⽰DR1中的数4.当置S3,S2,S1,S0,M为10101时,总线指⽰灯显⽰DR2中的数算数运算(不带进位)实验:置CBA=010,S3,S2,S1,S0,M,/CN为100101,LDCZY=0,则数据总线指⽰灯显⽰00001100(0CH)(⼆)进位控制实验(1)进位标志清零CBA=000 置S3,S2,S1,S0,M为00000 置/CN为0,LDCZY为1 按STEP (2)向DR1和DR2置数(同上)(3)验证进位运算及进位锁存功能,使/CN=1,LDCZY=1,来进⾏算数运算。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

组成实验报告 Prepared on 22 November 2020 上海理工大学光电信息与计算机工程学院 《计算机组成》实验报告

专 业计算机科学与技术 姓名 陈晓阳 学 号 年 级2015级 指导教师邬春学 成 绩: 教师签字: 目录

实验一 汇编实验一 一、实验目的 1)掌握汇编的基本语法 二、实验环境 三、实验内容 编程计算表达式 x=a x b + c - d/(e+f) 其中x、a、b、c、d、e、f均为双字节整数。 地址分别为X、A1、B1、C1、D1、E1、F1 四、实验代码及截图

1) data segment ;input data segment code here A1 DB 2 B1 DB 1 C1 DB 3 D1 DB 4 E1 DB 1 F1 DB 4 X1 DB data ends stack segment ;input stack segment code here stack ends code segment assume cs:code,ds:data,ss:stack start: mov ax,data mov ds,ax ;input code segment code here mov AL,A1 MUL BL ADD AL,C1 SUB AL,D1 MOV BL,E1 ADD BL,F1 DIV BL MOV X1,AL mov ah,4ch int 21h code ends end start 1)

实验二 汇编实验二

一、 实验目的 学习间接寻址、数组和转移指令的用法 二、实验环境

三、实验内容 1)一个由3个元素组成的整数数组,已经存放在主存的连续存储单元中,数组的起始地址为AS。设AS{10h,20h,30h}。编程实现:将数组AS中的元素向右循环移动一个位置,例如移位后变成{30h,10h,20h}。编程实现:将AS中最大元素和最小元素分别存于Max和Min中。 2)将字符串source中的内容复制到target中,并显示输出。 四、实验代码及截图 1) data segment

AS DW 10H,20H,30H ;input data segment code here MAX DW 0 MIN DW 0;数据初始 data ends stack segment ;input stack segment code here stack ends code segment assume cs:code,ds:data,ss:stack start: mov ax,data mov ds,ax;将data给ds mov cx,0;cx赋初始值0 mov si,offset as;将data偏移地址存到si mov ax,[si];data内容给ax add si,2;si加2 Li:mov bx,[si] mov [si],ax mov ax,bx add si,2 add cx,1 cmp cx,2 JNZ Li sub si,6 mov [si],ax;将30移位到第一位 mov ax,[si] mov MIN,ax mov MAX,ax;初始化MIN,MAX add si,2 mov bx,[si] cmp bx,ax JL L1;bx mov MAX,bx;如果bx>=ax,把bx值存入MAX add si,2;si后移一个数据 mov dx,[si] cmp bx,dx JG L4 mov MAX,dx;如果bx>dx则执行L4,否则将dx存入MAX L1:add si,2 mov bx,[si] cmp bx,ax JL L2;bx mov MAX,bx L4:cmp ax,dx JG L5 L5:mov MIN,dx ;将dx存入MIN L2:mov bx,[si] sub si,2 mov ax,[si] cmp bx,ax JG L3;bx大于ax则跳转L3,否则将bx存入MIN mov MIN,bx L3:mov MIN,ax;此时ax为10,将其存入MIN mov ah,4ch int 21h code ends end start 2) data segment source db 'Hello world$' data ends data1 segment target db 30 dup() data1 ends stack segment ;input stack segment code here stack ends code segment assume cs:code,ds:data,ss:stack start: mov ax,data mov ds,ax;data存入ds mov ax,data1 mov es,ax;data1存入es lea si,source;source地址存到si lea di,target;target地址存到di mov cx,2 std;DF=1 rep movsb;将si中字符串复制到di中 lea dx,target mov ah,9 int 21h;输出复制得到的字符串 mov ah,4ch int 21h code ends end start

1) 2)

实验三 汇编实验三

一、实验目的 1)学习逻辑运算指令和移位指令的用法 二、实验环境 三、实验内容 1)将一个指定字符串进行异或加密,每个单字符的密钥(0-255)保存在数组Key中。程序运行过程:显示明文,显示所产生的密文,显示解密后的明文。例如key = {125,248,16,8,26} 2)将一个指定字符串进行循环移位加密。每个单字符的密钥(-7~7)保存在数组Key中。程序运行过程:显示明文,显示所产生的密文,显示解密后的明文.例如key = {-2,2,1,0,-1},其中负数表示循环左移,正数表示循环右移,0不变,数字表示移动的位数 四、实验代码及截图 1)data segment

string db 'Hello$';明文 key db 125,248,16,8,26;密钥 msg1 db ' ming wen:$' msg2 db ' mi wen:$' data ends stack segment ;input stack segment code here stack ends code segment assume cs:code,ds:data,ss:stack start: mov ax,data mov ds,ax lea dx,msg1 mov ah,09h int 21h lea dx,string mov ah,09h int 21h;输出加密前明文 mov cx,5 loop1:mov bx,cx mov al,string[bx-1] xor al,key[bx-1] mov string[bx-1],al loop loop1;明文加密 lea dx,msg2 mov ah,09h int 21h lea dx,string mov ah,09h int 21h;输出加密后的密文 mov cx,5 loop2:mov bx,cx mov al,string[bx-1] xor al,key[bx-1] mov string[bx-1],al loop loop2;解密密文 lea dx,msg1 mov ah,09h int 21h lea dx,string mov ah,09h int 21h;输出解密的明文 mov ah,4ch int 21h code ends end start 2)data segment string db 'Hello$';待加密明文 key db -2,2,1,0,-1;密钥 msg1 db ' ming wen:$' msg2 db ' mi wen:$' data ends stack segment ;input stack segment code here stack ends code segment assume cs:code,ds:data,ss:stack start: mov ax,data mov ds,ax lea dx,msg1 mov ah,09h int 21h lea dx,string mov ah,09h int 21h;输出加密前的明文 mov cx,5 mov al,0 loop1:mov bx,cx push cx;对cx压栈 mov cl,key[bx-1] cmp cl,al jl t1;若密钥小于0则跳转到tl rol string[bx-1],cl;密钥不小于0则左循环移位 jmp s1;跳至sl t1:neg cl;若密钥小于0,则取补,变为正数进行操作 ror string[bx-1],cl;右循环移位 s1:pop cx;弹栈