东南大学信息学院计算结构POC实验报告

东南大学信息学院通信电子线路实验实验报告

3.1 常用仪器的使用04012540 印友进一、实验内容1、说明频谱仪的主要工作原理,示波器测量精度与示波器带宽、与被测信号频率之间关系。

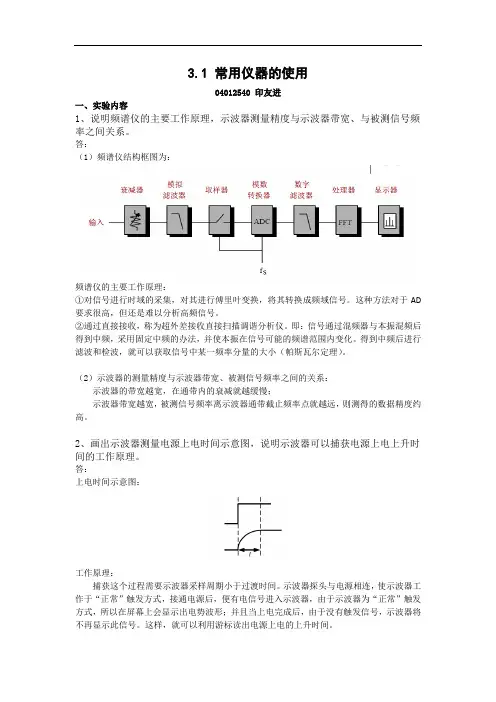

答:(1)频谱仪结构框图为:频谱仪的主要工作原理:①对信号进行时域的采集,对其进行傅里叶变换,将其转换成频域信号。

这种方法对于AD 要求很高,但还是难以分析高频信号。

②通过直接接收,称为超外差接收直接扫描调谐分析仪。

即:信号通过混频器与本振混频后得到中频,采用固定中频的办法,并使本振在信号可能的频谱范围内变化。

得到中频后进行滤波和检波,就可以获取信号中某一频率分量的大小(帕斯瓦尔定理)。

(2)示波器的测量精度与示波器带宽、被测信号频率之间的关系:示波器的带宽越宽,在通带内的衰减就越缓慢;示波器带宽越宽,被测信号频率离示波器通带截止频率点就越远,则测得的数据精度约高。

2、画出示波器测量电源上电时间示意图,说明示波器可以捕获电源上电上升时间的工作原理。

答:上电时间示意图:工作原理:捕获这个过程需要示波器采样周期小于过渡时间。

示波器探头与电源相连,使示波器工作于“正常”触发方式,接通电源后,便有电信号进入示波器,由于示波器为“正常”触发方式,所以在屏幕上会显示出电势波形;并且当上电完成后,由于没有触发信号,示波器将不再显示此信号。

这样,就可以利用游标读出电源上电的上升时间。

3、简要说明在FM 调制过程中,调制信号的幅度与频率信息是如何加到FM 波中的?答:载波的瞬时角频率为()()c f t k u t ωωΩ=+,(其中f k 为与电路有关的调频比例常数)已调的瞬时相角为000t ()()t t c f t dt t k u t dt θωωθΩ=++⎰⎰()=所以FM 已调波的表达式为:000()cos[()]t om c f u t U t k u t dt ωθΩ=++⎰当()cos m u t U t ΩΩ=Ω时,00()cos[sin ]om c f u t U t M t ωθ=+Ω+其中f M 为调制指数其值与调制信号的幅度m U Ω成正比,与调制信号的角频率Ω反比,即m f fU M k Ω=Ω。

东南大学信息学院-计算机结构与逻辑设计课件运算电路

精选PPT

16

对电路的检查方法

先查功能

功能不对,查电路——查仪器—

—查器件

网络

&

A

&

&

1

精选PPT

17

实验报告的要求

实验的逻辑图和电路图要画清楚,图上 要标明所使用的器件。输入信号源和输 出负载。

A&

B

123

AB

B怎样得到?

精选PPT

18

实验报告的要求

36

请解释图4.29电路中

1.MC14561是什么电路?如何 设计?(几种方法的优缺点)

2.触发器起什么作用?

3.用集成移位寄存器设计图中的 移位电路

精选PPT

37

集成ALU的功能表有何启示?

精选PPT

38

二,思考题

精选PPT

39

学习总结

精选PPT

40

一~三章——基础(理论,方法) 四~八章——应用

计算机结构与逻辑设计

(第九次课)

强化班04级

精选PPT

1

测验评述

精选PPT

2

P.409 题 3.43

求下面计数器的模

&

Vcc

Q1 Q2 Q3 Q4 CO

EN

LD

CP

74161

CI

CR

D1 D2 D3 D4

Q1 Q2 Q3 Q4 CO

EN

LD

74161

CI

CR

D1 D2 D3 D4

精选PPT

3

-----------

M = 16 × 10 + 3 + 1 = 160 + 4 = 164

东南大学微机实验报告10页10页

东南大学微机实验报告10页10页

1. 简介:介绍实验目的、实验背景、研究问题和实验方法等。

2. 材料和方法:介绍实验材料和方法,例如使用的硬件、软件和技术等。

3. 结果:给出实验结果,例如测试数据和图表等。

4. 讨论:对结果进行讨论,对实验中遇到的问题进行解释和分析,并提出结论和建议。

5. 结论:总结实验过程、重要结果和研究结论,以及对未来工作的展望。

以下是一份典型的东南大学微机实验报告的框架,可以参考使用。

实验题目:xxx

实验时间:xxxx.xx.xx

实验地点:东南大学计算机实验室

学生姓名:xxx

实验报告结构

1. 简介

1.1 实验目的

1.3 研究问题

2. 材料和方法

2.1 硬件

2.3 技术

3. 结果

3.1 测试数据

4. 讨论

4.2 问题解释

4.3 建议

5. 结论

5.3 未来展望

参考文献: 1. xxxx。

东南大学信息学院-计算机结构与逻辑设计课件(MSI电路)

0 1 2 3 4 5 6 7 B0

从数据选择器的输出(F)是否

为低电平可以判断A与B是否相 1 等。——数据比较器 &

0 0

EN

0 0 1 2 3 4 5 6 7

7

BIN/OCT

A2 1 A A1 0 A0 1

4 2 1 0 1 2 3 4 5 6 7

1

0

0

&

EN

1 1 1 1 1 0 1 1

CO

CO Y1 B CI A 0 S Y2 1 1 00 01 1 1 11 10 1

4,0 4,1 4,2 4,3 5,0 5,1 5,2 5,3

S

二,思考题

译码器与数据选择器在电路结构

上有何异同? 用译码器与用数据选择器实现组 合逻辑函数的方法有何异同?各 有什么优、缺点?

学习总结

组合逻辑设计方法 用途: 非常大——接口逻辑 基本方法: 最小化——必须掌握,是计算机辅助逻 辑简化的理论支撑 标准化——方便、清楚、易修改,硬件 软化,是可编程器件的结构支撑

&

?

& EN

1

0 0

0 1 2 3 4 5 6 7

S

&

CO

CO = f(A,B,C) = Σ m ( 3, 5, 6, 7) S = f(A,B,C) = Σ m ( 1, 2, 4, 7) 0 A B C 0 0 0 1 0 1 1 1 EN MUX 2 0 1 G– 7 0 0 1 2 3 4 5 6 7 0 A B C 0 1 1 0 1 0 0 1 EN MUX 2 0 1 G– 7 0 0 1 2 3 4 5 6 7

0 B2 1 B B1 0 B0 1

东南大学计算机系汇编试验报告

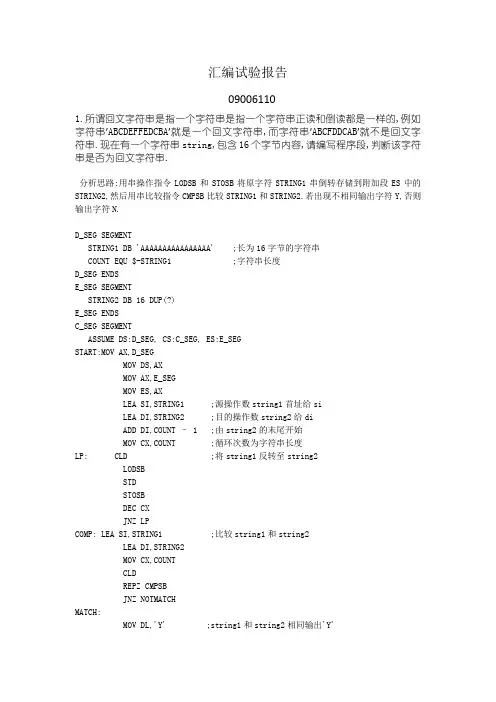

汇编试验报告090061101.所谓回文字符串是指一个字符串是指一个字符串正读和倒读都是一样的,例如字符串’ABCDEFFEDCBA’就是一个回文字符串,而字符串’ABCFDDCAB’就不是回文字符串.现在有一个字符串string,包含16个字节内容,请编写程序段,判断该字符串是否为回文字符串.分析思路:用串操作指令LODSB和STOSB将原字符STRING1串倒转存储到附加段ES中的STRING2,然后用串比较指令CMPSB比较STRING1和STRING2.若出现不相同输出字符Y,否则输出字符N.D_SEG SEGMENTSTRING1 DB 'AAAAAAAAAAAAAAAA' ;长为16字节的字符串COUNT EQU $-STRING1 ;字符串长度D_SEG ENDSE_SEG SEGMENTSTRING2 DB 16 DUP(?)E_SEG ENDSC_SEG SEGMENTASSUME DS:D_SEG, CS:C_SEG, ES:E_SEGSTART:MOV AX,D_SEGMOV DS,AXMOV AX,E_SEGMOV ES,AXLEA SI,STRING1 ;源操作数string1首址给siLEA DI,STRING2 ;目的操作数string2给diADD DI,COUNT – 1 ;由string2的末尾开始MOV CX,COUNT ;循环次数为字符串长度LP: CLD ;将string1反转至string2LODSBSTDSTOSBDEC CXJNZ LPCOMP: LEA SI,STRING1 ;比较string1和string2LEA DI,STRING2MOV CX,COUNTCLDREPZ CMPSBJNZ NOTMATCHMATCH:MOV DL,'Y' ;string1和string2相同输出'Y'MOV AH,02HINT 21HJMP EXITNOTMATCH:MOV DL,'N' ;string1和string2不同输出'N'MOV AH,02HINT 21HJMP EXITEXIT: MOV AH,4CHINT 21HC_SEG ENDSEND START2.将ELEMS中的100个字节数据的位置颠倒过来(即第一个字节和第100个字节的内容交换,第二个字节和第99个字节的内容交换……).分析思路:为了方便程序只做了将6个字节颠倒过来.程序先将原ELEMS打印到屏幕上,颠倒后再将新ELEMS打印的屏幕上.颠倒采用的方法同题1,使用串操作指令LODSB和STOSB将原串颠倒,再用串传送MOVSB将串复制到原来的地方.D_SEG SEGMENTELEMS DB '12345' ,'!' ;6个字节长的字符串LEN EQU $-ELEMS ;字符串长度D_SEG ENDSE_SEG SEGMENTSTRING DB 200 DUP(?)E_SEG ENDSC_SEG SEGMENTASSUME DS:D_SEG, ES:E_SEG, CS:C_SEGSTART:MOV AX,D_SEGMOV DS,AXMOV AX,E_SEGMOV ES,AXCALL PRINT ;将ELEMS输出到显示器LEA SI,ELEMSLEA DI,STRINGADD DI,LEN - 1MOV CX,LENLP:CLD ;将ELEMS反向存到string中LODSBSTDSTOSBDEC CXJNZ LPCOPY:MOV AX,E_SEG ;将string中的复制到原来ELEMS的地方MOV DS,AXMOV AX,D_SEGMOV ES,AXLEA SI,STRINGLEA DI,ELEMSMOV CX,LEN ;重复次数为串长度REP MOVSB ;重复CALL PRINT ;将新ELEMS输出到显示器MOV AH,4CHINT 21HPRINT PROC NEAR ;打印程序,打印ELEMSLEA BX,ELEMSMOV BYTE PTR[BX+LEN],'$' ;串尾部加'$'LEA DX,ELEMSMOV AH,09H ;调用字符串输出INT 21HMOV DL,0AHMOV AH,02HINT 21HMOV DL,0DHMOV AH,02HINT 21HRETPRINT ENDPC_SEG ENDSEND START3.请编写完整程序在一个升序字节数组中查找数N,找到后将此数从数组中删除,并使得CF=0,没找到返回CF=1.数组的首地址和末地址为A_HEAD和A_END.分析思路:采用二分查找的办法.首先将要寻找的数N与数组第一个数和最后一个数比较,当小于第一个或大于最后一个置CF=1, 如果等于第一个或最后1个置CF=0,同时将A_HEAD加1或将A_END减1.如果都不符合,调用二分查找的递归程序.递归首先判断终止条件(A_HEAD等于A_END),符合则CF=0,跳出至EXIT;然后计算中间位地址mid= (head+end)/2,比较要找的数与mid的大小,3种情况:一.当N=mid,置CF=0,然后将后面的元素依次前移一位,最后A_END减1.二.当N>mid,将mid地址给A_HEAD,调用二分查找三.当N<mid,将mid地址给A_END,调用二分查找D_SEG SEGMENTA_HEAD DW $+2 ;定义A_HEADARRAY DB 1,2,3,4,5,6,7,8,9 ;定义的升序字节数组A_END DW $-1 ;定义A_ENDN EQU 5 ;定义要找的数MID DB ?D_SEG ENDSC_SEG SEGMENTASSUME DS:D_SEG,CS:C_SEGSTART:MOV AX,D_SEGMOV DS,AXMOV BL,BYTE PTR[A_HEAD]CMP BL,N ;比较N和head JE TERM1JA TERM2MOV BL,BYTE PTR[A_END]CMP BL,N ;比较N和end JE TERM3JB TERM4MOV DX,A_HEAD ;DX存放head的地址MOV AX,A_END ;AX存放end的地址JMP HALFTERM1:CLC ;N=HEAD;置CF=0INC A_HEAD ;A_HEAD 后移一位,即删除JMP EXITTERM2:STC ;N<HEAD;置CF=1JMP EXITTERM3:CLC ;N=END;置CF=0DEC A_END ;A_END 前移一位,即删除JMP EXITTERM4:STC ;N>END;置CF=1JMP EXITHALF: CMP AX,DXJZ FOURMOV BX,DXADD BX,AX ;A_HEAD和A_END 相加,head + endSHR BX,1 ;折半,BX存放mid的地址CMP BYTE PTR[BX],NJA ONE ; N<midJB TWO ; N>midJZ THREE ; N=midONE: MOV DX,BX ;用mid的地址替换head的地址CALL HALFTWO: MOV AX,BX ;用mid的地址替换end的地址CALL HALFTHREE:CLC ;置CF=0MOV CX,A_ENDSUB CX,BX ;循环次数LP:MOV AL,[BX+1] ;删除元素,将后面的元素前移一位MOV [BX],ALINC BXDEC CXLOOP LPDEC A_ENDJMP EXITFOUR: STC ;没找到相应的N;置CF=1JMP EXIT EXIT: MOV AH,4CH INT 21HC_SEG ENDSEND START。

东南大学第2章-计算机逻辑实验报告-门电路组合逻辑

东南大学电工电子实验中心实验报告一、实验目的(1)掌握TTL和CMOS器件的静态特性和动态特性测量方法及这些特性对数字系统设计的影响;(2)掌握通过数字器件手册查看器件静态和动态特性参数;(3)掌握不同结构的数字器件之间的互连;(4)掌握OC门和三态门的特性和使用方法;(5)加深示波器测量技术的训练;(6)掌握小规模组合逻辑的工程设计方法;(7)了解竞争和冒险的产生原因,消除方法,掌握用示波器和逻辑分析捕捉毛刺的方法。

二、实验仪器三、实验原理实验原理见教材第2章。

预习思考题如下:1、下图中的两个电路在实际工程中经常用到,其中反相器为74LS04,电路中的电阻起到了保证输出电平的作用。

分析电路原理,并根据器件的直流特性计算电阻值的取值范围。

N 个N 个(a )(b )答:①电路(a)使用条件是驱动门电路固定输出为低电平当OL V V =时,如果有N 个负载门且20>N ,将使max max OL IL I NI >,而m a x OL I I >将使max OL OL V V >,所以需如图(a )所示接下拉电阻R 。

()()Ω=-=-≤≤-≤=12584.05.030max max max maxmax max max2N OL IL OL OL OL IL OL mAN VI NI V R V R I NI V R I②电路(b)使用条件是驱动门电路固定输出为高电平当OH V V =时,如果有N 个负载门且20>N ,将使max max O H IH I NI >,而m ax OH I I >将使min O H O H V V <,所以需如图(b )所示接上拉电阻R 。

()()()Ω=--=--≤≥--≥-=k 5.114.002.07.2555530max max min minmax max min2N OH IH OH OH OH IH OH mAN VI NI V V R V R I NI V V R I V2、下图中的电阻起到了限制前一级输出电流的作用,根据器件的直流特性计算电阻值的取值范围。

东南大学计算机系接口实验报告样板

东南大学接口实验报告09006110 090061112008-12-17实验2-11.将8253计数器0设置为方式0,计数器初值设置为N(N≤0FH)。

将实验台上单脉冲接到CLK0 上,用手动逐个输入单脉冲,编程使计数值在计算机屏幕上显示(查询方式),并同时用逻辑笔观察OUT0电平变化(当输入N+1个脉冲后OUT0变高电平)。

2.实验电路3.实验程序流程图及代码#include <stdio.h>#include <conio.h>#include "ApiEx.h"#pragma comment(lib,"ApiEx.lib")void main(){BYTE data;printf("----------EXP2_1-----------\n");printf("Press any key to begin!\n\n");getch();printf("Press any key to exit!\n");if(!Startup()){printf("ERROR:Open Device Error!\n");return;}//8253片选地址为0x280PortWriteByte(0x283,0x10); //给计算器0写控制字00010000 B = 10 H PortWriteByte(0x280,0x0A); //计算器0置初值0A Hwhile(!kbhit()) //判断是否有键按下{PortReadByte(0x280,&data); //读计数器0的值Sleep(1000); //延迟一秒钟printf("%d\n",data);}Cleanup();}实验2-21. 将计数器0,计数器1分别设置为方式3,利用这两个计数器,将实验台上的一个1MHz 的方波信号分频为1Hz的方波(做好8253初始化工作),并将此方波接到L7上,观察L7 以周期为1秒的频率闪烁。

东南大学电路实验实验报告

电路实验实验报告第二次实验实验名称:弱电实验院系:信息科学与工程学院专业:信息工程姓名:学号:实验时间:年月日实验一:PocketLab的使用、电子元器件特性测试和基尔霍夫定理一、仿真实验1.电容伏安特性实验电路:图1-1 电容伏安特性实验电路波形图:图1-2 电容电压电流波形图思考题:请根据测试波形,读取电容上电压,电流摆幅,验证电容的伏安特性表达式。

解:()()mV wt wt U C cos 164cos 164-=+=π,()mV wt wt U R sin 10002cos 1000=⎪⎭⎫ ⎝⎛-=π,us T 500=;()mA wt RU I I R R C sin 213.0===∴,ππ40002==T w ; 而()mA wt dtdu CCsin 206.0= dtdu CI CC ≈⇒且误差较小,即可验证电容的伏安特性表达式。

2.电感伏安特性实验电路:图1-3 电感伏安特性实验电路波形图:图1-4 电感电压电流波形图思考题:1.比较图1-2和1-4,理解电感、电容上电压电流之间的相位关系。

对于电感而言,电压相位 超前 (超前or 滞后)电流相位;对于电容而言,电压相位 滞后 (超前or 滞后)电流相位。

2.请根据测试波形,读取电感上电压、电流摆幅,验证电感的伏安特性表达式。

解:()mV wt U L cos 8.2=, ()mV wt wt U R sin 10002cos 1000=⎪⎭⎫ ⎝⎛-=π,us T 500=; ()mA wt RU I I R R L sin 213.0===∴,ππ40002==T w ; 而()mV wt dtdi LLcos 7.2= dtdi LU LL ≈⇒且误差较小,即可验证电感的伏安特性表达式。

二、硬件实验1.恒压源特性验证表1-1 不同电阻负载时电压源输出电压2.电容的伏安特性测量图1-5 电容电压电流波形图3.电感的伏安特性测量图1-6 电感电压电流波形图4.基尔霍夫定律验证表1-2 基尔霍夫验证电路思考题:1.根据实验数据,选定节点,验证KCL 的正确性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2-1 POC实验报告 目录 目录 .............................................................................................................................................. 1-1 1 实验目的 ............................................................................................................................... 1-1 2 实验任务 ............................................................................................................................... 2-1 3 架构说明 ............................................................................................................................... 3-2 4 仿真信号设计与结果分析 ................................................................................................... 4-3 4.1 打印机模块 ............................................................................................................... 4-3 4.1.1 仿真信号说明与设计 ................................................................................... 4-3 4.1.2 仿真结果与分析 ........................................................................................... 4-3 4.2 POC模块 .................................................................................................................. 4-3 4.2.1 仿真信号说明与设计 ................................................................................... 4-3 4.2.2 仿真结果与分析 ........................................................................................... 4-4 4.3 整体模块 ................................................................................................................... 4-4 5 总结与补充 ........................................................................................................................... 5-4 5.1 查询模式 ................................................................................................................... 5-5 5.2 中断模式 ................................................................................................................... 5-5 6 附录....................................................................................................................................... 6-6

1 实验目的 本实验的目的是设计一块简易的POC(并行输出控制器),从而连接系统总线和打印机。通过本次实验,可以初步了解输入输出、存储模块的设计,为接下来CPU的设计奠定良好的基础。

2 实验任务 利用ISE和VHDL语言设计出POC模块和打印机模块,并且通过仿真测试并验证其主要功能的实现。 仿真主要以中断响应工作模式为主。而查询模式也需要了解,这部分分析内容都将放在总结环节。 3-2

3 架构说明 整体由POC、Printer两个模块组成,整体的输入端口有: CS:片选,实际情况为地址总线13 A:寄存器选取; D_bus:数据总线; CLK:时间信号; R_W:读取/写入控制,0为读取,1为写入; 输出端口为: IRQ:中断请求信号,低电平有效; CNT:计数器,用于模拟打印机的忙碌情况。 4-3

4 仿真信号设计与结果分析 4.1 打印机模块 4.1.1 仿真信号说明与设计 RDY:输出信号,当Printer处于空闲状态时为1,工作状态为0; TR:输入信号,表示准备传输数据,设置为保持一个时钟周期; PD:输入信号,表示当前准备打印的数据; CLK:时钟信号,虽然设计图上没有,但为了模拟打印机工作采用了计数器,相应的也暂时引入了时钟信号。 CNT:输出信号,用以模拟打印机的过程,输出用以更直观的表示。

4.1.2 仿真结果与分析

① 初始状态时打印机显然不处于工作状态,因而RDY信号保持为1; ② 当PD数据填充完毕后,TR脉冲信号到来; ③ TR脉冲上升沿到来的同时,RDY信号置为0,表示正在忙碌; ④ 此时打印机开始打印,表示为cnt计数,当计数完毕后RDY信号重新为1。

4.2 POC模块

4.2.1 仿真信号说明与设计 RDY:输入信号,用以判断打印机是否空闲 CS:输入信号,表示片选,实际使用时为CPU是否选中该芯片(用前13根地址线) A:输入信号,地址线的后3位,表示实际选择哪个寄存器,本次设计001为选取数据寄存器,010为选取状态寄存器。 CLK:时钟信号。 CNT:输出信号,用以模拟打印机的过程,输出用以更直观的表示。 5-4

4.2.2 仿真结果与分析 ① 初始状态时,POC未被选中,打印机处于空闲状态,因此SR7被置为1,又由于默认工作在中断方式,因此在时钟上升沿之时便发出IRQ中断请求(低电平); ② 发送请求后,CPU选中芯片(即前13地址线选中CS),将数据总线的数据准备好,之后选中数据寄存器(A为001),并将POC的读写状态设置为写; ③ 经过一个时钟周期后tr脉冲输出表示数据准备传送,并且数据输出口准备好数据,打印机也回到忙碌状态。

4.3 整体模块 输入信号和POC模块大致相同,因此直接进行结果分析。

首先,IRQ信号产生,CPU选中POC芯片,随后选中数据寄存器并写入数据,之后经过几个时钟后,打印机开始工作,计数器开始计数。而CPU又去处理其他的工作(中断工作模式的体现)。 当打印机打印结束时,IRQ信号再度发出,等待CPU响应与再度传送数据。由于CPU当前也许正在进行不可中断的原子性操作,所以等待响应后再传送数据、再度打印是必要的。 由此仿真了整个工作流程。由于更复杂的仿真过程需要CPU的设计与介入,在此无法展示,我将在下文做相关文字补充。

5 总结与补充

通过仿真,我们对POC的工作方式和细节有了进一步的了解。然而,由于本次实验没有对CPU的特殊要求和说明,导致无法通过仿真的方式清晰的体现出中断方式和查询方式的具体区别。所有本应CPU输出、处理、反馈的信号都由人手工输入代替。因此,下面将对两种工作模式结合CPU作进一步阐述与补充。 5-5

5.1 查询模式 首先,CPU收到有关程序的请求,准备通过I/O接口联系POC模块,试图打印有关内容。CPU访问POC的相关状态寄存器(SR7),查看POC目前是否处于空闲状态。如果是,那就准备打印,否则,CPU处于轮询的状态。该进程内的每一个指令周期,CPU都在查询POC是否空闲,并不做其他的事情,直到POC处于空闲,并允许传输数据为止。 当CPU了解POC已准备就绪时,CPU便将有关内容分块传输到POC的数据缓存中。由于实际文件数据量较大,CPU将持续处于“轮询—传输—轮询—传输”直到文件打印完毕为之。 对于已经传输到POC的数据段,POC并不能立刻将其提交给打印机,因为当前打印机可能处于忙碌状态。当打印机用完当前数据(可能仅为一行)后,RDY信号为高电平,POC再将本段数据提交给打印机继续操作。 通过POC的TR信号和PD数据输出传送给打印机,再通过RDY信号判断当前打印机是否用完目前的数据。如果用完了,就将SR7置为空闲状态,以方便CPU提供新数据,否则SR7处于忙碌状态。 至此,整个查询模式的工作方式描述完毕。

5.2 中断模式 首先,CPU在某个时间点将POC的SR0置为1,即命令POC工作在中断模式。之后的前小部分和查询模式相同,CPU收到有关程序的请求,准备通过I/O接口联系POC模块,试图打印有关内容。CPU访问POC的相关状态寄存器(SR7),查看POC目前是否处于空闲状态,如果是,那就准备打印。 如果POC忙碌,CPU则继续忙其他的工作。由于POC事先已被CPU设置为中断模式,一旦POC处于空闲态,则会向CPU发出中断请求。此时,CPU会通过查中断向量表得知,是POC模块发出的请求,处理完当前的原子性操作或更高级的中断请求后,则响应POC中断,选中POC芯片进行有关操作。 由于实际文件数据量较大,CPU仍然会分块传输数据。此时CPU传完数据后继续忙其他工作,直到下一个中断来临。整个工作将持续处于“中断—传输—中断—传输”直到文件打印完毕为之。 具体的POC处理和前文类似,不再多言。