逻辑分析仪在芯片互联的应用

逻辑分析仪在CAN总线开发中的应用

逻辑分析仪─从入门到精通讲座(11) 逻辑分析仪在CAN总线开发中的应用1. 引言作为一种串行通讯技术,CAN-bus是20世纪80年代中后期适应汽车控制网络化要求而产生并迅速发展起来的,并已成为开放的国际标准通讯协议(ISO 11898),在众多领域得到了广泛的应用。

但是专用的CAN分析仪价格昂贵,本文介绍了一种基于逻辑分析仪的分析CAN总线的方法,不仅节省项目的资金,而且高效准确。

一般的逻辑分析仪中没有CAN 总线分析插件,CAN总线信号解码只能采用人工分析方法,即根据协议中规定的关系等许多情况进行分析。

这种分析方式不仅要求分析人员对该CAN协议非常熟悉,而且数据量大,分析过程容易出错。

本文采用了广州致远电子有限公司的高性能LAB6052逻辑分析仪和示波器相结合的方法对CAN-bus进行分析调试。

LAB6052逻辑分析仪的CAN-bus总线分析功能使得大多数开发人员可以很轻松的发现错误、调试硬件、加快开发进度,为高速度、高质量完成工程提供保障。

2. 测试原理尽管CAN是差分信号,而逻辑分析仪只支持单端信号的测量,但是根据CAN的电平特性,是可以通过合适的方法准确测量分析CAN总线数据的。

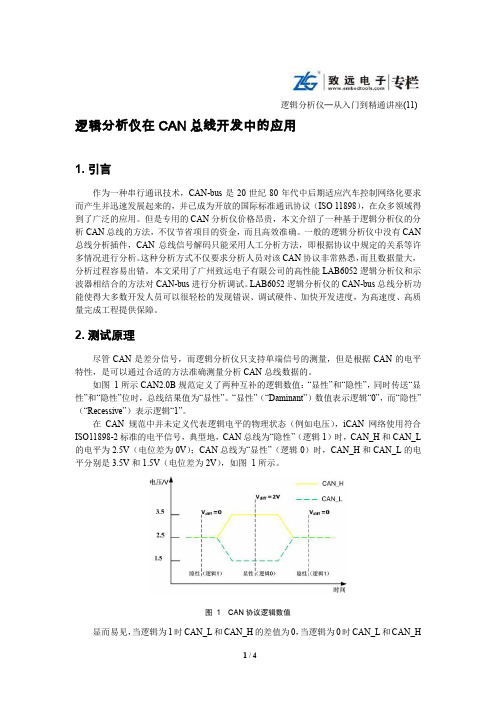

如图1所示CAN2.0B规范定义了两种互补的逻辑数值:“显性”和“隐性”,同时传送“显性”和“隐性”位时,总线结果值为“显性”。

“显性”(“Daminant”)数值表示逻辑“0”,而“隐性”(“Recessive”)表示逻辑“1”。

在CAN规范中并未定义代表逻辑电平的物理状态(例如电压),iCAN网络使用符合ISO11898-2标准的电平信号,典型地,CAN总线为“隐性”(逻辑1)时,CAN_H和CAN_L 的电平为2.5V(电位差为0V);CAN总线为“显性”(逻辑0)时,CAN_H和CAN_L的电平分别是3.5V和1.5V(电位差为2V),如图1所示。

图 1 CAN协议逻辑数值显而易见,当逻辑为1时CAN_L和CAN_H的差值为0,当逻辑为0时CAN_L和CAN_H差值为-2伏,用CAN_L的逻辑电平减去CAN_H的逻辑电平既可以得到CAN的时序逻辑,本文就是利用这一点达到测量的目的的,或者单端的CAN_L信号也是可以满足时序要求的,但是其稳定性明显不如双端的测量。

逻辑分析仪中Timing-State存储方式的应用

逻辑分析仪─从入门到精通讲座(18) 逻辑分析仪中Timing-State存储方式的应用1.引言在选购逻辑分析仪的过程中,用户关心的硬件指标主要有输入通道数量、采样速率、存储深度等参数。

随着逻辑分析仪技术的发展,这些指标正在不断提升,使用户在检测设备时更加方便:得以检测多通道数据,观测到微小脉宽信号,捕获长时间数据。

目前逻辑分析仪的采样速率已相当高,高达数百MHz甚至上GHz,数百Mpts的存储芯片已无法长时间记录数据,特别在某些长时间不活动、偶尔突发传输数据的设备中。

为了有效提高存储数据的实用率,某些高级的数据处理算法必须使用。

本文所介绍的致远电子LAB6000系列逻辑分析仪的Timing-State存储方式,正是在数据存储方面的一种优化算法。

2.常规存储方式的不足在常用的逻辑分析仪采样存储方式中,主要有定时采样(Timing)采样与状态(State)采样两种。

定时采样是采用逻辑分析内部时钟对数据进行采样,属于异步采样方式,用于测量目标设备的信号之间的定时关系。

状态采样是使用设备内部的信号作触发源,观测在该信号作用下各信号的电平状况,属于同步采样。

在这两种采样方式中,逻辑分析仪所记录的数据长度会随采样时间的增加而线性增长。

在目前高采样率的逻辑分析中,存储器的容量与带宽是个严重的挑战。

例如LAB6052在500MHz的采样时钟控制下,即2ns的采样时间间隔下,每通道16Mbit的存储深度单次可记录的时间是:16*1048576×2ns = 33.55ms。

此种数据记录方式没对数据做进一步的分析而直接存储,因此没能有效地利用存储器的容量。

在某些设备的应用中,信号的传输速率是相当高,但处于突发的传输模式,信号线在大部分时间是静止无效的,显然常用的数据记录方式无法在高采样率下对数据进行长时间记录。

在同类的电子测量设备数字示波器中,同样的问题也存在。

特别在既要观察细微信号,又要长时间观测全过程的测试场合中,此问题尤为突出,最常见的情况就是电源上电过程的测量。

基于FPGA逻辑分析仪的设计

基于FPGA逻辑分析仪的设计摘要本文介绍了一种基于FPGA(Field-Programmable Gate Array)的逻辑分析仪的设计。

逻辑分析仪是一种用于分析和调试数字信号的仪器。

设计中采用了FPGA作为核心逻辑芯片,实现了高速采集和处理数字信号的功能。

通过对比传统逻辑分析仪和FPGA逻辑分析仪的性能和优缺点,说明了该设计的重要性和实用性。

引言逻辑分析仪是一种非常重要的测试和调试工具,用于诊断数字信号的问题。

传统的逻辑分析仪采用SRAM作为存储原件,存储容量非常有限,难以满足现代数字系统复杂性的测试需要。

FPGA逻辑分析仪则采用FPGA芯片作为逻辑处理器,在实现高速采集和处理数字信号的同时,具有更高的存储容量和更快的测试速度,能够有效应对现代数字系统的测试需求。

FPGA逻辑分析仪的设计系统框图概述FPGA逻辑分析仪的系统框图如图1所示。

_________________| || FPGA逻辑 || 核心 ||_________________|||||PC信号采集 ||________||_________| || 数字信号采集模块 ||____________________|图1 FPGA逻辑分析仪系统框图FPGA逻辑处理器设计FPGA逻辑处理器需要具备高速采集和处理数字信号的能力。

设计中采用高速ADC(Analog-to-Digital Converter)进行信号采集,经过FPGA逻辑核心的处理之后,将数据传输至PC上进行分析和显示。

信号采集采用高速ADC进行数字信号采集,通过电缆连接至FPGA芯片,利用芯片内部的高速I/O口,实现数字信号采集与处理。

FPGA逻辑处理采用Verilog进行FPGA逻辑处理器设计,将逻辑核心分为两部分:一部分负责ADC信号采集,另一部分负责信号处理和转换。

其中,采集部分采用FPGA内置模块实现,处理部分采用自行设计的模块,实现对数字信号的快速处理和转换。

逻辑分析仪的基本原理和应用

时错 误 时 , 用不 正 确 的工 具 将 会 耗 费 大量 时 间 。 用逻 辑 时 观 察 几条 甚 至 几百 条 信号 线 以验 证 信 号 间的 选 采

・

跳 变 采 样

弓 言 l

一

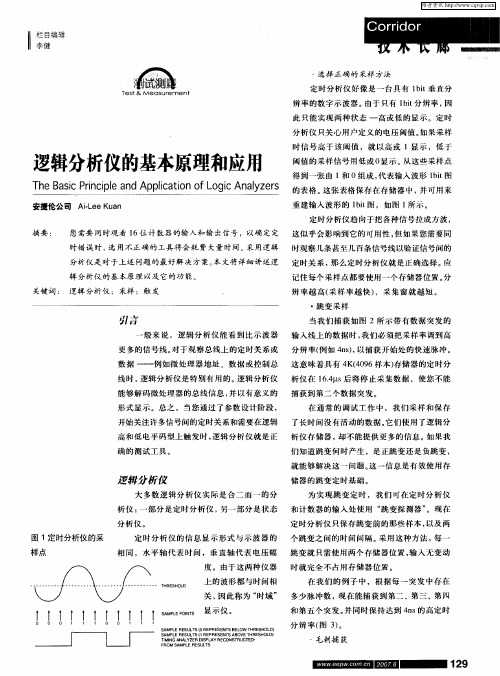

当 我 们 捕 获 如 图 2所 示 带 有 数 据 突发 的

般 来 说 ,逻 辑 分 析 仪 能 看 到 比 示 波 器 输 入 线 上 的 数 据 时 , 们 必 须 把 采 样 率 调 到 高 我

更 多 的 信 号 线 。 于观 察 总 线 上 的定 时 关 系或 分 辨 率 ( 如 4 s, 对 例 n ) 以捕 获 开 始 处 的快 速 脉 冲 。

度。由于这两种仪器 时 就 完 全 不 占用 存 储 器 位 置 。

上 的 波形 都 与 时 间 相 在 我 们 的例 子 中 ,根 据 每 一 突 发 中存 在 关 , 此 称 为 “ 域 ” 多 少 脉 冲 数 , 在 能 捕 获 到 第 二 、 三 、第 四 因 时 现 第

f f f f f f f f f f f

样 点

定 时 分 析 仪 的 信 息 显 示 形 式 与 示 波 器 的 个 跳 变 之 间 的 时 间 间 隔 。 用 这 种 方 法 , 采 每一

相 同 , 水 平 轴 代 表 时 间 ,垂 直 轴 代 表 电压 幅 跳 变 就 只 需 使 用 两个 存储 器 位 置 , 入无 变动 输

数 据 — — 例 如 微 处 理 器 地 址 数 据 或 控 制 分

线 时 , 辑 分 析 仪 是 特 别 有 用 的 。 辑 分析 仪 析仪 在 l . s 将 停 止 采 集 数 据 ,使 您 不 能 逻 逻 6# 后 4 能 够解 码 微 处 理 器 的 总线 信 息 , 以 有 意 义 的 捕获 到 第二 个 数 据 突 发 。 并

Acute逻辑分析仪 智能电表客户测试案例(SPI信号)

Acute逻辑分析仪 智能电表客户测试案例(SPI信号)客户是做智能电表中的,产品中处理芯片是MCU,涉及到MCU的SPI接口通信数据测试。

我们针对他们产品测试中体现出来的技术优势:1.逻辑分析仪的采样率,我们逻辑分析仪的采样率有200MHz,400MHz,800MHz,1.6MHz,2GHz,4GHz一共六个档位选择,可以灵活根据客户的被测信号速率来选择。

而他们现有使用的逻辑分析仪的采样率才100MHz。

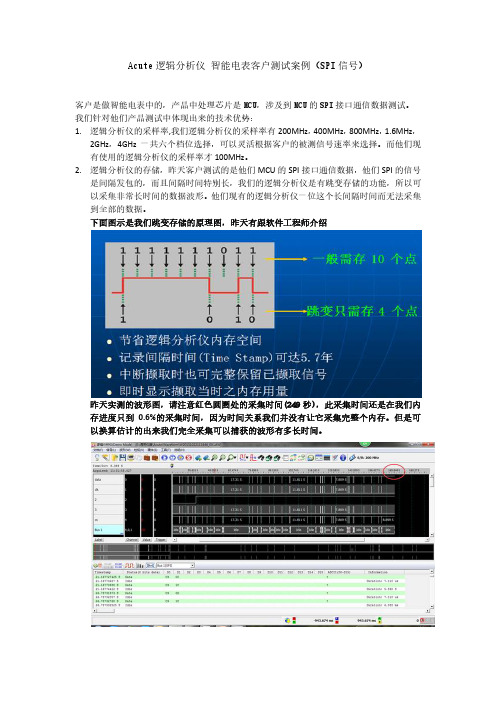

2.逻辑分析仪的存储,昨天客户测试的是他们MCU的SPI接口通信数据,他们SPI的信号是间隔发包的,而且间隔时间特别长,我们的逻辑分析仪是有跳变存储的功能,所以可以采集非常长时间的数据波形。

他们现有的逻辑分析仪一位这个长间隔时间而无法采集到全部的数据。

下面图示是我们跳变存储的原理图,昨天有跟软件工程师介绍昨天实测的波形图,请注意红色圆圈处的采集时间(249秒),此采集时间还是在我们内存进度只到0.6%的采集时间,因为时间关系我们并没有让它采集完整个内存。

但是可以换算估计的出来我们完全采集可以捕获的波形有多长时间。

3.我们逻辑分析仪的数据报告窗口有时间标记的功能,软件工程师说这个对他定位数据非常有帮助,而他目前使用的逻辑分析仪是没有此功能的。

以下图示红圈处就是我们数据报告窗口中的时间标记功能。

4.我们的逻辑分析仪可以在一个界面中查看协议数据,信号示波器波形,数字波形,那么我们可以在一个界面就完成协议分析,信号质量测试(phy),数字信号时序分析。

工程师昨天对我们这个工程师很感兴趣,认为很有用处。

下图中的data, 3两通道是SPI的两路数据,一路正常,一路异常,我们当时认为异常通道是否是未连接好。

然后我就用了我们的示波器堆叠功能,就可以清楚的看到异常通道的信号问题。

5.我们逻辑分析仪还有专门针对SPI的总线协议触发功能,可以精确定位数据,抓获工程师想要看的数据波形。

下图是我们SPI协议触发的设置界面,昨天测试设置0Dh捕获数据,然后触发捕获定位到满足0Dh数据的波形。

逻辑分析仪使用方法

逻辑分析仪使用方法逻辑分析仪是一种用于测试和分析电子设备中信号波形的仪器,它在电子工程领域中有着广泛的应用。

逻辑分析仪的使用方法对于工程师和技术人员来说至关重要,正确的使用方法可以帮助他们更准确地分析和解决问题。

下面将介绍逻辑分析仪的使用方法,希望能对大家有所帮助。

首先,使用逻辑分析仪之前需要对仪器本身有所了解。

逻辑分析仪通常包括输入端口、触发设置、采样率、存储深度等功能。

在开始使用之前,需要对这些功能有所了解,并且熟悉仪器的操作界面和按钮功能。

在连接逻辑分析仪之前,需要确保被测试的电子设备已经断电,并且对测试线进行正确的连接。

一般来说,逻辑分析仪会有多个输入通道,需要根据测试的需要选择合适的通道进行连接。

接下来是设置触发条件。

触发条件是指当输入信号满足一定的条件时,逻辑分析仪开始采集数据。

在设置触发条件时,需要根据被测试设备的信号特点来进行设置,以确保能够捕获到需要分析的信号波形。

采样率和存储深度也是需要注意的地方。

采样率决定了逻辑分析仪对信号波形的采样速度,而存储深度则决定了能够存储的波形数据量。

在进行设置时,需要根据被测试设备的信号特点来进行调整,以确保能够捕获到完整的波形数据。

在一切准备就绪后,可以开始对被测试设备进行电源供给,并进行数据采集。

在采集过程中,需要留意观察逻辑分析仪的显示屏,确保能够捕获到需要的信号波形。

最后,在数据采集完成后,需要对采集到的数据进行分析和处理。

逻辑分析仪通常会提供数据分析的功能,可以对采集到的波形数据进行放大、缩小、测量等操作,以便更好地分析和理解信号波形的特点。

总的来说,逻辑分析仪的使用方法并不复杂,但是需要对仪器本身有所了解,并且根据被测试设备的信号特点进行合理的设置和操作。

希望以上介绍能够对大家在使用逻辑分析仪时有所帮助。

逻辑分析仪使用方法

逻辑分析仪使用方法逻辑分析仪是一种用于测试和分析数字信号的仪器,广泛应用于电子、通信、计算机等领域。

它能够帮助工程师快速准确地分析数字电路中的信号,发现问题并进行调试。

下面将介绍逻辑分析仪的基本使用方法,希望能帮助您更好地使用这一工具。

首先,使用逻辑分析仪前,需要准备好相应的测试设备和接线。

确保待测电路处于断电状态,并按照逻辑分析仪的说明书,正确连接测试线和探头。

接线完成后,打开逻辑分析仪并设置相应的参数,如采样频率、触发方式等。

这些参数的设置需要根据具体的测试需求进行调整,以确保能够捕获到需要分析的信号。

接下来,进行信号采集和分析。

在逻辑分析仪上设置好参数后,可以开始进行信号的采集。

通过触发功能,可以使逻辑分析仪在特定条件下自动捕获信号,并将其显示在屏幕上。

在信号捕获后,可以通过逻辑分析仪提供的分析工具,如时序图、状态图等,对信号进行深入分析。

通过观察信号的波形和时序关系,可以快速定位问题,并进行故障排除。

最后,根据分析结果进行调试和优化。

通过逻辑分析仪的帮助,我们可以快速准确地找到问题所在,并进行相应的调试和优化。

在调试过程中,可以通过逻辑分析仪实时监测信号的变化,以便及时调整电路参数并验证效果。

通过不断的分析和调试,最终可以确保电路的稳定性和可靠性。

总之,逻辑分析仪作为一种重要的测试工具,在数字电路设计和调试过程中发挥着不可替代的作用。

正确的使用方法能够帮助工程师更快速地定位问题并进行调试,提高工作效率。

希望本文介绍的逻辑分析仪使用方法能够对您有所帮助,谢谢阅读!。

如何正确使用逻辑分析仪

如何正确使用逻辑分析仪逻辑分析仪(Logic Analyzer),是一种常见的电子设备,用于对数字电路进行信号分析和故障诊断。

逻辑分析仪可以帮助工程师准确分析数字信号,找出潜在问题,并帮助修复电路故障。

本文将介绍如何正确使用逻辑分析仪,以帮助读者更好地应用这一工具。

一、选择适合的逻辑分析仪在使用逻辑分析仪之前,首先需要选择适合自己需求的设备。

逻辑分析仪有不同的通道数和采样率等参数,请根据实际需要选择相应的型号。

此外,还要考虑逻辑分析仪的软件兼容性以及使用的便捷性等因素。

二、准备测试电路在使用逻辑分析仪进行测试之前,需要准备好测试电路。

确保电路的连接正确无误,并根据需要给被测电路供电。

三、连接逻辑分析仪将逻辑分析仪与被测电路进行连接。

通常情况下,逻辑分析仪需要与被测电路的信号引脚相连。

使用合适的连接线,将逻辑分析仪的信号线与被测电路连接起来,确保连接牢固可靠。

四、设置逻辑分析仪参数在连接逻辑分析仪后,需要根据测试需求设置合适的参数。

逻辑分析仪通常会提供相应的软件,可以通过软件进行参数设置和数据分析。

根据被测电路的特点和测试目的,设置逻辑分析仪的采样率、采样深度、触发条件等参数。

五、进行信号采样设置好参数后,可以开始进行信号采样。

逻辑分析仪会根据设置的参数进行数据采集,采集到的信号可以用于进一步的分析和诊断。

在信号采样过程中,需要确保采样的时间范围覆盖了所需分析的信号波形。

六、分析和诊断信号采样完成后,可以通过逻辑分析仪提供的软件对采集到的信号进行分析和诊断。

逻辑分析仪通常会提供波形分析、时序分析等功能,可以帮助工程师快速找出问题所在。

通过触发功能,可以将采样波形与特定条件进行比较,从而找出异常信号。

七、故障排除与修复通过分析和诊断,可以确定问题所在并进行相应的修复。

根据分析结果,工程师可以对电路进行调整、更换故障组件等操作,以修复电路故障。

八、记录和总结在使用逻辑分析仪进行测试和分析的过程中,需要及时记录测试结果和分析过程。

逻辑分析仪使用教程

声明: 本文来自分析仪开发手册.pdf)前言一、什么是逻辑分析仪二、使用介绍三、安装说明四、Saleae软件使用方法五、逻辑分析仪硬件安装六、使用Saleae分析电视红外遥控器通信协议七、使用Saleae分析UART通信八、使用Saleae分析IIC总线通信九、使用Saleae分析SPI总线通信十、Saleae逻辑分析仪使用问题和注意事项淘宝地址:(原文件名:21.jpg)前言:工欲善其事,必先利其器。

逻辑分析仪是电子行业不可或缺的工具。

但是由于一直以来,逻辑分析仪都属于高端产品,所以价格居高不下。

因此我们首先要感谢Cypress公司,提供给我们68013这么好的芯片,感谢俄罗斯毛子哥将这个Saleae逻辑分析仪开源出来,让我们用平民的价格,就可以得到贵族的待遇,获得一款性价比如此之高的逻辑分析仪,可以让我们在进行数字逻辑分析仪的时候,快速查找并且解决许多信号、时序等问题,进一步提高我们处理实际问题的能力。

原本计划,直接将Saleae的英文版本使用手册直接翻译过来提供给大家,我花费半天时间翻译完后,发现外国人写的东西不太符合我们国人的思维习惯,当然,也是由于我的英语水平有限,因此,我根据自己摸索这个Saleae的过程,写了一份个人认为符合中国人习惯的Saleae,提供给大家,希望大家在使用过程中少走弯路,快速掌握使用方法,更快的解决自己实际遇到的问题。

由于个人水平有限,因此在文章撰写的过程中难免存在问题和错误,如果有任何问题,希望大家能够提出来,我会虚心接受并且改进,希望通过我们的交流,给越来越多的人提供更加优秀的资料,共同进步。

一、什么是逻辑分析仪:逻辑分析仪是一种类似于示波器的波形测试设备,它通过采集指定的信号,并通过图形或者数据统计化的方式展示给开发人员,开发人员通过这些图形化时序信号按照协议来分析硬件或者软件中的错误。

逻辑分析仪是设计中不可缺少的设备,通过它,可以迅速定位错误,发现并解决问题,达到事半功倍的效果,尤其在分析时序,比如1wire、I2C、UART、SPI、CAN等数据的时候,应用逻辑分析仪解决问题非常快速。

逻辑分析仪讲座8-逻辑分析仪SPI插件触发应用

成都周立功

地址:成都市一环路南二段 1 号数码科技大厦 403 室 邮编: 610041 电话:(028) 85439836

85437446

武汉周立功

地址:武汉市洪山区广埠屯珞

瑜路 158 号 12128 室(华中电 脑数码市场) 邮编:430079 电话:(027) 87168397

87168497 87168297

联系方式:

广州致远电子有限公司 地址:广州市天河区车陂路黄洲工业区三栋二楼

销售电话: 020-22644372 020-28872453 020-22644249 销售邮箱: sales@

020-22644399

技术支持电话: 020-22644375 技术支持邮箱: support@ 技术支持论坛:

广州周立功单片机发展有 限公司

地址:广州市天河北路 689 号 光大银行大厦 12 楼 F4 邮编:510630 电话:(020) 38730972

38730916 38730917

38730976 38730977

深圳周立功

地址:深圳市深南中路 2070 号电子科技大厦 C 座 4 楼 D 室

邮编:518031 电话:(0755) 83783155 83781788(5 线)

关于测量与分析事业部

广州致远电子有限公司是集研发、生产、销售和服务于一体,产学研双结合的高新技术 企业。广州致远电子有限公司测量与分析事业部致力于测量测试仪器和开发工具设计与开 发。现拥有十大类,数十种产品。产品囊括数字示波器、逻辑分析仪、协议分析仪、数字万 用表、信号发生器、通用仿真器、通用编程器、数据采集板卡等。产品广泛应用于电子研发、 生产制造、工业控制、网络通信、科研院校和国防科技等领域。同时,广州致远电子有限公 司应邀参与数字示波器和逻辑分析仪国家标准的制定。测量与分析事业部的产品还得到了 TI、NXP、RENESAS、FUJITSU、WINBOND、INFINEON、LIMINARY、SUNPLUS、MYSON、SYNCMOS 等著名半导体公司的第三方认可。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

的要求 。在 图 2 中Ts 为W E RD信号 /

2 .接 口分析 比较 流行 的并行 总线扩展 模式有

对 地 址 总 线 的 建 立 时 间 ,地 址 总 线要

在 W / E RD信号激 活之前的Ts 间保 时

C }—— ——

-—

--・・-

-

-—--一

ItlB s ne u 模式 ̄ Moooa B s I t rl u 模式 , l

证 数据 的稳 定 ,不然 写 / 的地 址 不 读

— — — — — —

wE

} b

- RD— — —— —

LP 21 C2 4

略Pl S82

这两种最大的区别是Mo o o a t r l BU 能确定 。Th S 为数据 总线对W E RD / 信

如 图2 所示 。

(0 p 分 辨 率 ) ,完 成 可 以 满 足 建 立 20 s 时 间Ts[ 持 时 间T 的 测 量 。 fI 保 h

3 案例分享 .

口扩 展的方式 中 ,使 用并行数 据总线

与功能芯 片或 模块 进行通信是M CU/ CPU外 围功能扩展的过程 中最常用 的

致

W W W .

. s ’ e1 J 一 熏a.f ■ . 专栏 m电( bor eI o子 ; o e

逻 分 仪 — 入 到 通 座3 辑 析 — 从 门 精 讲 () 0

逻辑分析仪在芯片互联的应用

1引亩 . Bs u 典型的1 位接 I扩展如图1 6 : I 所示 。 储定时采样 最高采样达到 1 GHZ(nS i

尽管现在 的MCU/ห้องสมุดไป่ตู้U集成度 已 CP

经很 高 ,但在 数字 电路 系统开 发 中, 通常我们还会对MCU/C U的进行扩 P 展 ,如增 ̄ US \ H B 以太网\ D LC 驱动显 示接 口等 多种 方式 的扩展 。在 各种接

Itl u 的写入和读取操作 时序 分 辨 率 ) ,高速 定 时 采样 为 5 ne B s GHz

LA 7 0 逻辑 分析仪深 存 B 54

脚 ,设置采样 频率 为5 1 ,测量结果 GIz

44 今日电子 ・21年7 01 月

●卜

图3 P21与I 18的连接 Lc 24 s 2 P5

单独的信号线来表示读或者写。I t l 要保 持不变 ,不然会 引起数 据写入或 n e

读 取 出错 。随着现 代芯片 工艺的不 断

●--— — ——— ‘ -— - f — — —一

● - —---- V --- t --— 一

在使 用中 ,发 现读写不稳 定 ,具

体的表现 为在一些 板上没 有问题 ,在 另外的一 些板上会 出现 出错 现象 。使

●—— —-b— —— R ———一

改 进 ,建立 时 间Ts r i 保持 时 间Th变

MC U

从设鲁器件

■— B s10一 L【:】

得 越来 越小 ,建立 时 间Ts 基本在 2 ~

方式 。

在使 用并行总 线进行 芯片 阃的 通

图2 1位总线读写时序 6 MCU/ P C U要 正确的读 写外 围芯 片 ,其操 作时序 必须要满足 外 围芯片 信时需要 对时序 间的配合 进行确认 , 如果 双 方 的 时 序 配 合 不 上 时 ,会 产

生 读 写 出 错 的 问 题 。 在 N XP公 司 的 AR 7 片 L C 2 4 使 用 IP 5 2 M 芯 P 2 1上 S 1 8 进 行 US 接 口扩 展 ,如 图 3 示 。 B 所

1n 左右 ,而保持时 间Th 0s 最小的可以

做 到0 s n

。

用LAB 5 4 7 0 逻辑分析仪测量乙 2 1 PC 2 4

地址 总线 数 据 总 线 和 读 写 信 号 等 弓

A D [: ・- 一 D RnI -- ] —— ●I- _—O^ A :l T nso——-

图’ ’位数据总线连接 图 。

— — — —

_ D R 7 卜—— ^ O 【: O D T I :] —’ A A[S — 0

模式 使 用一根 信号 线 来表 示读 / 写信

号 , ̄I t l n e Bu 模式分 别使用两根 s

号保 持时 间 ,在W / 信 号激活撤 E RD

销 的Th 时间内 ,数据总 线DATA必须