半导体封装不良术语

半导体dfn封装的中文术语

半导体dfn封装的中文术语半导体dfn封装是电子行业中的一种封装技术,它被广泛应用于集成电路的制造过程中。

该封装技术能够有效地保护电子器件,提高其稳定性和可靠性。

下面我将从不同角度对半导体dfn封装进行描述。

一、半导体dfn封装的定义和特点半导体dfn封装是一种采用无引脚底部焊盘和封装材料对芯片进行封装的技术。

与传统的封装技术相比,dfn封装具有以下特点:1. 封装尺寸小:dfn封装可以实现芯片的高集成,尺寸更小,适用于电子设备的微型化和轻量化。

2. 低功耗:dfn封装的无引脚底部焊盘设计减少了电阻和电感,降低了功耗,提高了芯片的性能。

3. 优良的散热性能:dfn封装采用底部焊盘散热设计,能够更好地散热,提高芯片的工作稳定性。

4. 高可靠性:dfn封装采用无引脚设计,减少了焊接点,降低了故障率,提高了芯片的可靠性。

二、半导体dfn封装的应用领域半导体dfn封装广泛应用于电子设备的制造和通信领域。

具体包括:1. 手机和平板电脑:dfn封装的小尺寸和低功耗特性非常适合手机和平板电脑等移动设备的需求。

2. 无线通信设备:dfn封装的高可靠性和优良散热性能使其成为无线通信设备中关键部件的首选。

3. 汽车电子:dfn封装能够满足汽车电子产品对小尺寸、高可靠性和低功耗的要求。

4. 工业控制设备:dfn封装具有抗震、抗干扰等特点,适用于工业控制设备等恶劣环境下的应用。

三、半导体dfn封装的未来发展趋势随着电子技术的不断进步,半导体dfn封装也在不断发展。

未来,dfn封装有望实现以下发展趋势:1. 封装尺寸进一步缩小:随着芯片尺寸的减小和集成度的提高,dfn封装尺寸将进一步缩小,实现更高的集成性。

2. 更高的功耗效率:随着材料和工艺的进步,dfn封装将实现更低的功耗和更高的电子器件性能。

3. 更好的散热设计:随着散热技术的不断发展,dfn封装将实现更好的散热效果,提高芯片的工作稳定性。

4. 更广泛的应用领域:随着电子设备的普及和需求的增加,dfn封装将在更多领域得到应用,如物联网、人工智能等。

半导体专业术语

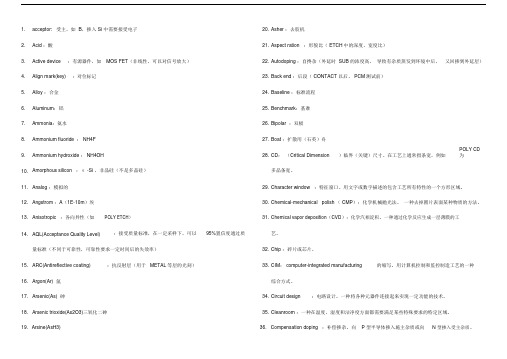

1.acceptance testing (WAT: wafer acceptance testing)2.acceptor: 受主,如B,掺入Si中需要接受电子3.Acid:酸4.Active device:有源器件,如MOS FET(非线性,可以对信号放大)5.Align mark(key):对位标记6.Alloy:合金7.Aluminum:铝8.Ammonia:氨水9.Ammonium fluoride:NH4F10.Ammonium hydroxide:NH4OH11.Amorphous silicon:α-Si,非晶硅(不是多晶硅)12.Analog:模拟的13.Angstrom:A(1E-10m)埃14.Anisotropic:各向异性(如POLY ETCH)15.AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)16.ARC(Antireflective coating):抗反射层(用于METAL等层的光刻)17.Argon(Ar)氩18.Arsenic(As)砷19.Arsenic trioxide(As2O3)三氧化二砷20.Arsine(AsH3)21.Asher:去胶机22.Aspect ration:形貌比(ETCH中的深度、宽度比)23.Autodoping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)24.Back end:后段(CONTACT以后、PCM测试前)25.Baseline:标准流程26.Benchmark:基准27.Bipolar:双极28.Boat:扩散用(石英)舟29.CD:(Critical Dimension)临界(关键)尺寸。

在工艺上通常指条宽,例如POLY CD 为多晶条宽。

30.Character window:特征窗口。

半导体专业术语.doc

1. acceptor: 受主,如 B,掺入 Si 中需要接受电子20. Asher :去胶机2. Acid :酸21. Aspect ration :形貌比( ETCH中的深度、宽度比)3. Active device :有源器件,如MOS FET(非线性,可以对信号放大)22. Autodoping :自搀杂(外延时 SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)4. Align mark(key) :对位标记23. Back end :后段( CONTACT以后、 PCM测试前)5. Alloy :合金24. Baseline :标准流程6. Aluminum:铝25. Benchmark:基准7. Ammonia:氨水26. Bipolar :双极8. Ammonium fluoride : NH4F 27. Boat :扩散用(石英)舟9. Ammonium hydroxide : NH4OH 28. CD:(Critical Dimension )临界(关键)尺寸。

在工艺上通常指条宽,例如POLY CD 为10. Amorphous silicon :α -Si ,非晶硅(不是多晶硅)多晶条宽。

11. Analog :模拟的29. Character window :特征窗口。

用文字或数字描述的包含工艺所有特性的一个方形区域。

12. Angstrom :A(1E-10m)埃30. Chemical-mechanical polish ( CMP):化学机械抛光法。

一种去掉圆片表面某种物质的方法。

13. Anisotropic :各向异性(如POLY ETCH)31. Chemical vapor deposition(CVD):化学汽相淀积。

一种通过化学反应生成一层薄膜的工14. AQL(Acceptance Quality Level) :接受质量标准,在一定采样下,可以95%置信度通过质艺。

半导体用语资料

半导体用语Siliconingot 硅锭Wafer晶片Mirror wafer 镜面晶圆Patter 晶圆片FAB: fabrication 制造Fabrication Facility 制造wafer生产工厂Probe test 探针测试Probe card 探针板Contact 连接Probe Tip 探头端部ChipFunction 功能EPM: Electrical Parameter MonitoringSummary 总结R&D:Research and Development 研究和开发MCP:Multi Chip Package 多芯片封装POP:Package on Packagee-MMC:embedded Multi Media card 嵌入式多媒体卡WLP:Wafer Level Package 晶圆级封装SDP 一层DDP 两层QDP 四层ODP 八层Pad outBack Grind 背研磨Wafer Grind Back Grind 磨片Overview 概述TPM:Total Profit Management SKTPM Operation 操作Erase 消除Key Para. :Key parameter 关键参数Cycling 写入次数、循环次数Retention 保留时间Non-Volatile memoryVolatile memoryRead 读Write 写Refresh 更新Speed 速度、速率、转速Restore 修复、恢复Electrical Signal 电信号WFBI:Wafer Burn-InPT1H:Probe Test 1 Hot TestPT1C:Probe Test 1 Cold TestL/Rep:Laser RepairPurpose 目的Substrate 基片Trend 趋势Small Size 小体积High Density 高集成High Speed 高速度Roadmap 路标TSOP:Thin small outline package 薄型小尺寸封装FBGA:(Fine Ball Grid Array)package 细间距球栅阵列(一种封装模式)Flip Chip Package:在wafer的chip上形成bump直接在substrate或PCB基板上填充形态,使I/O最高密度化的填充方式。

半导体专业术语

专业术语1 Active Area 主动区(工作区)主动晶体管(ACTIVE TR ANSISTOR)被制造的区域即所谓的主动区(ACTI VE AREA)。

在标准之MOS制造过程中ACTIVE AREA是由一层氮化硅光罩即等接氮化硅蚀刻之后的局部场区氧化所形成的,而由于利用到局部场氧化之步骤,所以ACTI VE AREA会受到鸟嘴(BIRD’S BEAK)之影响而比原先之氮化硅光罩所定义的区域来的小,以长0.6UM之场区氧化而言,大概会有0.5UM之BIRD’S BEAK 存在,也就是说ACTIVE AREA比原在之氮化硅光罩所定义的区域小0.5UM。

2 ACTONE 丙酮 1. 丙酮是有机溶剂的一种,分子式为CH3COCH3。

2. 性质为无色,具刺激性及薄荷臭味之液体。

3. 在FAB内之用途,主要在于黄光室内正光阻之清洗、擦拭。

4. 对神经中枢具中度麻醉性,对皮肤黏膜具轻微毒性,长期接触会引起皮肤炎,吸入过量之丙酮蒸汽会刺激鼻、眼结膜及咽喉黏膜,甚至引起头痛、恶心、呕吐、目眩、意识不明等。

5. 允许浓度1000PPM。

3 ADI 显影后检查 1.定义:After Developing Inspection 之缩写2.目的:检查黄光室制程;光阻覆盖→对准→曝光→显影。

发现缺点后,如覆盖不良、显影不良…等即予修改,以维护产品良率、品质。

3.方法:利用目检、显微镜为之。

4 AEI 蚀刻后检查 1. 定义:AEI即After Etching Inspection,在蚀刻制程光阻去除前及光阻去除后,分别对产品实施全检或抽样检查。

2.目的:2-1提高产品良率,避免不良品外流。

2-2达到品质的一致性和制程之重复性。

2-3显示制程能力之指针2-4阻止异常扩大,节省成本3.通常AEI检查出来之不良品,非必要时很少作修改,因为重去氧化层或重长氧化层可能造成组件特性改变可靠性变差、缺点密度增加,生产成本增高,以及良率降低之缺点。

半导体术语

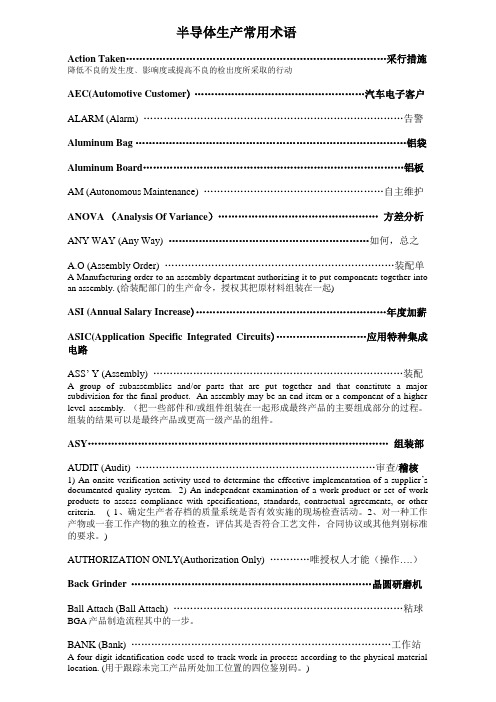

半导体生产常用术语Action Taken……………………………………………………………………采行措施降低不良的发生度﹑影响度或提高不良的检出度所采取的行动AEC(Automotive Customer)……………………………………………汽车电子客户ALARM (Alarm)……………………………………………………………………告警Aluminum Bag ………………………………………………………………………铝袋Aluminum Board……………………………………………………………………铝板AM (Autonomous Maintenance)………………………………………………自主维护ANOVA (Analysis Of Variance)…………………………………………方差分析ANY WAY (Any Way)……………………………………………………如何,总之A.O (Assembly Order)……………………………………………………………装配单A Manufacturing order to an assembly department authorizing it to put components together into an assembly. (给装配部门的生产命令,授权其把原材料组装在一起)ASI (Annual Salary Increase)…………………………………………………年度加薪ASIC(Application Specific Integrated Circuits)………………………应用特种集成电路ASS’ Y (Assembly)…………………………………………………………………装配A group of subassemblies and/or parts that are put together and that constitute a major subdivision for the final product. An assembly may be an end item or a component of a higher level assembly. (把一些部件和/或组件组装在一起形成最终产品的主要组成部分的过程。

英语-半导体用语

chip - 芯片。

崩角delamination - 分层reliability test - 可靠性试验risk assessment - 风险评估die - 芯片crack - 裂开kukumalu1001 at 2008-8-13 13:13:38PPAP - Production Part Approval Process -PA - Product Analysis - 产品分析Package- 封装体Isolated failure - 独立失效期间Laten Defect - 潜在失效缺陷田尼at 2008-8-26 21:24:56Million of Thanks for your sharing.田尼at 2008-8-26 21:34:571. 压焊图 bonding diagram2. 铝垫 bonding pad3. 打印规范marking instruction4. 塑封料 molding compound5. 导电胶 epoxyydh3256 at 2008-8-31 22:57:46谢谢大家分享好的东西538059 at 2008-9-09 22:09:57pcaking 包装washing 洗净conductuve mat 导电地板wrist lap 导电手腕带flux 助焊剂田尼at 2008-9-10 11:13:446. 单腔模具 single cavity mold7. 多腔模具 multi-cavity mold8. 浇口gate9. 顶针ejector pin10. 合模力clamping forcezf1722 at 2008-9-10 11:45:11QUOTE:原帖由田尼于2008-7-25 17:40 发表各位兄弟姐妹、叔叔阿姨们:我们在论坛里可不可以多一些封装测试专业方面的英语啊?每次看到的英语帖子都是些半导体以外的,我想我们论坛应该以半导体行业英语为主吧。

半导体材料术语1

半导体材料术语13.1 受主acceptor半导体中的⼀种杂质,她接受从价带激发的电⼦,形成空⽳导电。

3.2 电阻率允许偏差allowable resistivity tolerance晶⽚中⼼点或晶锭断⾯中⼼点的电阻率与标称电阻率的最⼤允许差值,它可以⽤标称值的百分数来表⽰。

3.3 厚度允许偏差allowable thickness tolerance晶⽚的中⼼点厚度与标称值的最⼤允许差值。

3.4 各向异性anisotropic在不同的结晶学⽅向有不同物理特性。

⼜称⾮各向同性,⾮均质性。

3.5 各向异性腐蚀anisotropic etch沿着特定的结晶学⽅向,呈现腐蚀速率增强的⼀种选择性腐蚀。

3.6 退⽕annealing改变硅⽚特性的热过程。

3.7 退⽕⽚annealing wafer在惰性⽓氛或减压⽓氛下由于⾼温的作⽤在近表⾯形成⼀个⽆缺陷(COP)区得硅⽚。

3.8 脊形崩边apex chip从晶⽚边缘脱落的任何⼩块材料的区域。

该区域⾄少含有2个清晰的内界⾯,⽽形成⼀条或多条清晰交叉线。

3.9 区域沾污area contamination在半导体晶⽚上,⾮有意地附加到晶⽚表⾯上的物质,它的线度远⼤于局部光散射体。

区域沾污可以是由吸盘印,⼿指或⼿套印迹、污迹、腊或溶剂残留物等形成的晶⽚表⾯外来物质。

3.10 区域缺陷area defect⽆标准定义,参看延伸的光散射体(3.28.6)3.11 氩⽓退⽕的硅⽚argon annealed wafer在氩⽓⽓氛下进⾏⾼温退⽕的硅⽚。

3.12 ⾃掺杂autodoping源⾃衬底的掺杂剂掺⼊到外延层中。

⾃掺杂源可来⾃衬底的背⾯、正⾯以及边缘、反应器中的其它衬⽚,基座或沉积系统的其它部分。

3.13 背封backseal在硅⽚背⾯覆盖⼀层⼆氧化硅或其它绝缘体得薄膜,以抑制硅⽚中主要掺杂剂向外扩散。

3.14 背⾯backside不推荐使⽤的术语。

3.15 背表⾯back surface半导体晶⽚的背表⾯,相对于在上⾯已经或将要制作半导体器件的暴露表⾯。

半导体封装键合工艺中常见缺陷识别和处理方法

半导体封装键合工艺中常见缺陷识别和处理方法南京信息职业技术学院李荣茂 2012-07-13##############2012-07-13######2#0#12-07-13########,摘要,本文叙述了键合工艺的概念、键合工艺设备的改进和其产生的各种缺陷的类别。

重点研究了键合工艺常见缺陷的类型和其产生的根本原因。

通过对各种缺陷类型的识别,探索其产生的根本原因并找出应对方法,从而增加其合格率。

,关键词,键合工艺缺陷处理方法1.引言 FORCE 大 POWER是比较适宜的 ;(3)断点靠我们需要调节参数,小近随着科技发展的日新月异,电子芯片的使用越来越渗透到各行各中间,通常问题已经不再参数上了,我们应当仔细观察设备平台,是否业,而封装技术也应运而生。

所谓封装技术是一种将集成电路用“”有异物例如一些小的残留碎片遗留在产品的底部造成损伤,如果确认绝缘是这样的情况,及时清理平台残留碎片即可。

的塑料或陶瓷材料打包的技术。

封装对于芯片来说不但必须也是至关 4.2 不规则焊球 Defective ball 重要的,它直接影响到了芯片的质量,而 WIRE BOND作为封装技术中的一个重要的步骤,其过程中产生的晶体缺陷也是不容忽视的。

2.WIRE BOND 键合工艺目前主要的芯片连接技术有三种,分别为引线键合,载带焊和倒装焊,其中前者占键合工艺的 80%以上,在 IC 制造也中得到广泛的应用。

引线键合是半导体封装制程的一站,自晶粒 (Die或 Chip)各电极上,以金线或铝线进行各式打线结合,再牵线至脚架(Lead Frame)的各内脚处续行打线以完成回路,这种两端打线的工作称为 WireB ond。

Wire bond 图 2 不规则焊球在芯片封装厂称为前工序,又叫做金属线键合是将 die 的 PAD飞线连如图 2 所示金线打在芯片上的球并非圆形且球与球的大小厚度还接到外部封装的 BALL 的工序。

不一样,表示同一粒芯片上的球是不规则的,一粒芯片大约有百来粒 3.键合工艺为什么会产生缺陷球,有可能只有一到两粒是产生这样异常的,可对质量的影响确是大打 3.1 键合工艺产生缺陷的原因折扣。

半导体与封装专业英语常用术语-义守大学

半導體與封裝專業英語常用術語徐祥禎義守大學機械與自動化工程學系【A】Å or Angstrom/埃:m,用來定義長度的一個單位。

其他常用單位與符號縮寫Active component/主動元件:可藉由輸入訊號來使系統作動的電子元件,如電晶體與二極體。

ATC(accelerated thermal cycling)/加速熱循環Alloy/合金:兩種或者兩種以上的元素混合,其中至少有一種為金屬元素。

Ambient/周圍環境:環繞於系統、配件或元件周圍之接觸環境。

Ambient Temperature/環繞溫度:測試接觸之環境氣體其平均溫度。

Analog circuits/類比電路:具有連續輸入與輸出間關係之電路。

ANSI(American National Standards Institute)/美國國家標準協會ASIC(application specific integrated circuit)/特殊用途積體電路AST(accelerated stress testing)/加速應力試驗【B】Batch Manufacturing/批量製造:以群組、大量的方式製造,完成的所有元件皆具有一致性。

Batch Processing/整批處理:當使用特定機具進行連續生產仍無法達到所需要的產品數量時,所使用的一種生產方法。

BEOL(back-end of line)/後段製程線路BGA(ball grid array)/球柵式陣列構裝:一種利用陣列式錫球做為電訊接點,使晶片裝置於基板上之表面構裝技術。

Burn in/預燒:一種加速元件老化之方式,通常是提高溫度、電壓,利用此試驗可使元件特性較穩定,並發現早期破壞之元件。

【C】C4(controlled collapse chip connection)/控制塌陷高度晶片連接:一種由液體焊料之表面張力控制接點連接高度,並支持晶片重量的覆晶式連接方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

半导体封装不良术语

半导体封装是指将硅片上的芯片封装在包裹材料中,以保护芯片并提供连接电路的技术。

在半导体封装过程中,可能会出现一些不良现象和术语。

下面是一些常见的半导体封装不良术语:

1.基材开裂:在封装过程中,基材(如硅片或基板)会发生开裂现象。

这可能是由于温度变化、机械应力或材料瑕疵等原因引起的。

基材开裂会导致封装失效和电性能下降。

2.焊点开裂:焊点是连接芯片和封装材料的重要部分。

如果焊点出现开裂现象,则会导致芯片与封装材料之间的连接不良,从而影响电性能和可靠性。

3.内应力:封装材料在固化过程中会产生一定的内应力。

如果内应力过大,则可能导致封装材料的开裂、位移或变形,从而影响封装质量和芯片性能。

4.气泡:在封装材料中产生的气泡可能会导致封装结构不密封。

气泡通常由残留的挥发性物质或有机杂质引起,会使封装材料的绝缘性能下降,从而对芯片的电性能和可靠性产生负面影响。

5.异物:在封装过程中,可能会有杂质或异物进入封装材料中。

这些异物可能来自环境、生产设备或操作人员,如灰尘、化学物质残

留或金属碎屑等。

异物会导致封装材料的绝缘性能下降,同时还可能

引起短路、失效和降低芯片可靠性。

6.未覆盖敏感区域:在封装过程中,有些芯片可能具有敏感区域,需要特殊处理,如保护盖或金属屏蔽层。

如果这些敏感区域未得到适

当的保护或覆盖,可能会引起电磁干扰、电气失效或硬件故障。

7.漏胶:封装材料在封装过程中可能会发生漏胶现象,即封装材

料未充分填充到封装结构内部,导致封装不完整或存在孔隙。

漏胶会

导致封装结构不牢固,可能引起失效、短路或电性能下降。

8.异常电气性能:封装过程中可能会出现异常的电气性能,如电

阻值过大、电容值不稳定或电感值异常等。

这些异常可能是由封装材

料的质量问题、设备故障或操作错误等原因引起的。

9.封装不良率:封装不良率是指封装过程中出现的不良产品数量

与总产量之比。

封装不良率高可能是由于生产设备的问题、操作人员

的技术水平不高或材料质量的问题等引起的。

以上是一些常见的半导体封装不良术语。

在实际生产中,这些术

语对于检测不良产品、改进封装工艺和提高产品质量都具有重要意义。

因此,解决和预防这些不良现象是半导体封装过程中必须要注意的问题。